1

Изобретение относится к вычислительной технике и может быть использовано антономно в быстродействующих вычислителях или в качестве функциональных расширителей в составе больших ЭВМ.

Целью изобретения является повышение точности вычислений за счет устранения методической ошибки путем использования дополнительного кода адреса и исключение выброса функции при нулевых значениях аргумента.

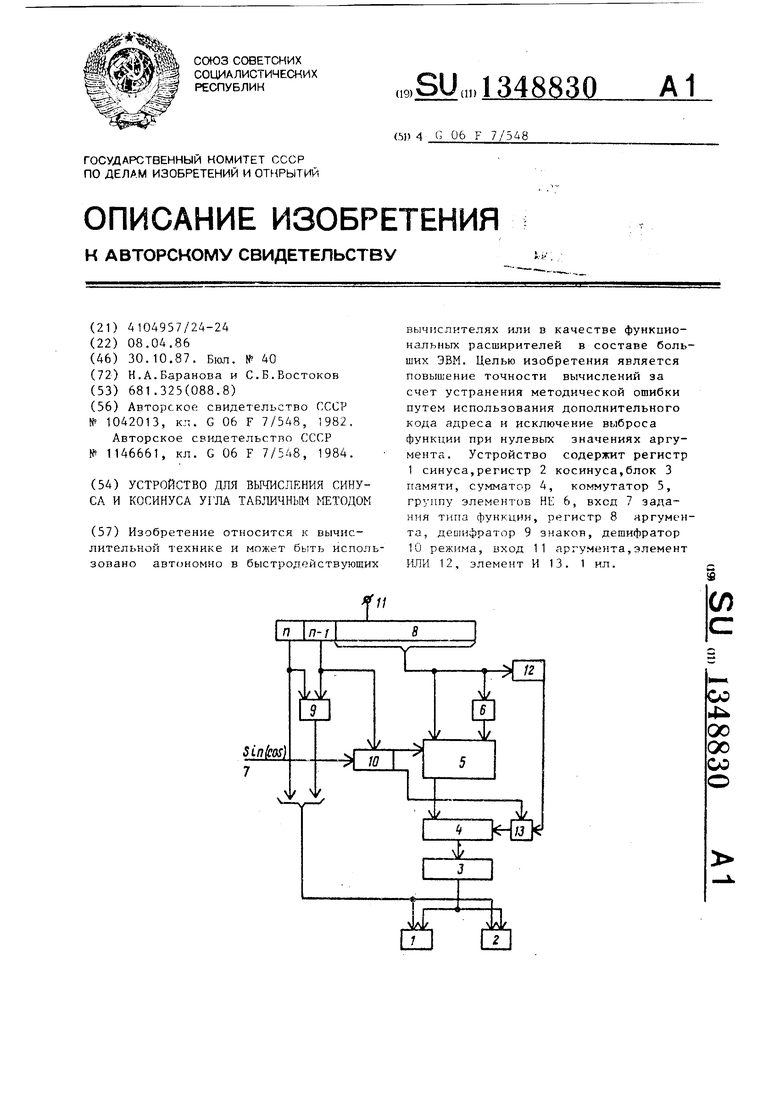

На чертеже представлена функциональная схема устройства.

Устройство содержит регистр 1 синуса, регистр 2 косинуса, блок 3 памяти, сумматор А, коммутатор 5,группу элементов НЕ 6, вход 7 задания типа функции,регистр 8 аргумента,дешифратор 9 знаков, дешифратор 10 режима, вход 11 аргумента, элемент ИЛИ 12, элемент И 13.

Устройство работает следу- ющим образом.

В блок 3 памяти записана таблица кодовых значений синуса,соответствующих функции первого квадранта.Интервал представления периода Т функции соответствует максимальному значению . п-разрядного кода аргумента (т 2 ). Аргумент поступает ч преобразователь , с п разрядов регистра 8 аргумента,в который аргумент записывается гго входу 11. С появлением на входе 7 сигнала о выборке одной функции из пары (sin х или cos х) для аргумента, находящегося в регистре 8 аргумента, дешифратор 10 режима разрешает прохождение аргумента iepe- коммутатор 5 либо в прямом, плбо р (:.бр;ггном коде.

Для значений аргумента в разрядах п и п-1 00 (Т квадрант) адрес функции sin X образуется через прямой код (ПК), а адрес функции cos х - через обратный код (ОК). Для значения аргумента в разрядах п и п-1 соответственно 01 (Л квадрант) адреса функции sin X образуется через ОК, адрес функции cos х - через ПК. Для значений аргумента в разрядах п и п-1 соотрр.тственно 10 (III квадрант) адрес функции sin х обра- jyeTCH через ПК, а адрес функции cos X - через СК. Для значений аргумента Б разрядах п и п-1 соответгм венно 11 (IV квадрант) здрес функ

488302

ции sin X образуется через ОК, а адрес функции cos X - через ПК.

В сумматоре А образуется адрес Р ячейки блока 3 постоянной памяти.

Если передача аргумента дешифратором 10 режима разрешается в ПК, на вход второго слагаемого сумматора 4 поступает величина аргумента

10 без изменений. Если передача аргумента дешифратором 10 режима разрешается в ОК, на вход второго слагаемого сумматора 4 поступает ОК младших разрядов аргумента.

15 Когда в п-2 младших разрядах аргумент в ПК содержит только нули, с группы элементов НЕ 7 на вход вто рого слагаемого поступают только единицы ,сигнал на входе первого слагае20 мого равен нулю. Адрес в этом случае образуется из всех единиц и соответствует точке таблицы. В противном случае к величине ОК добавляется единица в младший разряд.

5

Формула изобретения

Устройство для вычисления синуса и косинуса угла табличным методом содержащее регистр аргумента, регистр синуса, регистр косинуса, блок памяти, сумматор, коммутатор, группу элементов НЕ, дешифратор знаков и дешифратор режима, причем выходы (п-2)-х младших разрядов регистра аргумента

35, (п-разрядность аргумента) соединены с первым информационным входом коммутатора, второй информационный вход которого соединен с выходами элементов НЕ группы, входы которых соедине ны с выходами (п-2)-х младших разрядов регистра аргумента,выходы п-го и (n-l)-ro разрядов которого соединены соответственно с первым и вторым входами дешифратора знаков, выход которого и выход п-го разряда регистра аргумента соединены с входами старших знаковых разрядов соответственно регистров косинуса и синуса, информационные входы младших разрядов

которых соединены с выходом блока памяти, адресные входы которого соединены с выходом сумматора, управля- юш.ий вход коммутатора соединен с пер- ным выходом дешифратора режима, пер-.

5 Bbifi и второй входы которого соедине- i.bi соответственно с выходом (п-1)- го разряда регистра аргумента и иходом задан1 я типа функций устрой30

45

1348830

ства, отличающееся тем,соединен с первым входом элемента

что, с целью повышения точности вы-И, второй вход которого соединен с

числения, устройство дополнительновторым выходом дешифратора режима,

содержит элемент И и элемент ИЛИ,при-выход элемента И соединен с вхочем выходы (п-2)-х младших разрядовдом первого слагаемого сумматора,

регистра аргумента соединены с вхо-вход второго слагаемого которого

цами элемента ИЛИ, выход которогосоединен с выходом коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Устройство для вычисления функций синуса и косинуса | 1985 |

|

SU1272331A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1388855A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Устройство для вычисления функций SIN х и coS х | 1981 |

|

SU974371A1 |

| Цифровой генератор гармонических функций | 1981 |

|

SU1001069A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1164686A1 |

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Цифровой генератор гармоническихфуНКций | 1979 |

|

SU840858A1 |

Изобретение относится к вычислительной технике и может быть использовано автономно в быстродействующих вычислителях или в качестве функциональных расширителей в составе больших ЭВМ. Целью изобретения является повышение точности вычислений за счет устранения методической ошибки путем использования дополнительного кода адреса и исключение выброса функции при нулевых значениях аргумента. Устройство содержит регистр 1 синуса,регистр 2 косинуса,блок 3 памяти, сумматор 4, коммутатор 5, группу элементов НЕ 6, вход 7 задания типа функции, регистр 8 аргумента, деп1ифратор 9 знаков, дешифратор 10 режима, вход 11 аргумента,элемент ИЛИ 12. элемент И 13. 1 ил. Т // (Л UJ Ш

| Синусно-косинусный преобразователь | 1981 |

|

SU1042013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское CBi-щетельство СССР № 1146661, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-04-08—Подача