Изобретение относится к запоминающим устройствам. Известное устройство для контроля памяти, содержащее счетчик адресов, подключенный к блоку формирования адресов, блоку сравнения адресов и блоку анализа, коммутатор, соединенный с блоком формирования чисел, счетчик циклов, подключенный к блокам сравнения адресов и циклов, счетчик адресных операций, дешифратор, блок сравнения количества циклов, амплитудновременной дискриминатор, програмный блок и блок управления | 1. Данное устройство производит тес-« товый контроль взсшмосвязей между адресными ячейками и между разрядами блоков памяти. При этом устройство позволяет проверить блоки памяти дина мическими тестами бегающая 1 или О, шахматный порядок и первмен-г ное циклирование. Недостатками этого устройства являются сложность и большие аппаратные затраты. Наиболее близким к предлагаемому по технической сущности является устройство для контроля оперативной памяти, содержащее первый счетчик, регистр числа и блок управления, подклю ченные к выходным шинам устройства, основные коммутаторы, выходы которых соединены с входами регистра числа, второй и третий счетчики, формирователь, счетный триггер, полусумматор, дополнительный коммутатор и элемент ИС2. Это устройство формирует контролирующий тест типа дождь и ресный код. Недостатком данного устройства является невысокое быстродействие . Например, для проверки полного объема памяти .512 к байт машины ЕС-1022 с помощью этого устройства требуется несколько . Время проверки растет пропорционально квадрату числа адресов памяти. Для производственного , Контроля, когда необходимо быстро выловить все недостающие и лишние связк, неизбежные на этапе изготовления, такое устройство не может устраивать пО произ водитель ности. Цель изобретения - повыиение %icrrродействия и упрощение устройства. Поставленная цель достигается тем, в устрой«;тво для контроля памяти содержащее адресный счетчик, блок местного управления, коммутаторы и схему сравнения, одни из входов которой соединены с выходами коммутаторов.

другие являются одними из входов стройства, выходами которого являются выходы KON iyxaTopoB, одни из выхоов .счетчика и первый выход блока естного управления, второй и третий выходы которого подключены соответственно к управляющим входам адресного счетчика и коммутаторов, а входы блока естного управления соединены с одним

из выходов схемы сравнения и другим

выходом адресного счетчика, введен JO блок постоянной памяти, вход которого соединен с четвертым нлходом блока местного управления, а выходы подключены к одним из входов коммутаторов, ругие входы которых соединены соответ -15 ственно с одними из выходов адресного счетчика и другими выходами схемы сравнения, а также тем, что блок местного управления содержит генератор импульсов, триггеры, распределитель 20 импульсов и синхронизаторы, выходы которых являются выходами блока, причем выходы триггеров подключены к одним из входов синхронизаторов и распределителя импульсов, другой вход ко- 25 торого соединен с выходом генератора импульсов, одни из входов триггеров и другой вход первого синхронизатора объединены и являются первым входом блока, другие входы второго и третье- эд го синхронизаторов подключены к выходу распределителя импульсов, другие входы триггеров и четвертого синхронизатора, объединены и являются вторым входом блока. ,с

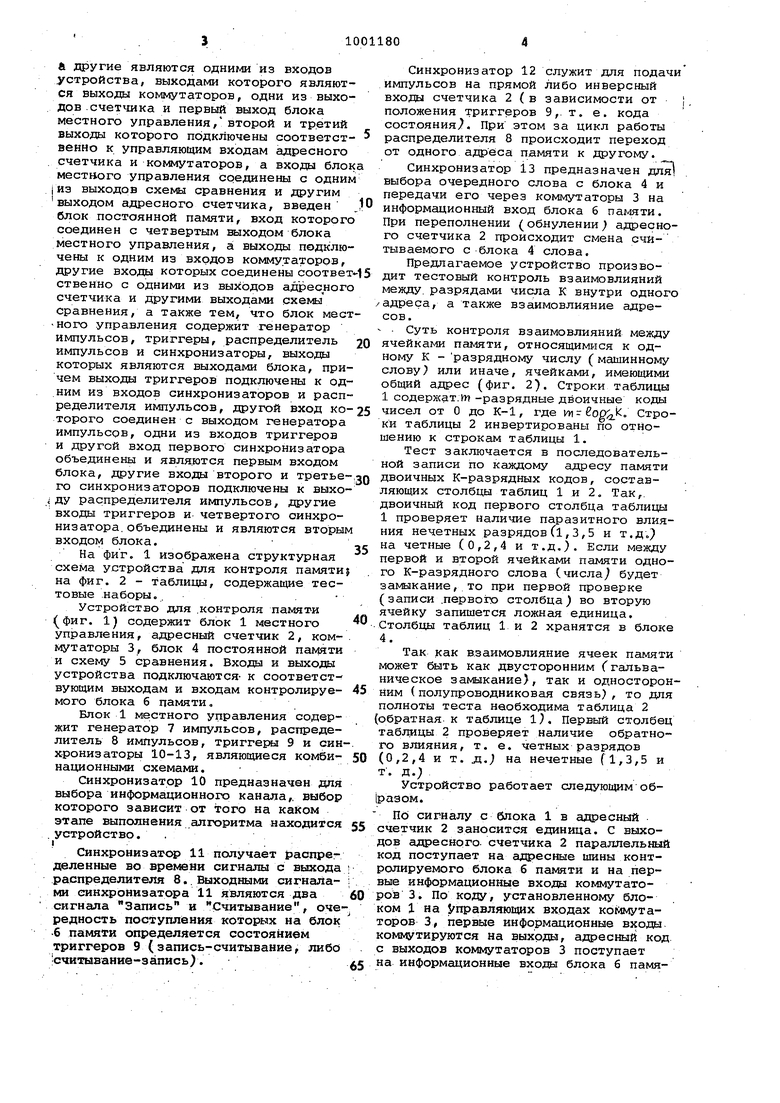

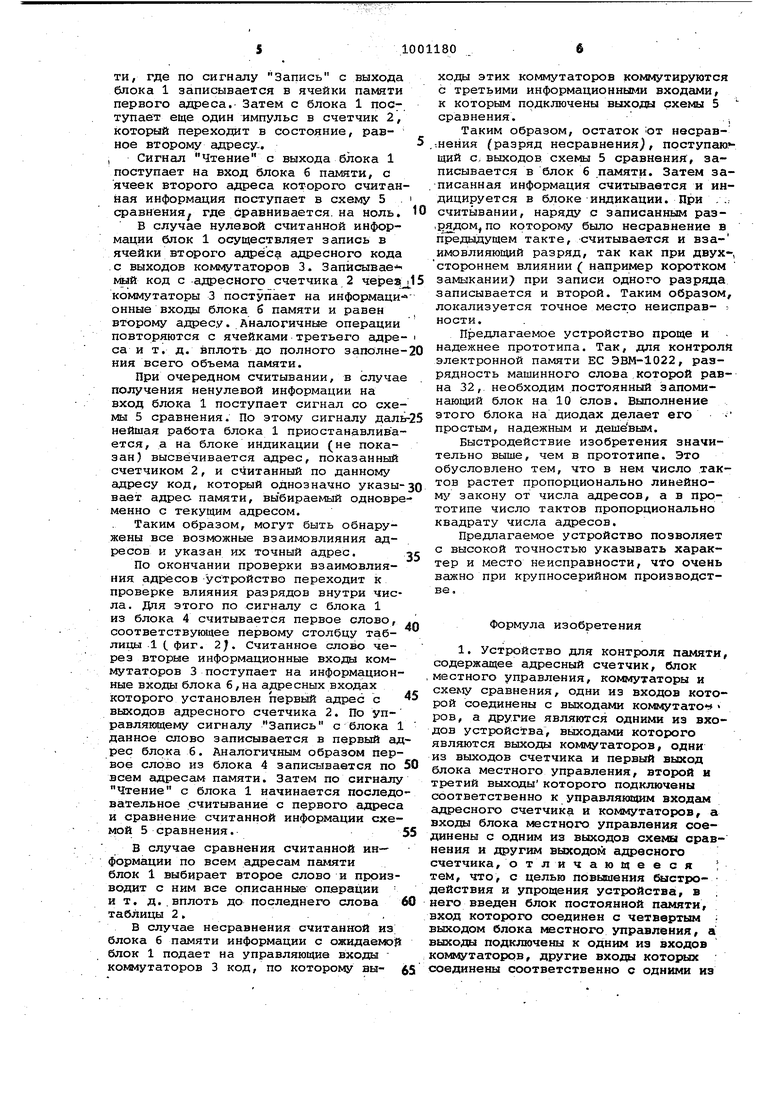

На фиг. 1 изображена структурная схема устройства для контроля памяти на фиг. 2 - таблицы, содержащие тестовые .наборы...

Устройство для .контроля памяти (фиг. 1) содержит блок 1 местного управления, адресный счетчик 2, ком- . мутаторы 3, блок 4 постоянной памяти и схему 5 сравнения. Входы и выходы устройства подключаются- к соответст вующим выходам и входам контролируе- 45 мого блока б памяти.

Блок 1 местного управления содержит генератор 7 импульсов, распределитель 8 импульсов, триггеры 9 и син-. хронизаторы 10-13, являющиеся комби- 50 национными схемами.

Синхронизатор 10 предназначен для выбора информационного канала,, выбор которого зависит от того на каком этапе выполнения алгоритма находится jS устройство. .

Синхронизат ф 11 получает распределенные во времени сигналы с выхода; распределителя 8.. Выходными сигнала- ; ми синхронизатора 11 являются два 60 сигнала Запись и Считывание, очередность поступления которых на блок б памяти определяется состоянием триггеров 9 (запись-считывание, либо считывание-запись).

Синхронизатор 12 служит для подачи импульсов на прямой либо инверсный входы счетчика 2 (в зависимости от |. положения триггеров 9, т. е. кода сост.ояния/. При этом за цикл работы распределителя 8 происходит переход

от одного памяти к другому.

....... -

Синхронизатор 13 предназначен для выбора очередного слова с блока 4 и передачи его через коммутаторы 3 на информационный вход блока 6 памяти. При переполнении (обнулении; адресного счетчика 2 происходит смена считываемого с блока 4 слова.

Предлагаемое устройство производит тестовый контроль взаимовлияний ежду, разрядами числа К внутри одного адреса, а также взаимовлияние адресов.

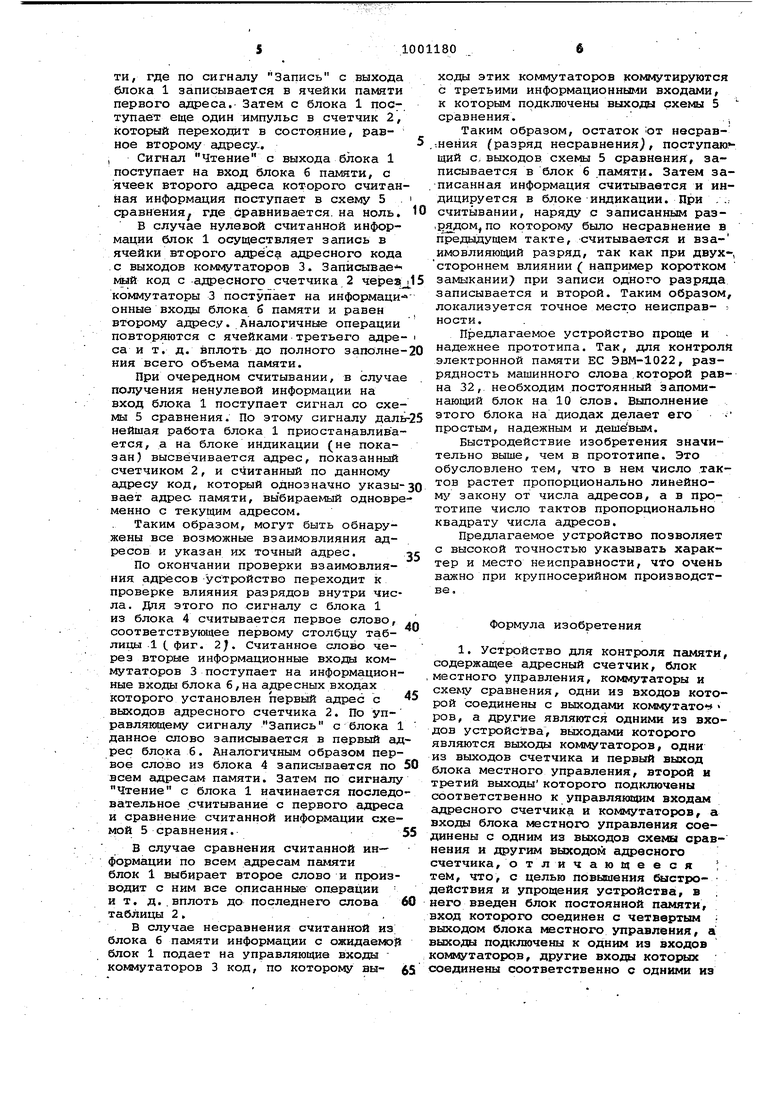

Суть контроля взаимовлияний между ячeйкa /IИ памяти, относящимися к одному К - разрядному числу ( машинному слову) или иначе, ячейками, имеющими общий адрес (фиг. 2). Строки таблицы 1 содержат.т -разрядные двоичные коды чисел от О до К-1, где Строки таблицы 2 инвертированы по отноению к строкам таблицы 1.

Тест заключается в последовательной записи по каждому адресу памяти двоичных К-разрядных кодов, составяющих столбцы таблиц 1 и 2. Так,, двоичный код первого столбца таблицы 1 проверяет наличие паразитного влияния нечетных разрядов (1,3,5 и т.д.) на четные (0,2,4 и т.д.). Если между первой и второй ячейками памяти одного К-разрядного слова (числа) будет замыкание, то при первой проверке (записи .первото столбца) во вторую ячейку запишется ложная единица. Столбцы таблиц 1 и 2 хранятся в блоке 4.

Так как в.заимовлияние ячеек памяти может быть как двусторонним Г гальваническое замыкание), так и односторонним (полупроводниковая связь), то для полноты теста необходима таблица 2 обратная к таблице 1). Первый столбец табгащы 2 проверяет наличие обратного влияния, т. е. четных разрядов (0,2,4 и т. д.) на нечетные (1,3,5 и

т. Д.) . :

Устройство работает следующим образом.

По сигналу с блока 1 в адресный счетчик 2 заносится единица. С выходов адресного, счетчика 2 параллельный код поступает на адресные шины контролируемого блока б памяти и на первые информационные входы коммутаторов 3. По КОДУ, установленному блоком 1 на Управляющих входах коммутаторов 3, первые информационные входы, коммутируются на выходы, адресный код. с выходов коммутаторов 3 поступает на информационные входы блока б памяти, где по сигналу Запись с выхода блока 1 записывается в ячейки памяти первого адреса.- Затем с блока 1 поступает еще один импульс в счетчик 2, который переходит в состояние, равное второму адресу-.5 I Сигнал Чтение с выхода блока 1 поступает на вход блока 6 памяти, с ячеек второго адреса которого считанная информация поступает в схему 5 qpaвнeния где сравнивается, на ноль. Ю

В случае нулевой считанной информации блок 1 осуществляет запись в ячейки второго адресу адресного кода .с выходов коммутаторов 3. Запйсывае шлК код с адресного счетчика 2 4epes. коммутаторы 3 поступает на информаци онные входы блока б памяти и равен второму адресу. Аналогичные операции повторяются с ячейками третьего адре- i са и т. д, вплоть до полного заполне-20 ния всего объема памяти.

При очередном считывании, в случае получения ненулевой информации на вход блока 1 поступает сигнал со схемы 5 сравнения. По этому сигналу даль-25 нейшая работа блока 1 приостанавливается, а на блоке индикации (не показан) высвечивается адрес, показанный счетчиком 2, и считанный по данному адресу код, который однозначно указы-ЗО вает адрес, памяти, выбираемый одновременно с текущим адресом.

Таким образом, могут быть обнаружены все во31 эжные взаимовлияния адресов и указан их точный адрес. js

По окончании проверки взаимовлияния адресов устройство переходит к проверке влияния разрядов внутри числа. Для этого по сигналу с блока 1 из блока 4 считывается первое слово, .. соответствунвдее первому столбцу таблицы 1 ( фиг. 2|. Считанное слово через вторые информационные входы коммутаторов 3 поступает на информационные входы блока б, на адресных входах которого установлен первый адрес с выходов адресного счетчика 2. По управляющему сигналу Запись с блока 1 данное слово записывается в первый адрес блока б. Аналогичным образом первое слово из блока 4 записывается по 50 всем адресам памяти. Затем по сигналу Чтение с блока 1 начинается последовательное считывание с первого адреса и сравнение считанной информации схемой 5 сравнения.55

В случае сравнения считанной информации по всем адресам памяти блок 1 выбирает второе слово и производит с ним все описанные операции и т. д..вплоть до последнего слова 6Q таблицы 2,. .

В случае несравнения считанной из; блока 6 памяти информации с ожидаемо блок 1 подает на управляющие входы коммутаторов 3 код, по которому вы- (J5

ходы этих коммутаторов коммутируются с третьими информационными входами, к которым подключены выходы схемы 5 сравнения.

Таким образом, остаток от нвсравтнения (разряд несравнения), поступаю.щий с. выходов схемы 5 сравнения, записывается в блок 6 памяти. Затем записанная информация считывается и индицируется в блоке индикации. При ... считывании, наряду с записанным раз,рядом,по которому было несравнение в предыдущем такте, считывается и взаимовлияющий разряд, так как при двухстороннем влиянии ( например коротком замыкании при записи одного разряда записывается и второй. Таким образом, локализуется точное место неисправ- : ности.

П эедлагаемое устройство проще и надежнее прототипа. Так, для контроля электронной памяти ЕС ЭВМ-1022, разрядность машинного слова которой равна 32, необходим постоянный запоминающий блок на 10 слов. Выполнение этого блока на диодах делает его простым, надежным и дешевым.

Быстродействие изобретения значительно выше, чем в прототипе. Это обусловлено тем, что в нем число тактов растет пропорционально линейному закону от числа адресов, а в прототипе число тактов пропорционально квадрату числа адресов.

Предлагаемое устройство позволяет с высокой точностью указывать характер и место неисправности, что очень важно при крупносерийном производстве.

Формула изобретения

1. Устройство для контроля памяти содержащее адресный счетчик, блок местного управления, коммутаторы и схему сравнения, одни из входов которой соединены с выходами коммутато ров, а другие являются одними из входов устройства, выходами которого являются выходы коммутаторов, одни из выходов счетчика и первый выход блока местного управления, второй и третий выходы которого подключены соответственно к управляющим входам адресного счетчика и коммутаторов, а входы блока местного управления соединены с одним из выходов схемы сравнения и другим выходом адресного счетчика, отличающееся ; тем, что, с целью повышения быстро- действия и упрощения устройства, в ; него введен блок постоянной памяти, вход которого соединен с четвертым ; выходом блока местного управления, а выходы подключены к одним из входов коммутаторов, другие вхо; которых соединены соответственно с одними из

выходов адресного счетчика и другими , выходами схемы сравнения.

2. Устройство по п. 1, о т л и чающееся тем, что блок местного управления содержит генератор импульсов, триггеры, распределитель импульсов и синхронизаторы, выходы которых являются выходами блока, причем 4выходы триггеров подключены к одним из входов синхронизаторов и распределителя импульсов, другой вход которого соединен с выходом генератора импульсов, одни из входов триггеров и другой вход первого синхронизатора объединены и являются первым входом блока, другие входы второго и третьего синхронизаторов подключены к выходу распределителя импульсов, другие входы триггеров и четвертого синхронизатора объединены и являются вторым входом блока.

Источники информации, принятые во внимание, при экспертизе

1.Авторское свидетельство СССР № 526964, кл. G 11 С 29/00,1974.

2.Авторское свидетельство СССР -№ 547837,кл. G 11 С ,29/00,1975(прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Процессор для идентификации и адресования событий | 1983 |

|

SU1188748A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Система коммутации | 1989 |

|

SU1667095A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1285470A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Tofjfm O f

Авторы

Даты

1983-02-28—Публикация

1981-03-11—Подача