11

Изобретение относится к вычислительной технике и может быть использовано в синхронизаторах, электронных коммутаторах и устройствах обработки информации.

Цель изобретения - увеличение быстродействия.

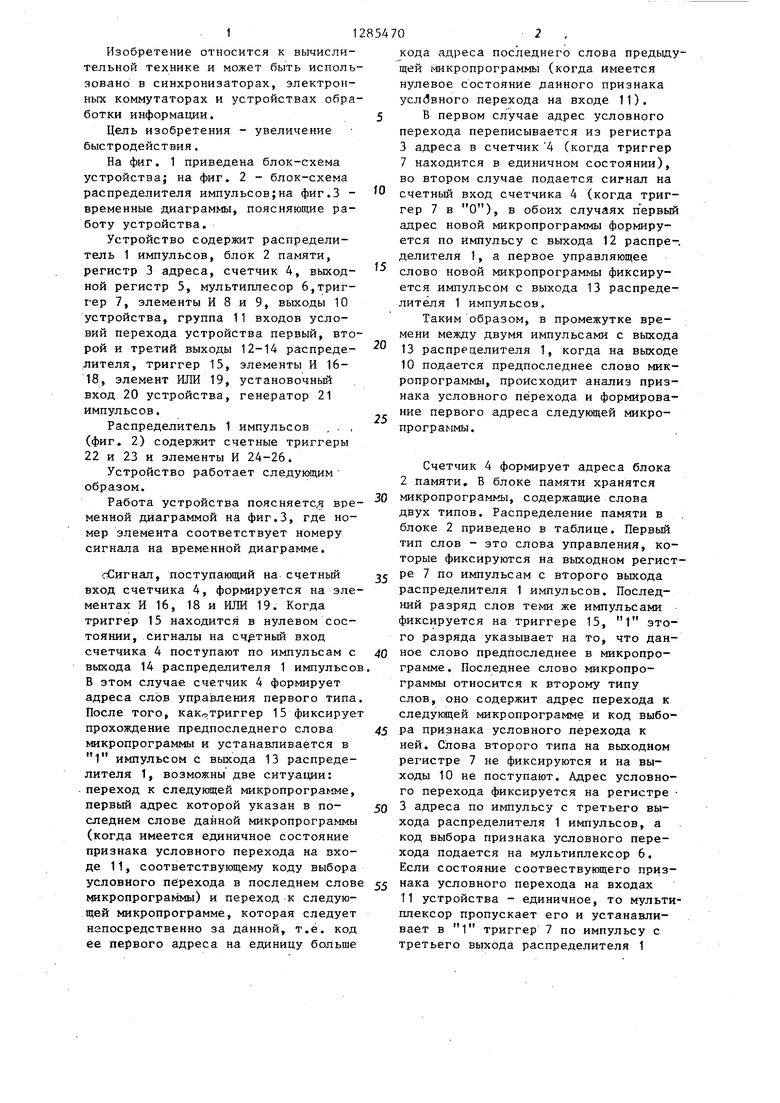

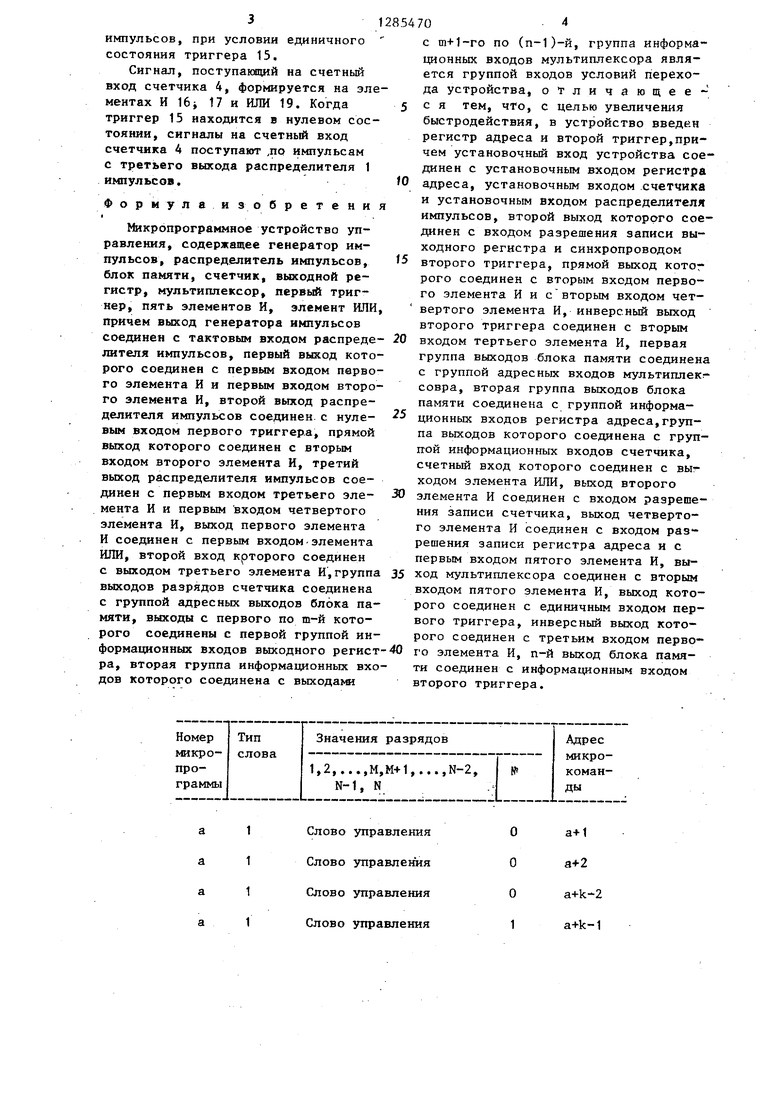

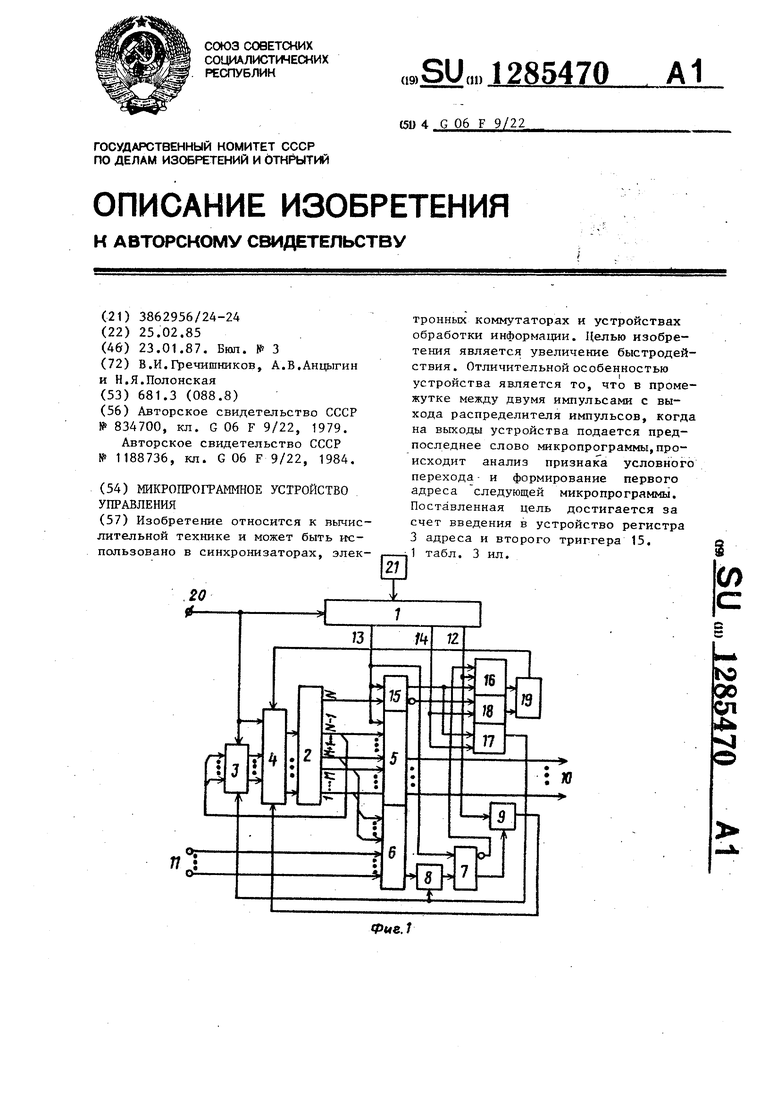

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема распределителя импульсов;на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство содержит распределитель 1 импульсов, блок 2 памяти.

регистр 3 адреса, счетчик 4, выходной регистр 5, мультиплесор 6,триггер 7, элементы И 8 и 9, выходы 10 устройства, группа 11 входов условий перехода устройства первый, второй и третий выходы 12-14 распределителя, триггер 15, элементы И 16- 18, элемент ИЛИ 19, установочньй вход 20 устройства, генератор 21 импульсов.

Распределитель 1 импульсов . . , (фиг. 2) содержит счетные триггеры 22 и 23 и элементы И 24-26.

Устройство работает следующим образом.

Работа устройства поясняете временной диаграммой на фиг.З, где номер элемента соответствует номеру сигнала на временной диаграмме.

сСигнал, поступающий на счетный вход счетчика 4, формируется на элементах И 16, 18 и ИЛИ 19. Когда триггер 15 находится в нулевом состоянии, сигналы на счетный вход счетчика 4 поступают по импульсам с выхода 14 распределителя 1 импульсо В этом случае счетчик 4 формирует адреса слов управления первого типа После того, какотриггер 15 фиксируе прохождение предпоследнего слова микропрограммы и устанавливается в 1 импульсом с выхода 13 распределителя 1, возможны две ситуации: . переход к следующей микропрограмме, первый адрес которой указан в последнем слове данной микропрограммы (когда имеется единичное состояние признака условного перехода на входе 11, соответствующему коду выбора условного перехода в последнем слов микропрограммы) и переход к следующей микропрограмме, которая следует непосредственно за данной, т.е. код ее пе(вого адреса на единицу больше

5

0

5

0

5

0

5

0

5

кода адреса последнего слова предьщу- щей микропрограммы (когда имеется нулевое состояние данного признака услбвного перехода на входе 11).

В первом случае адрес условного перехода переписывается из регистра 3 адреса в счетчик 4 (когда триггер 7 находится в единичном состоянии), во втором случае подается сигнал на счетный вход счетчика 4 (когда триггер 7 в О), в обоих случаях п ервый адрес новой микропрограммы формируется по импульсу с выхода 12 распре-. делителя 1, а первое управляющее слово новой микропрограммы фиксируется импульсом с выхода 13 распределителя 1 импульсов.

Таким образом, в промежутке времени между двумя импульсами с выхода 13 распределителя 1, когда на выходе

10подается предпоследнее слово микропрограммы, происходит анализ признака условного перехода и формирование первого адреса следующей микро- пpoгpa iмы.

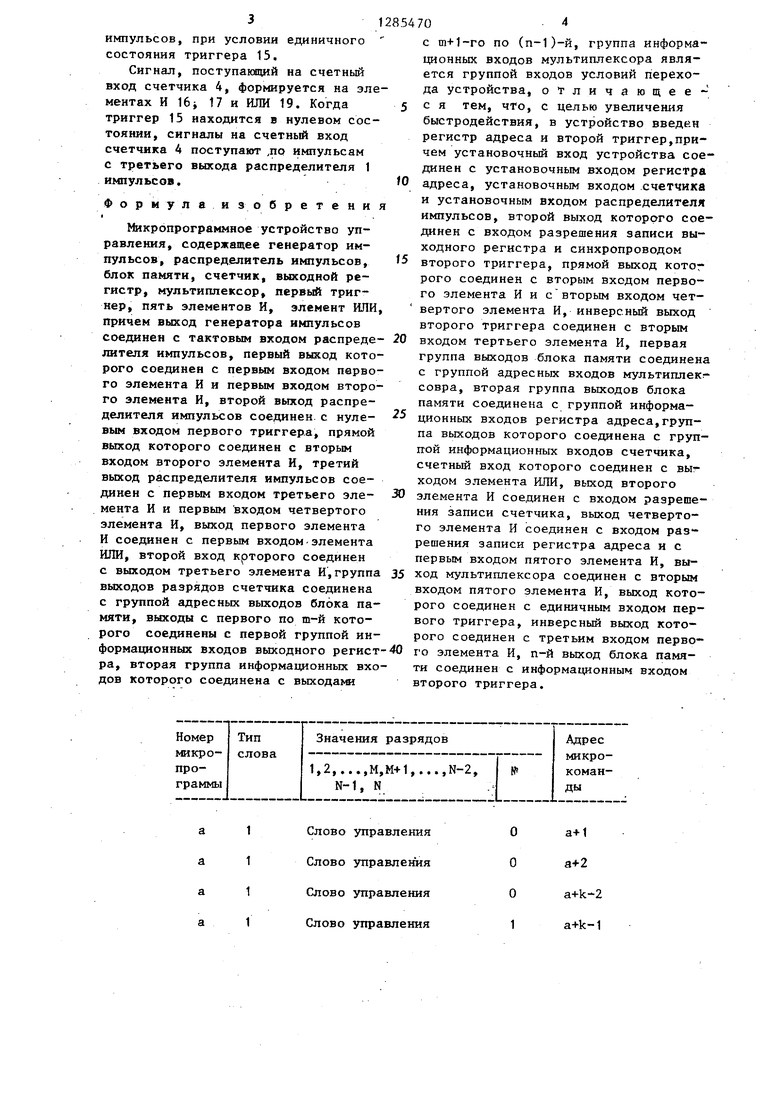

Счетчик 4 формирует адреса блока

2памяти, В блоке памяти хранятся микропрограммы, содержащие слова двух типов. Распределение памяти в блоке 2 приведено в таблице. Первый тип слов - это слова управления, которые фиксируются на выходном регистре 7 по импульсам с второго выхода распределителя 1 импульсов. Последний разряд слов теми же импульсами фиксируется на триггере 15, 1 этого разряда указывает на то, что данное слово предпоследнее в микропрограмме. Последнее слово микропрограммы относится к второму типу слов, оно содержит адрес перехода к следующей микропрограмме и код выбора признака условного перехода к ней. Слова второго типа на выходном регистре 7 не фиксируются и на выходы 10 не поступают. Адрес условного перехода фиксируется на регистре

3адреса по импульсу с третьего выхода распределителя 1 импульсов, а код выбора признака условного перехода Подается на мультиплексор 6. Если состояние соотвествующего признака условного перехода на входах

11устройства - единичное, то мультиплексор пропускает его и устанавливает в 1 триггер 7 по импульсу с третьего выхода распределителя 1

импульсов, при условии единичного состояния триггера 15.

Сигнал, поступанядий на счетный вход счетчика 4, формируется на элементах И 16i 17 и ИЛИ 19. Когда триггер 15 находится в нулевом состоянии, сигналы на счетный вход счетчика 4 поступают ,по импульсам с третьего выхода распределителя 1 импульсов.

Форм у лай 3 обретения

Микропрограммное устройство управления, содержащее генератор импульсов, распределитель импульсов, блок памяти, счетчик, выходной регистр, мультиплексор, первый триг- нер, пять элементов И, элемент ИЛИ, причем выход генератора импульсов соединен с тактовым входом распреде- лителя импульсов, первый выход которого соединен с первым входом первого элемента И и первым входом второго элемента И, второй выход распределителя импульсов соединен с нулевым входом первого триггера, прямой выход которого соединен с вторым входом второго элемента И, третий выход распределителя импульсов соединен с первым входом третьего элемента И и первым входом четвертого элемента И, выход первого элемента И соединен с первым входомэлемента ИЛИ, второй вход крторого соединен с выходом третьего элемента И,группа выходов разрядов счетчика соединена с группой адресных выходов блока памяти, выходы с первого по т-й которого соединены с первой группой информационных входов выходного регист ра, вторая группа информационных входов которого соединена с выxoдa в

а1Слово управления

а1Слово управлегшя

а1Слово управления

а1Слово управлеиия

28.54

я

fO

f5

25

, - 20 35-40X

704

с m+1-ro по (п-1)-й, группа информационных входов мультиплексора является группой входов условий перехода устройства, отличающее- с я тем, что, с целью увеличения быстродействия, в устройство введен регистр адреса и второй триггер,причем установочный вход устройства соединен с установочным входом регистра адреса, установочным входом .счетчика и установочным входом распределителя импульсов, второй выход которого соединен с входом разрешения записи выходного регистра и синхропроводом второго триггера, прямой выход котог рого соединен с вторым входом первого элемента И и с вторым входом четвертого элемента И, инверсный выход второго триггера соединен с вторым входом тертьего элемента И, первая группа выходов блока памяти соединена с группой адресных входов мультиплек:- совра, вторая группа выходов блока памяти соединена с группой информационных входов регистра адреса,группа выходов которого соединена с группой информационных входов счетчика, счетный вход которого соединен с выходом элемента ИЛИ, выход второго элемента И соединен с входом разрешения записи счетчика, выход четвертого элемента И соединен с входом решения записи регистра адреса и с первым входом пятого элемента И, выход мультиплексора соединен с вторым входом пятого элемента И, выход которого соединен с единичным входом первого триггера, инверсный выход которого соединен с третьим входом первого элемента И, п-й выход блока памяти соединен с информационным входом второго триггера.

а+1 а+2

a+k-2 a+k-1

I 11 Код призна- Адрес уска условно- ловного го перехода перехода

Слово управления Слово управления Слово управления Слово управления

Код призна- Адрес ус- ка уловно- ловного перехода перехода

a+k+m

1

Слово управления

Продолжение таблида

О

a+k-Hn+1

2J

1

М ч/ N / V

I

21

0fif

Vj /4 Фиг.2

Составитель Н.Торопова Редактор Е.Папп Техред А.Кравчук Корректор М.Максимишинец

Заказ 7526/51 Тираж 670 Подписное ВНИИПИ Государственногц комитета СССР

по делам изобретений и открытий 1 13035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

22

Q О

V

I

25

26

0fif Jr

/4 Фиг.2

12

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1179337A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Микропрограммное устройство управления с контролем переходов | 1982 |

|

SU1109749A2 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

Изобретение относится к вычислительной технике и может быть использовано тронных коммутаторах и устройствах обработки информации. Целью изобретения является увеличение быстродействия. Отличительной особенностью I устройства является то, что в промежутке между двумя импульсами с выхода распределителя импульсов, когда на выходы устройства подается предпоследнее слово микропрограммы,происходит анализ признака условного перехода - и формирование первого адреса следующей микропрограммы. Поставленная цель достигается за счет введения в устройство регистра 3 адреса и второго триггера 15. ФцеЛ

| Микропрограммное устройство управления | 1979 |

|

SU834700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-23—Публикация

1985-02-25—Подача