(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Усилитель считывания | 1988 |

|

SU1580441A1 |

| Усилитель считывания | 1986 |

|

SU1368918A1 |

| Формирователь логических перепадов | 1987 |

|

SU1531157A1 |

| Интегральный ЭСЛ-элемент | 1988 |

|

SU1531209A1 |

| Транзисторный логический элемент | 1988 |

|

SU1621165A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1492381A1 |

| Формирователь импульсов управления | 1985 |

|

SU1290501A1 |

| Усилитель считывания | 1989 |

|

SU1658209A1 |

Изобретение относится к импульсной технике и может быть использовано при построении микросхем ЭСЛ- типа. Цель изобретения - повышение быстродействия. Эмиттерно-связанный элемент содержит четыре транзистора, четыре резистора и диод. Введение четвертого транзистора,четвертого резистора и диода позволяет повысить быстродействие эмиттерно-связан- ного логического элемента на высоких частотах повторения входного сигнала за счет возможности уменьшения выходного логического перепада путем значительного уменьшения зависимости изменения тока, задаваемого генератором тока, от изменения напряжений входного сигнала. 1 ил.

Изобретение относится к импульсной технике и может быть использовано при построении микросхем ЭСЛ-типа.

Цель изобретения - повышениебы- стродейств я эмиттерно-связанного элемента на высоких частотах повторения сигнала при той же потребляемой мощности за счет возможности уменьшения выходного логического перепада, которая реализуется из-за значительного уменьшения зависимости изменений тока, задаваемого генератором тока, от изменения напряжений входного сигнала.

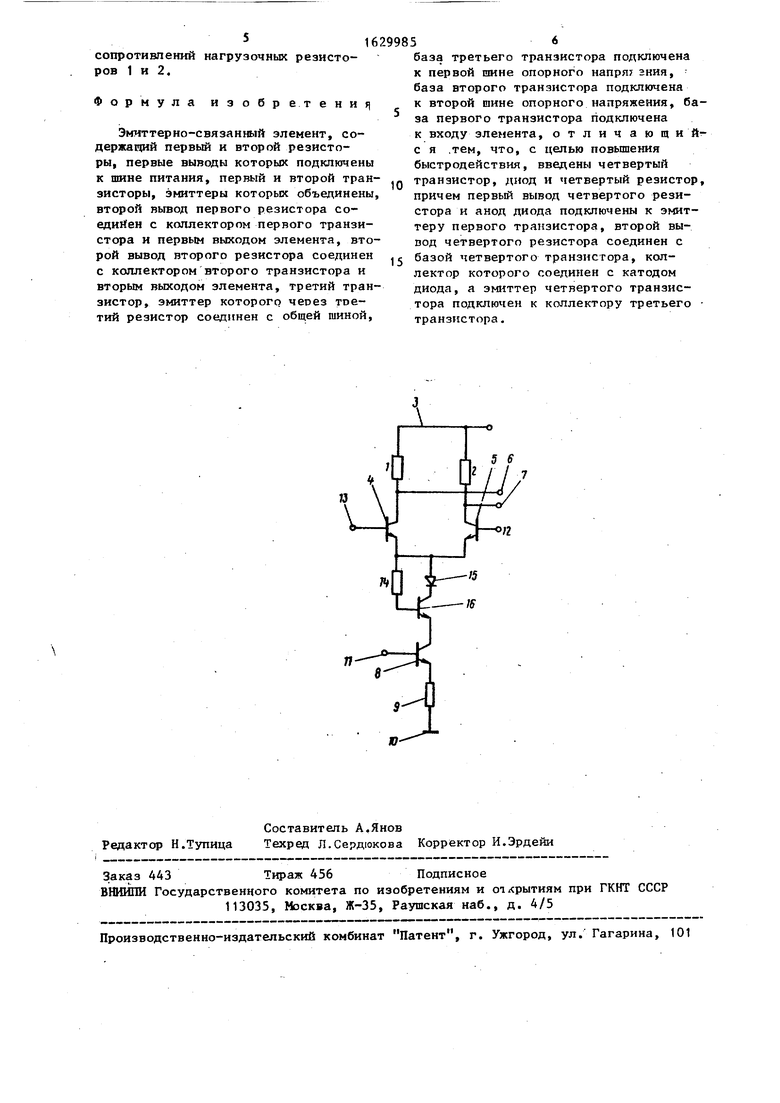

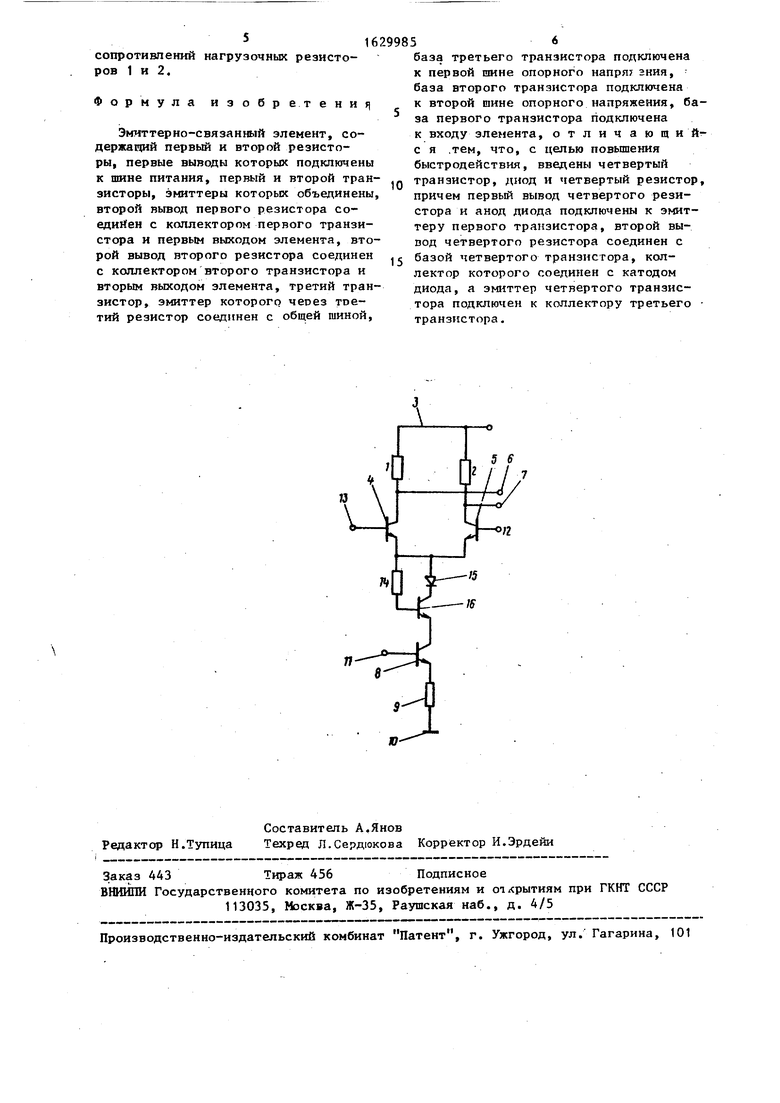

На чертеже приведена -электрическая принципиальная схема эмиттерно-связанного элемента.

Эмиттерно-связанный элемент содержит первый 1 и второй 2 резисторы, каждый из которых подключен первым выводом к шине 3 питания, первый 4 и второй 5 транзисторы, эмиттеры которых объединены, второй вывод резистора 1 соединен с коллектором транзистора 4 и первым выходом 6 элемента, второй вывод резистора 2 соединен с коллектором транзистора 5 и вторым выходом 7 элемента, третий транзистор 8, эмиттер которого через третий резистор 9 соединен с общей шиной 10, база транзистора 8 подключена к первой пине 11 опорного напряжения, база транзистора 5 подключена к второй шине 12 опорного напряжения.

база транзистора 4 подключена к входу

13элемента,первый вывод четвертого резистора 14 и анод диода 15 подключены к объединенным эмиттерам транзис- торов 4 и. 5, второй вывод резистора

14соединен с базой четвертого транзистора 16, коллектор которого роеди- нен с катодом диода 15, а эмиттер транзистора 16 подключен к коллекто- ру транзистора 8.

Эмиттерно-связанный элемент работает следующим образом.

При подаче.на вход 13 элемента напряжения входного сигнала низкого уровня (уровня логического О) ток в базу транзистора 4 не течет - транзистор 4 закрыт, транзистор 5 открыт за счет управления гоком от источника опорного напряжения, а ток от шины 3 питания к общей шине 10 через резистор 2, открытый транзистор 5, резистор 14, диод 15 и транзистор 16 определяется генератором тока, выполненным на резисторе 9 и транзисто- ре 8, который управляется от источника опорного напряжения. Напряжение на коллекторе транзистора 4 и выходе

6элемента повышено на величину логического перепада (это напряжение вы- ходного сигнала высокого уровня - уровня логической 1), напряжение

на коллекторе транзистора 5 и выходе

7элемента понижено на величину логического перепада (это напряжение вы ходного сигнала низкого уровня - уровня логического О).

При подаче на вход 13 элемента напряжения входного сигнала высокого уровня (уровня логической 1) ток в базу транзистора 5 от источника опорного напряжения не течет - транзистор 5 закрыт,, от входа 13 ток течет в базу транзистора 4 транзистор 4 от- крыт, а ток от шины 3 питания к общей шине 10 через резистор 1, открытый транзистор 4, резистор 14, диод

15и транзистор 16 определяется генератором тока, выполненным на рези- сторе 9 и транзисторе 8. Напряжение

на коллекторе транзистора 4 и выходе 6 элемента понижено на величину логического перепада (это напряжение выходного сигнала низкого уровня -уровня логичес кого О), напряжение на коллекторе транзистора 5 и выходе 7 элемента повышено на величину логического перепада (это напряжение выходного сигнала высокого уровня - уровня логической 1).

Каскад на транзисторе 16, резисторе 14 и диоде 15 постоянно поддерживает режим транзистора 16 на границе активного режима и режима насыщения . При этом при изменении напряжения входного сигнала на входе 13 о напряжения, равного напряжению источника опорного напряжения, до напряжения более высокого значения (и наоборот) происходит такое же изменени напряжения на объединенных эмиттерах а изменение напряжения на коллекторе транзистора 8 уменьшается за счет работы каскада на транзисторе 16. Это позволяет уменьшить изменения тока генератора тока на транзисторе 8.

Так как каскад на транзисторе 16, резисторе 14 и диоде 15, включенный последовательно между коллектором транзистора 8 генератора тока и объединенными эмиттерами транзисторов 4 и 5, все время поддерживает режим транзистора 16 на границе насыщения, то диффузионная емкость прямосмещен- ного р-п перехода база-эмиттер транзистора 16 достаточно велика (ввиду значительного объемного заряда неосновных носителей в цепи транзистора 16) - настолько, что постоянная времени цепи последовательно включенных резистора 14 и вышеупомянутой емкости имеет значительную величину. Соответственно и быстродействие каскада на вновь введенных элементах достаточно низкое. Поэтому для изменений напряжения входного сигнала с достаточно высокой частотой повторения, период следования которой менее постоянной впемени вновь введенной цепи резистора 14 и емкости база-эмиттер транзистора 16, эти изменения напряжения входного сигнала повторяются на объединенных эмиттерах транзисторов 4 и 5,но срабатываются со значительным ослаблением вновь введенным каскадом на коллекторе транзистора 8 генератора тока, что позволяет генератору тока значительно уменьшить зависимость генерируемого им тока от изменений входного гигнала. А это, в свою оче- редь,.позволяет повысить быстродействие эмиттерно-связанного элемента при той же потребляемой мощности путем уменьшения выходных логических перепадов за счет уменьшения величин

сопротивлений ров 1 и 2.

нагрузочных резистоФормула изобретение

Эмчттерно-связанный элемент, содержащий первый и второй резисторы, первые выводы которых подключены к шине питания, первый и второй транзисторы, эмиттеры которых объединены, второй вывод первого резистора со- едиЖен с коллектором первого транзистора и первым выходом элемента, второй вывод второго резистора соединен с коллектором второго транзистора и вторым выходом элемента, третий транзистор, эмиттер которого чепез тое- тий резистор соединен с общей шиной,

П

5

база третьего транзистора подключена к первой шине опорного напря эния, база второго транзистора подключена к второй шине опорного напряжения, база первого транзистора подключена к входу элемента, отличающий- с я .тем, что, с целью повышения быстродействия, введены четвертый транзистор, диод и четвертый резистор, причем первый вывод четвертого резистора и анод диода подключены к эмиттеру первого транзистора, второй вывод четвертого резистора соединен с базой четвертого транзистора, коллектор которого соединен с катодом диода, а эмиттер четвертого транзистора подключен к коллектору третьего транзистора.

| Апексенко А.Г., Ыагурин И.И | |||

| Микросхемотехника | |||

| - М.: Радио и связь, 1982, с.71, рис.2.19 а | |||

| Абрайтис В.-Б.Б | |||

| и др | |||

| Микропроцессорный комплект | |||

| Всасывающе-нагнетательное устройство для передвижения судов | 1925 |

|

SU1800A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-02-23—Публикация

1988-08-04—Подача