Устройство относится к вычислительной технике и, в частности, может быть использовано в управля- кздих вычислительных системах.

Известно многоканальное устройство коммутации-, в котором управление поочередным подключением процессоров к общей магистрали осуществляется устройством-диспетчером, анализирующим запросы процессоров на пользование общими ресурсами такими, как память, устройства ввода-вывода.

В системе может объединяться до восьми микро-ЭВМ, семь нз которых входят на общую для них магистраль отделенную от магистрали с общими ресурсами контроллером шины. В устройство коммутации, кроме конТроллера шины, содержащего коммутатор/ входит планировщик ресурсов 1.

Недостатком такого устройства , коммутации является наличие достаточно сложных и поэтому недостаточно надежных общих элементов (в рассматриваемрм случае - планировщик ресурсов и контроллер шины), отказ какого-либо из которых приводит к отказу всей системы.

Известно также устройство, в котором каждая из множества микро-ЭВМ имеет локальную память, и кроме того, предусмотрено множество общих запоминающих устройств, каждое из которых связано с двумя микро-ЭВМ через средство управления. Каждое из множества средств управления координирует обращения микро-ЭВМ

10 к общей памяти и запрещает одной из микро-ЭВМ обращаться к общей памяти, когда аналогичное обращение выполняет другая микро-ЭВМ t 2.

Недостатком этой системы являет15ся наличие общего для обеих микроЭВМ средства управления подключением к общему запоминающему устройству и малое количество объединяемых микро-;ЭВМ.

20

Наиболее близким к изобретению техническим решением является многоканальное устройство коммутации магистралей, в котором основными элементс1ми являются мультиплексор

25 и таймер. Мультиплексор соединен с общей магистралью системи и с локальными магистралями процессоров. Таймер соединен с мультиплексором и процессорами. Подключение локальных

30 магистргшей к общей магистраши осуществляется мультиплексором пооче- , Iредно в режиме разделения времени, организуемого за счет фазового сдвига между синхроимпульсами, вырабатываемыми таймером. Данное устройство выгодно отличается простотой 3

Недостатком известного устройства является, во-первых, то, что отказ любого из элементов переключений магистралей приводит :с отказу всей системы, во-вторых, то, что при отка,зе какого-либо из процессоров нет возможности другим (исправным) процессором взять на себя обслуживание устройств, подсоединенных к локальной магистраши отказавшего процессора, и, в-третьих, невозможность коммутации большого числа локальных магистралей..

Целью изобретения является .повышение надежности и пропускной способности устройства.

Поставленная цель достигается тем что в многоканальное устройство коммутации магистралей, содержащее п коммутирующих блоков, выполненных в виде коммутатора, первые входы-выходы которых соединены с общей магистралью, а вторые входы-выходы с соответствующими локальными магист ралями, в каждый коммутирующий блок введены счетчик, блок злементов ИЛИ, датчик начального значения счетчика, регистр управляющей информации, триггер управления, первый и второй элементы ИЛИ, элемент И, триггер блокировки и регистр самоотключения, причем вход регистра управляющей информации соединен с первым входом-выходоь. коммутатора, первый выход - с первым входом первого элемента ИЛИ и с выходом отключения процессора устройства, второй выход - с первым входом второго элемента ИЛИ, и третий выход - с первым входом блока элемента ИЛИ, второй вход которого соединен с выходом датчика начального значения счетчика, а выход - с .входом параллельной записи счетчика, счетный вход которого соединен с выходом элемента И, а вход установки начального значения - с первым входомвыходом устройства и нулевым входом тригг ера блокировки, выход первого элемента ИЛИ подключен к единичному входу триггера управления, нулевой вход которого соединен с выходом второго элемента ИЛИ и единичным входом триггера блокировки, выход которого подключен к первому входу элемента И, второй вход которого соединен с вторым входом-выходом устройства, второй вход второго элемента ИЛИ подключен к выходу регистра самоотключения, которого соединен с вторым входом-выходом устройства,третий вход второго элемента ИЛИ соединен

через коммутирующий блок с входом отключения по времени устройства.

Реализация такой структуры многоканального устройства коммутации магистралей позволяет каждому из процессоров поочередно подсоединяться к общей магистрали, и выполняя роль ведущего, при необходимости отключать неисправный процессор от его локальной магистрали, подключат эту локальную .магистрашь к общей и обслуживать устройства, подсоединенные к локальной магистрали отказавшегося процессора. Прм этом устройство принципиально не ограничивает чи.сло коммутируемых локальных магистралей . ,

Общая магистраль системы и локалные магистрали имеют одинаковую структуру и могут, например, иметь трехшинную организацию, при которой магистраль включает в себя: шину данных, адресную шину и шину управления. Такая организация характерна для многих микропроцессорных систем построенных, например, на базе микропроцессоров типа К580ИК80,18080, Мб800, Z80.

Одним из положений, лежащих в основе построения предлагаемого устроства коммутации, является оценка занятости общей магистрали по наличию ,на ней синхроимпульсов одного из сигналов шины управления.

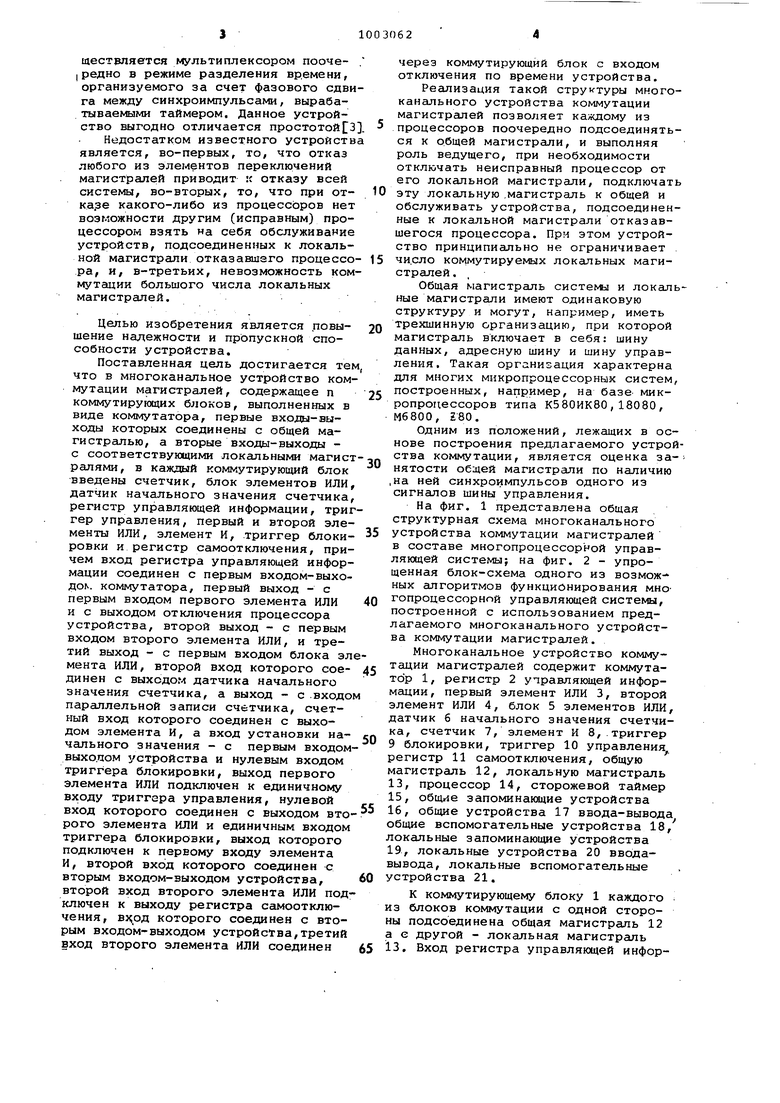

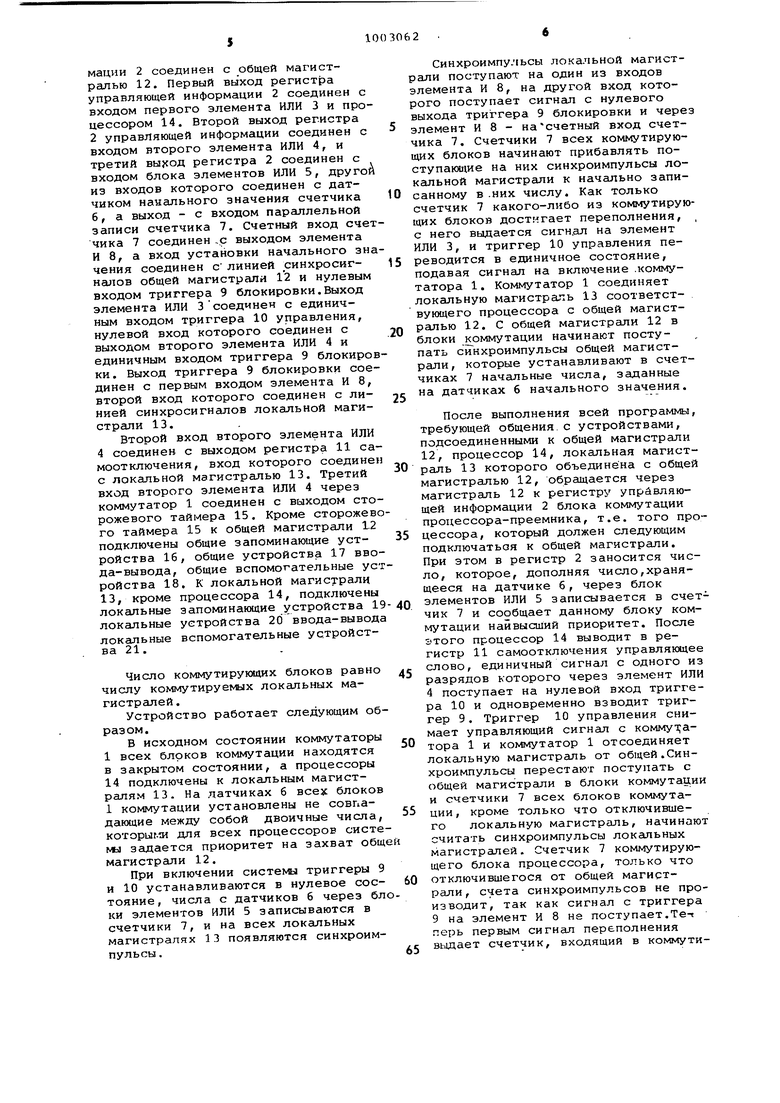

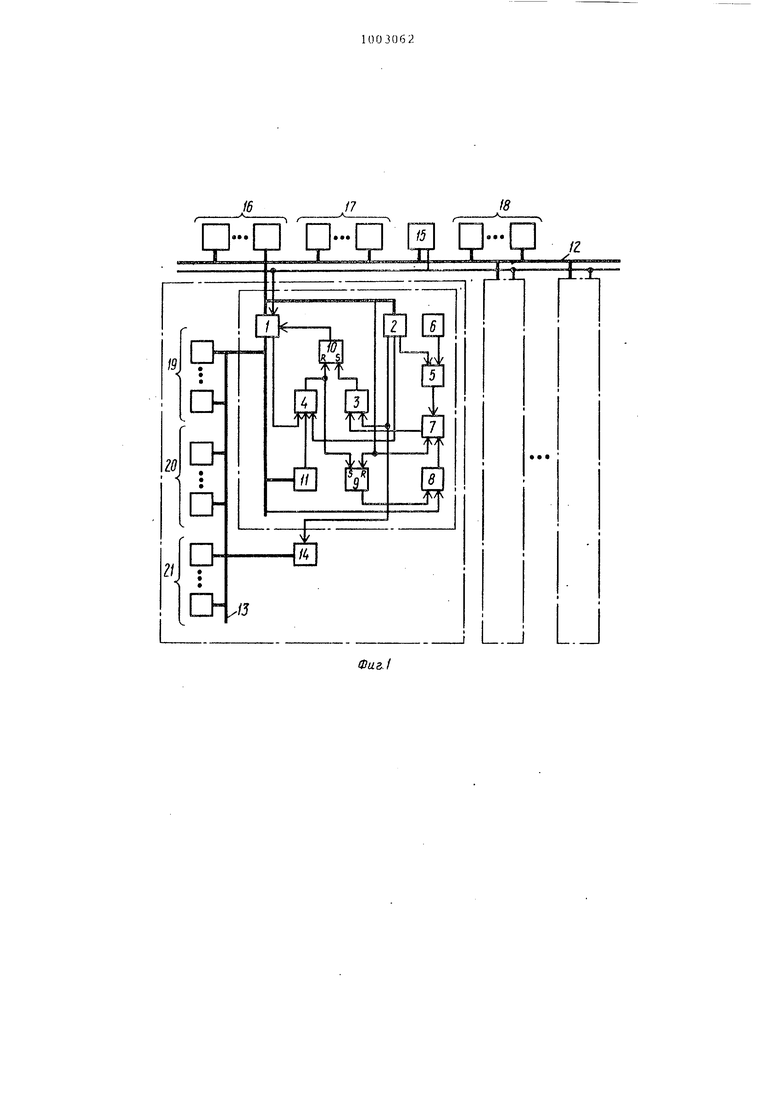

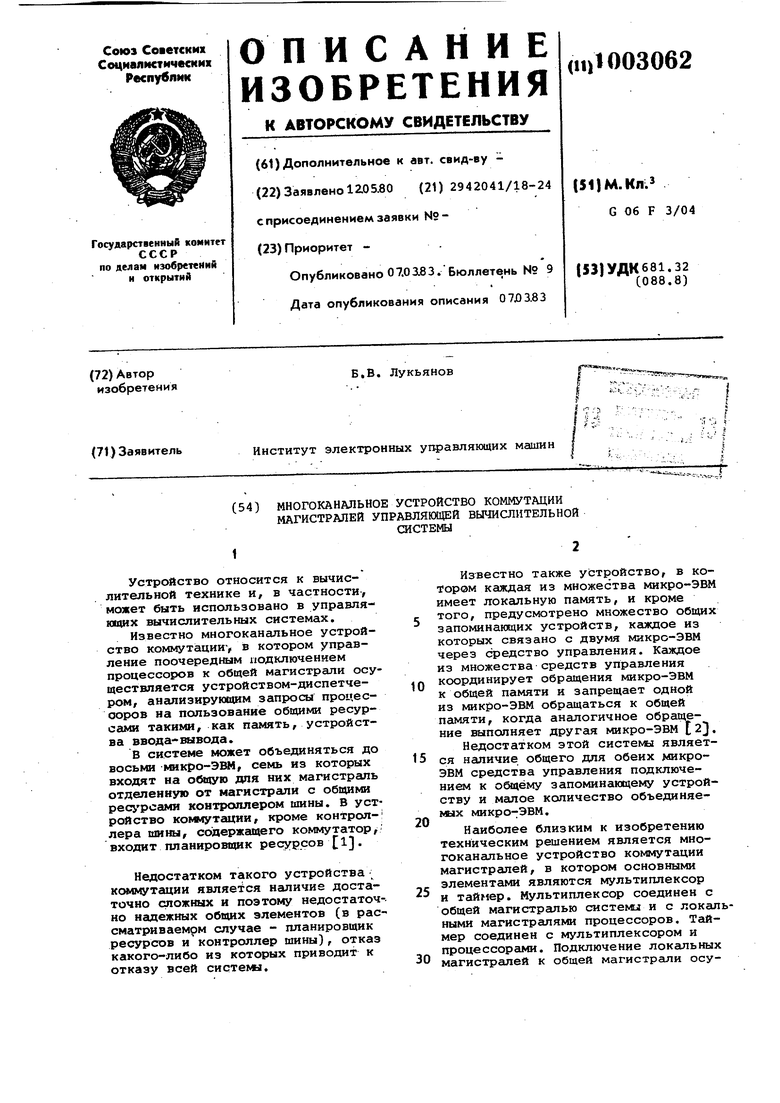

На фиг. 1 представлена общая структурная схема многоканального устройства коммутации магистралей в составе многопроцессорной управляющей системы; на фиг. 2 - упрощенная блок-схема одного из возмож- ных алгоритмов функционирования многопроцессорной управляющей системы, построенной с использованием предлагаемого многоканального устройства коммутации магистралей.

Многоканальное устройство коммутации магистралей содержит коммутатор 1, регистр 2 управляющей информации, первый элемент ИЛИ 3, второй элемент ИЛИ 4, блок 5 элементов ИЛИ датчик б начального значения счетчика, счетчик 7, элемент И 8,.триггер 9 блокировки, триггер 10 управления регистр 11 самоотключения, общую магистраль 12, локальную магистраль 13, процессор 14, сторожевой таймер

15,общие запоминающие устройства

16,общие устройства 17 ввода-вывода общие вспомогательные устройства 18 локальные запоминающие устройства 19, локальные устройства 20 вводавывода, локсшьные вспомогательные устройства 21.

К коммутирующему блоку 1 каждого из блоков коммутации с одной стороны подсоединена общая магистраль 12 а с другой - локальная магистраль 13, Вход регистра управляющей информацни 2 соединен с общей магистралью 12. Первый выход регистра управляющей информации 2 соединен с входом первого элемента ИЛИ 3 и процессором 14. Второй выход регистра 2 управляющей информации соединен с входом второго элемента ИЛИ 4, и третий вы}{од регистра 2 соединен с входом блока элементов ИЛИ 5, другой из входов которого соединен с датчиком канального значения счетчика 6, а выход - с входом параллельной записи счетчика 7. Счетный вход счет чика 7 соединен ,.с выходом элемента И 8, а вход установки начального зна чения соединен с линией синхросигналов общей магистрали 12 и нулевым входом триггера 9 блокировки.Выход элемента ИЛИ 3соединен с единичным входом триггера 10 управления, нулевой вход которого соединен с выходом второго элемента ИЛИ 4 и единичным входом триггера 9 блокиров ки. Выход триггера 9 блокировки соединен с первым входом элемента И 8, второй вход которого соединен с линией синхросигналов локальной магистрали 13. Второй вход второго элемента ИЛИ 4 соединен с выходом регистра 11 самоотключения, вход которого соединен с локальной магистралью 13. Третий вход второго элемента ИЛИ 4 через коммутатор 1 соединен с выходом сторожевого таймера 15. Кроме сторожево го таймера 15 к общей магистрали 12 подключены общие запоминающие устройства 16, общие устройства 17 ввода-вывода, общие вспомот ательные уст ройства 18. К локальной магистрали 13, кроме процессора 14, подключены локальные запоминающие устройства 19 локальные устройства 20 ввода-вывода локальные вспомогательные устройства 21. Число коммутирующих блоков равно числу коммутируемых локальных магистралей . Устройство работает следующим образом. В исходном состоянии коммутаторы 1 всех блоков коммутации находятся в закрытом состоянии, а процессоры 14 подключены к локальным магистралям 13. На датчиках б Bcejc блоков 1 коммутации установлены не совпадающие между собой двоичные числа, которыг.да для всех процессоров системы Зсщается приоритет на захват обще магистрали 12. При включении систег ы триггеры 9 и 10 устанавливаются в нулевое соетояние, числа с датчиков 6 через бло ки элементов ИЛИ 5 записываются в счетчики 7, и на всех локальных магистралях 13 появляются синхроимпульсы. Синхроимпу.чьсы локальной магистрали поступают на один из входов элемента И 8, на другой вход которого поступает сигнал с нулевого выхода триггера 9 блокировки и через элемент И 8 - на счетный вход счетчика 7. Счетчики 7 всех коммутирующих блоков начинают прибавлять поступающие на них синхроимпульсы локальной магистрали к начально записанному в .них числу. Как только счетчик 7 какого-либо из коммутирующих блоков достигает переполнения, с него выдается сигн.ал на элемент ИЛИ 3, и триггер 10 управления переводится в единичное состояние, подавая сигнал на включение .коммутатора 1. Коммутатор 1 соединяет локальную магистраль 13 соответствующего процессора с общей магистралью 12. С общей магистрали 12 в блоки коммутации начинают поступать синхроимпульсы общей магистрали, которые устанавливают в счетчиках 7 начальные числа, заданные на датчиках 6 начального значения. После выполнения всей программы, требующей общения.с устройствами, подсоединенными к общей магистрали 12, процессор 14, локальная магистраль 13 которого объединена с общей магистралью 12, обращается через магистраль 12 к регистру упрйвляющей информации 2 блока коммутации процессора-преемника, т.е. того процессора, который должен следующим подключаться к общей магистрали. При этом в регистр 2 заносится число, которое, дополняя число,хранящееся на датчике б, через блок элементов ИЛИ 5 записывается в счетчик 7 и сообщает данному блоку коммутации наивысший приоритет. После этого процессор 14 выводит в регистр 11 самоотключения управляющее слово, единичный сигнал с одного из разрядов которого через элемент ИЛИ 4 поступает на нулевой вход триггера 10 и одновременно взводит триггер 9. Триггер 10 управления снимает управляющий сигнал с комму1;атора 1 и коммутатор 1 отсоединяет локальную магистраль от общей.Синхроимпульсы перестают поступать с общей магистраши в блоки коммутации и счетчики 7 всех блоков коммутации , кроме только что отключившего локс1льную магистраль, начинают считать синхроимпульсы локальных магистралей. Счетчик 7 коммутирующего блока процессора, только что отключившегося от общей магистрали, счета синхроимпульсов не производит, так как сигнал с триггера 9 на элемент И 8 не поступает.Те-т перь первым сигнал переполнения вьадает счетчик, входящий в коммутиРУЮ1ДИ0 блок процессора-преемника, и в результате локальная магистрал этого процессора подсоединяется к общей магистрали. Если процессор, соединенный в данный момент с общей магистралью, получает информацию о том, что како либо из других процессоров неисправен (фиг. 2), то он посылает управляющее слово в регистр 5 этого процессора такое, что единичный сигнал одного из разрядов поступает на управляющий вход неисправного проце сора 14, отключая его,и через элемент ИЛИ 3 на триггер 10, устанавливая его в единичное состояние. Триггер 10 включает коммутатор 1 который подсоединяет к общей магист рали 12 локальную магистраль 13 неисправного процессора. После этого процессор, соединенный с общей маг.истралью, выполняет программу по обслуживанию устройств неисправного процессора. Сторожевой таймер 15 настраивается на время, несколько большее тр буемого процес.сору для работы на общей магистрали. При каждой смене процессора Сотключение локальной магистрали от общей) таймер сбрасывается. Если процессор, захвативший -Общую магист раль, не отключается от нее дольше положенного- времени, таймер 15 срабатывает, и сигнал от него через включенный коммутатор 1 поступает на элемент ИЛИ 4, сбрасывает триггер 10 и выключает коммутатор 1, от ключая локальную магистраг1Ь от обше После этого общую магистраль зах ватывает процессор с наивысшим сред оставшихся процессоров приоритетом. Процессоры в то время, когда их локальные магистрали не подключены к общей магистрали, нормальным обра зом выполняют свои рабочие программыОдин из возможных алгоритмов работы процессоров при подсоединении к общей магистрали показан на фиг.2 Функционирование системы, содержащей N процессоров (ПР) начинается с ее включения.После этого одним из процессоров (ПР К) производится захват общей магистрали (ОМ) как описано. Затем К-й продессор выполняет свою рабочую программу и самотестирование. Самотестирование заканчивается занесением результирую щего контрольного числа в соответст вующую ячейку общего ЗУ. Процессор, владеющей общей магистралью, оценивает состояние других процессоров и при необходимости обслуживает устройства неисправных процессоров. Это произ водится в несколько шагов. Вначале сравнивается контрольное число, полученное при самотестировании проверяемого процессора (nPfiJ с эталонной константой. В зависимости от результата сравнения, к содержимому одной из ячеек общего ОЗУ ячейки голосования, добавляется +1 или -1, По значению числа в ячейке голосования производится оценка проверяемого процессора - исправен или неисправен. При обнаружении неисправного продессора производятся действия, указанные на фиг. 2 в первой ветви и описанные при рассмотрении работы устройства (фиг. 1).После оценки состояния всех процессоров владеющий общей магистралью процессор проверяет, не относится ли к неисправным процессор-преемник, указанный в его программе. Если намеченный процессор-преемник оказывается неисправным, то по следовательным перебором определяется исправный процессор и первому из найденных исправных процессоров устанавливается наивысший приоритет на захват магистрали. Процессор, владеющий общей магистралью (nPfKj), отключает свою локальную магистраль (ЯМ) и переходит в режим работы по обслуживанию устройств, подсоединенных к его локальной магистрали.. А процессор-преемник описанным образом захватывает общую магистраль и цикл работы системы повторяется. .Ориентировочно относительная экономическая эффективность внедрения предлагаемого устройства .может быть оценена по отношению вероятности безотказной работы устройства (Е( ) t к вероятности безотказной работы известного устройства (Pi) и по увеличению числа объединяемых в систему процессов РЛ -l-0-Pgk) г vnoPvnA где Р - вероятность безотказной работы блока коммутации; рд- вероятность безотказной работы общей части известного устройства; Р - вероятность безотказной работы части известного устройства, связанной с отдель1НЫМ процессором; N - количество процессоров в системе. Выражение (1) справедливо для случая, когда снижение скорости опроса входных каналов и выдачи управляющих или информационных сигналов, вызываемое отказами процессоров, не приводит к нарушению нормальной работы управляемого объекта. Пусть мы имеем следующие значения вероятностей безотказной работы соечастей устройств коммутатавныхции: VA 09 %о 09 - показатели надежнбС и устройств KOMi iyTauHa в зависимооти от количества объединяемых процессоров будут следую1ЦИМИ:. Возможное число подключаемых прок цессоров в предлагаемом устройстве практически ограничивается лишь электрическими характеристиками магистралей (допустимой длиной линий, нагрузочной способностью, токами утечкк) и разрядностью используемых счетчиков. При разрешении между задаваемыми приоритетами на захват общей магистрали в два импульса для четырехразрядных счетчиков имеется возможность объединения в систему до восьми процессоров. Каждый дополнительный разряд счетчика увеличивает возможное число объединяемых процессоров вдвое Так, при вGCь «paзpядныx счетчиках, к общей магистрали через предлагаемо устройство, может подключаться до 12 процессоров. В известном устройстве число подключаемых процессоров ограничено вре менными соотношениями и не может пре выаать нескольких единиц. Формула изобретения Многоканальное устройство коммута ции магистралей управляющей вычислительной системл, содержащее п коммутирующих блоков, выполненных в виде коммутатора, первые, входы-выходы которых соединены с общей магистралью а вторые входы-выходы - с соответствующими локальными магистралями, отличающееся тем, что, г. целью повышения .его надежности и пропускной способности, в каждый коммутнрующий блок введены счетчик, блок элементов ИЛИ, датчик начального значения счетчика, регистр управляющей информации, триггер управления, пер«. вый и второй элементы ИЛИ, элемент И, триггер блокировки и регистр самоотключения, причем вход регистра управляющей информации соединен с первым входом-выходом коммутатора, первый выход - с первым входом первого элемента ИЛИ и с выходом отключения процессора устройства, второй выход - с первым входом второго элемента ИЛИ, а третий выход - с первым входом блока элементов ИЛИ, второй вход которого соединен с выходом датчика начального значения .счетчика, а выход - с входом параллельной записи счетчика, счетный вход которого соединен с выходом элемента И, а вход установки начального значения с первым входом-выходом устройства и нулевым входом триггера блокировки, выход первого элемента ИЛИ подключен к единичному входу триггера управления, нулевой вход которого соединен с выходом второго элемента ИЛИ и единичным входом .тдэиггера блокировки, выход которого подключен к первому входу элемента И, второй вход которого соединен с вторым входом-выходом устройства, второй вход второго элемента ИЛИ подключен к выходу регистра самоотключения, вход которого соединен с вторым входом-выходом устройства, третий вход, второго элемента ИЛИ соединен через коммутирующий блок входом отключения по времени устройства. Источники информации, принятые во внимание при экспертизе 1.Экспресс-информация Вычислительная техника, 1977, 24, реферат №142. 2.Патент США 4065809, кл. 364-200, опублик. 1979. 3.Патент США 4164787, кл. 364-200, опублик. 1980 (прототип) .

/5

18

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для отладки программ | 1986 |

|

SU1319038A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для восстановления работы процессора | 1987 |

|

SU1476467A2 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для измерения фазовых сдвигов сигналов от многоканальных интерферометров термоядерных установок | 1983 |

|

SU1352395A1 |

Авторы

Даты

1983-03-07—Публикация

1980-05-12—Подача