1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных машинах, рабртаквдих в избыточной системе счисления.

Известно устройство для сложения нескольких двоичных чисел 1, содержащее несколько рядов одноразрядных двоичных сумматоров в каждом из блоков суммирования. В данном устройстве производится сложение только в двоичной системе счисления, т.е, это устройство не позволяет выполнить суммирование нескольких чисел в избыточной системе счисления .

Известно устройство для сложения в избыточной системе счисления С2}, содержащее два комбинационных сумматора, логические схемы .выработки положительного и отрицательного переносов и группу элементов ИЛИ.

Недостатком данного устройства является то, что оно производит сложение только двух чисел. Для сложения нескольких чисел требуется значительное увеличение оборудования.. Кроме того, это устройство позволяет суммировать только в системе счисления с нечетным основанием.

Наиболее близким к предложенному является устройство для сложения N чисел в избыточной системе счисления DJ, содержащее в каждом из п разрядов два двоичных сукжатора и сумматор в избыточной системе счисления, в котором производится сло10жение нескольких чисел. Сумматор в Дг5оичной избытс чной системе счисления содержит четыре одноразрядных двоичных суьвчатора и два элемента запрета.

15

Это устройство производит сложение чисел только в двоичной избыточной системе счисления.

Цель изобретения - расширение 20 функциональных возможностей,,т.е. обеспечение суммирования чисел в избыточной системе счисления с произвольным основанием.

Для достижения этой цели в каждый из п разрядов устройства, содержащий первый и второй двоичные сумматоры, первые группы входов которых соединены с шинами соответственно отрицательных и положительных значений соответствующего разряда слагаемых (log од,Р+1 где р - осночание системы счисления) , введен блок а.нализа. Выходы k младших разрядов двоичных сумматоров подключены к 2k входам блока анализа, а выходы остальных разрядов первого и второго двоичных сумматоров i-ro разряда устройства подключены к вторым группам входов соответственно-первого и второго двоичных сумматоров следующего (i+l)-ro разряда устройства. Выходы блока анализа соединены с отрицательными и -положительными шинами результата.

При суммировании чисел в избыточной системе счисления с основанием блок анализа содержит k-разрядный двоичный сумматор, две группы элементов И и элемент НЕ.

Выход, переноса k-разрядного двоиного сумматора подключен к входу переноса первого разряда этого сумматора, к первым входам элементов И первой группы и через элемент НЕ к первым входам элементов И второй группы. Выходы элементов И первой и второй группы подключены к выходам блока анализа, а вторые входы к выходу соответствующего разряда k-разрядного двоичного сумматора, входы которого соединены с входами блока анализа.

При суммировании чисел в избыточной системе счисления с основанием ,(. 2 , блок анализа дополнительно содержит первый и второй узлы коррекции, ВХО.ДЫ которых соединены с соответствующими входами блока анализа. Выходы переноса первого и второго узлов коррекции блока анализа i-ro разряда устройства соединены с входом переноса первого разряда соответственно первого и второго двоичных сумматоров следующего (i+l)-ro разряда устройства, а . выходы суммы первого и второго узлов коррекции соединены с соответствующими входами k-разрядного сумматора блока анализа.

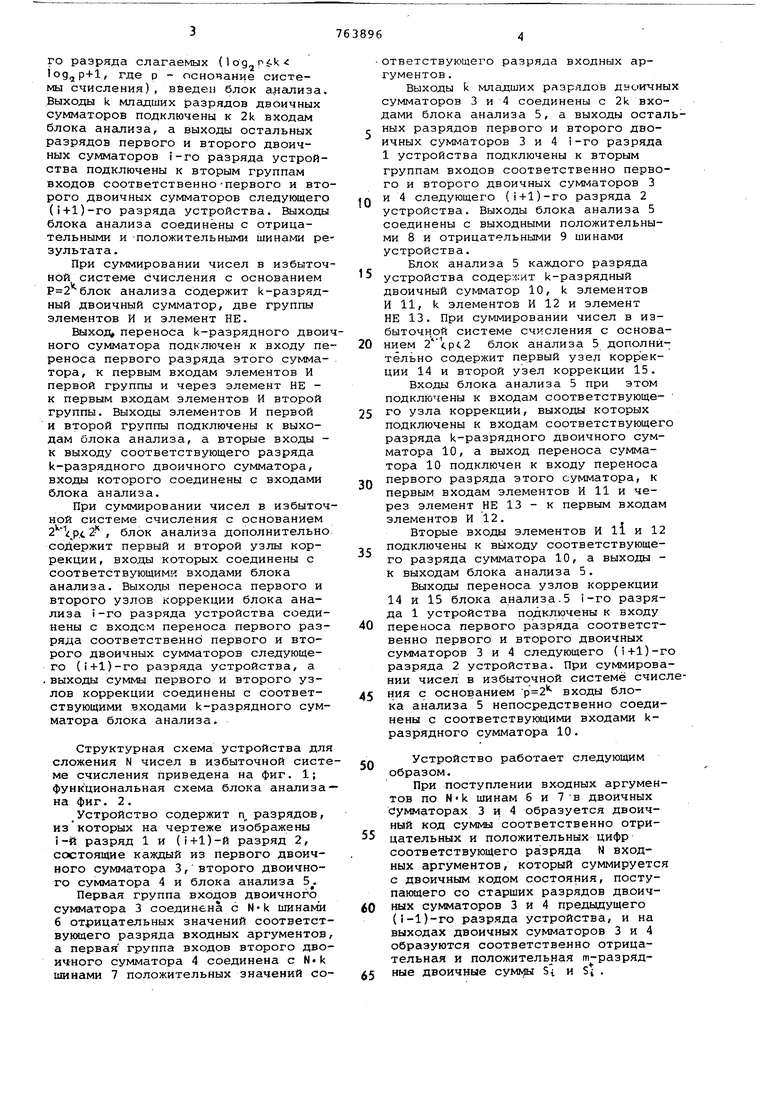

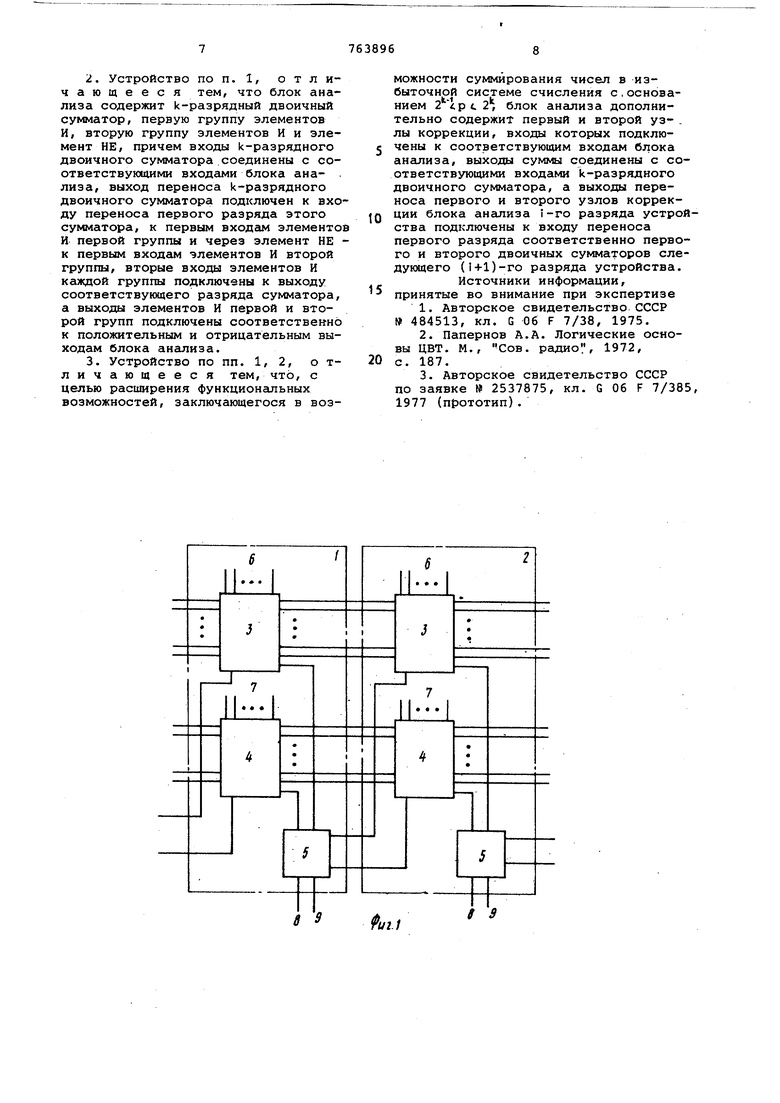

Структурная схема устройства для сложения N чисел в избыточной системе счисления приведена на фиг. 1; функциональная схема блока анализа- на фиг, 2.

Устройство содержит п разрядов, из которых на чертеже изображены i-Й разряд 1 и (1+1)-й разряд 2, состоящие каждый из первого двоичного сумматора 3,второго двоичного сумматора 4 и блока анализа 5.

Первая группа входов двоичного сумматора 3 соединена с N-k 6 отрицательных значений соответствующего разряда входных аргументов, а первая группа входов второго двоичного cyiviMaTopa 4 соединена с N«k шинами 7 положительных значений соответствующет о разряда входных аргументов .

Выходы k младших разрядов двоичных умматоров 3 и 4 соединены с 2k вхоами блока анализа 5, а выходы остальных разрядов первого и второго двочных сумматоров 3 и 4 i-ro разряда 1 устройства подключены к вторым группам входов соответственно первого и второго двоичных сумматоров 3 и 4 следующего (i+l)-ro разряда 2 устройства. Выходы блока анализа 5 соединены с выходными положительными 8 и отрицательными 9 шинами устройства.

Блок анализа 5 каждого разряда устройства содержит k-разрядный двоичный сумматор 10, k элементов И 11, k элементов И 12 и элемент НЕ 13. При суммировании чисел в избыточн.ой системе счисления с основанием 2.рс2 блок анализа 5 дополнительно содержит первый узел коррекции 14 и второй узел коррекции 15.

Входы блока анализа 5 при этом подключены к входам соответствующе- го узла коррекций, выходы которых подключены к входам соответствующего разряда k-разрядного двоичного сумматора 10, а выход переноса сумматора 10 подключен к входу переноса первого разряда этого сумматора, к первым входам элементов И 11 и через элемент НЕ 13 - к первым входам элементов И 12.

Вторые входы элементов И 11 и 12 подключены к выходу соответствующего разряда сумматора 10, а выходы к выходам блока анализа 5.

Выходы переноса узлов коррекции 14 и 15 блока анализа.5 i-ro разряда 1 устройства подключены к входу переноса первого разряда соответственно первого и второго двоичных сумматоров 3 и 4 следующего (i+l)-ro разряда 2 устройства. При суммировании чисел в избыточной системе счисления с основанием входы блока анализа 5 непосредственно соединены с соответствующими входами kразрядного сумматора 10.

Устройство работает следующим образом.

При поступлении входных аргументов по Nk шинам 6 и 7в двоичных сумматорах 3 и 4 образуется двоичный код суммы соответственно отрицательных и положительных цифр соответствующего разряда N входных аргументов, который суммируется с двоичным кодом состояния, поступающего со старших разрядов дв.оичных сумматоров 3 и 4 предыдущего (i-l)ro разряда устройства, и на выходах двоичных сумматоров 3 и 4 образуются соответственно отрицательная и положитель ная т-разрядные двоичные суммы 5| и Si . Младшие k разрядов отрицательной и положительнбй Sj сумм с выходов k младших разрядов двоичных cyi-iMaTOpoB 3 и 4 поступают в б анализа 5, в котором двоичные kразрядные положительное а и отрицательное a1 числа преобразуются в k-разрядное число Zi в избыточной системе счисления. При суммировании чисел в избыточной системе счи сления с основанием числа и ai не могут быть больше (р-1) , noэтому преобразование сводится к су мированию числа а с числом а1 в о ратном коде и анализу полученной суммы. При суммировании чисел в избыточ системе счисления с основанием 2 с р. 2 числа at и at может быть бо ше (р-1), поэтому блок анализа 5 1-го разряда 1 устройства должен вырабатывать сумму чисел а и а| и перенос в старший (ifl)-й разряд 2 устройства. Узел коррекции 14, на выходах которого подается число а вырабатывает отрицательный перенос bi и отрицательную сумму ci : b) 0 и с а| при bl 1 и при аГ(.р-1 Узел коррекции 15, на входы которого подается число, а , вырабатывает положительный перенос Ь и положительную сумму Ь 0 и при aj ;р-1 Ь| 1 и при Сумматор 10 имеет k разрядов, на входы которых поступают двоичные числа с (или а ) и с (или а ) . На выходах сумматора 10 образуется сумма Zi , которая поступает на входы соответствующих элементов И 11 и 12, на другие входы которых поступает сигнал с выхода переноса сумматора 10. На входы элементов И 11 поступает прямой сигнал переноса, а на входы элементов И 12 инверсный сигнал через элемент НЕ 13. Соответственно на выходах элементов И 11 формируются положительные значения результата сложения Z , которые поступают на положительные выходные шины 6 устройства в виде k -разрядного двоичного числа, а на выходах элементов И 12 формируются отрицательные значения результата сложения 21, которые поступают на отрицательные выходные шины 9 устройства в обратном коде. Чтобы получить прямой код отрицательных значений результата, необходимо добавить k элементов НЕ (не показаны). Пример сложения трех чисел А-2301, В-2121 и , представленных цифрами 3,2,1,0, 1, 2,иЗ приведены в таблице (при ).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Устройство для сложения в избыточнойСиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824198A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1978 |

|

SU686030A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для сложения @ -разрядных чисел в избыточной системе счисления | 1984 |

|

SU1188731A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

Проверим результат сложения 2301 2121 0120 11102 Таким образом, данное устройств позволяет производить сложение N чисел в избыточной системе счислен с основанием , при этом каж разряд числа в избыточной, системе счисления передается по шинам. Формула изобретения 1. Устройство для сложения N чи сел в избыточной системе счисления содержащее в каждом из п разрядов первый и второй двоичные сумма торы, первые группы входов которых соединены соответственно с отрицательными и положительными шцнами соответствующего разряда входных операндов, отличающееся тем, что, с целью расширения функциональных возможностей, заключающегося в возможности суки шрования чисел в избыточной системе счисления с основанием- , каждый из п разрядов устройства содержит блок анализа, 2k входов которого соединены с выходг1ми k младших разрядов двоичных сумматоров (logj pik с1 ., где р - основание системы счисления) , выходы остальных (N-k) разрядов первого и второго двоичных сумматоров i-ro разряда устройства подключены к вторым группам входов соответственно первого и второго двоичных сумматоров следующего (I+ +-1)-го разряда устройства, а k положительных и k отрицательных выходов блока анализа подключены к отрицательным и положительным шинам результата устройства соответственно.

i. Устройство по п. 1, отличающееся тем, что блок анализа содержит k-разрядный двоичный сумматор, первую группу элементов И, вторую группу элементов И и элемент НЕ, причем входы k-разрядного двоичного сумматора соединены с соответствующими входами блока ана- . ЛИЗа, выход переноса k-разрядного двоичного сумматора подключен к входу переноса первого разряда этого сумматора, к первым входам элементо И первой группы и через элемент НЕ к первым входам элементов И второй группы, вторые входы элементов И каждой группы подключены к выходу соответствующего разряда сумматора, а выходы элементов И первой и второй групп подключены соответственно к положительным и отрицательным выходам блока ансшиза.

Источники информации, принятые во внимание при экспертизе

с. 187.

по заявке 2537875, кл. G 06 F 7/385 1977 (прототип).

6i

Ci

It

А,

М «.

Cii

11

lit

/z

Zi,

IK

Раг.2

Авторы

Даты

1980-09-15—Публикация

1978-06-26—Подача