1327092

относится к вычислинп ч

тельной технике и может быть использовано при построении специализированных цифровых систем контроля, регистрации и управления.

Цель изобретения - расширение функциональных возможностей за счет суммирования чисел, представленных в

J,k,г-кoдax при сохранении способное- ю счисления. Такие системы счисления ти суммирования чисел, представленных позволяют прежде всего строить более в двоичных кодах.

На чертеже изображена принципигльчи, а диапазон представления чисел в

экономичные и более быстродействующие суммирующие устройства. При э-тон по- ная схема первых четырех (п 4) разря- мехоустойчивость j,k,r-кoдoв сравнима дов комбинационного сумматора. 15 с помехоустойчивостью кодов ФибоначКомбинационный сумматор содержит одноразрядный двухвходовой сумматор 1-1 и трехвходовые сумматоры 1-2, Г-3, 1-4, первые элементы 2-1 и 2-2 ИЛИ, вторые элементы 3-1 и 3-2 ИЛИ, элементы 4-1, 4-2, 5-1, 5-2, 6 И, выход 7 сигнала ошибки, вход 8 управлеj.,k,r-кoдax не ниже, чем в обобщенных гр-кодах. Вьшолнение арифметических операций в з,и,г-кодах значительно 20 проще, чем в известных кодах с естественной избыточностью. Это обусловлено тем, что формирование как прямых.

ния режимом, выход 9 суммы, вход 10 J-UK и обратных переносов носит локальпервого операнда, вход 11 второго one- ьм характер.

ранда.25 Пусть требуется сложить два числа

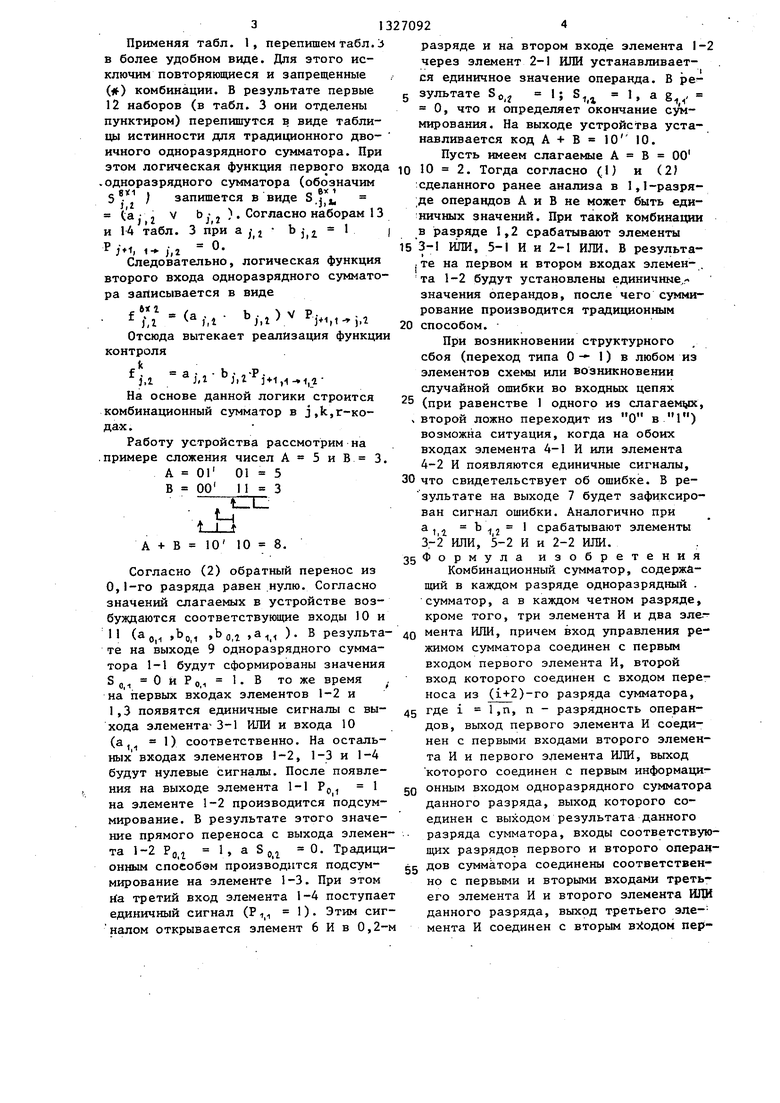

При работе в традиционных, двоичных в jfk,rKOAax по общеизвестному алго- кодах в работе участвуют одноразряд- питму Мерсера (см. табл. 2). ,ные сумматоры 1-1 - 1-4, первый 2-1, табл. 2 и далее апострофами отме- второй 3-1 элементы ИЛИ, второй эле- чены границы между группами разрядов. мент 5-1 И, первый 10 и второй вхо- ЗО примера и уравнения (1) вытека, ды слагаемого. При суммировании в двоичных традиционных кодах на управляющей шине 8 сохраняется нулевой потенциал. Суммирование производится известным образом, при этом между первым входом одноразрядного суммает, что

, ),г гг2 .

,.,:

При этом в первом саучае всегда а

j-,l

тора (вх. 1) и вторым входом (вх. 2) производится следующее перераспределение входных сигналов (а у , и Ь; . )

.J 1 J li,

35 - b. О (где а,- и b, - 1-е значения операндов А и В соответственно ), а во втором случае а -4, Ьи, 0. В первом случае, если а :. ь 5, то распространение переноса в и в соответствии с-известным алгорит- 40 следующем частичном цикле может быть мом формирование S j и Р,-

При суммировании чисел в j, k, г- кодах в работе участвуют все элементы схемы,- а на шине 8 присутствует единичный потенциал.

Сущность изобретения состоит в

не далее чем в J,l-.paзpяд, во втором случае распространение переноса в i-i-l , 1-разряд заканчивается в первом частичном цикле суммирования. Это ис- 45 ключает формирование цепочки обратного переноса более чем в пределах двух

следующем.

Пусть веса двоичных разрядов связаны между собой следующим рекурент- ным уравнением:

2h ;., J при k 1; (1)

h, ,

;Д

hj-., + Ь|.д , при k 2 при следующих начальных условиях

0,1 где h

2,

(2)

i, k

1, ол

- значение в(2са двоичного

разряда; j - номер группы.

Каждая группа состоит из двух разрядов (J 0,1,2,,,, , k - номер разряда в группе, k ). Тогда значения h,k будут равнь 1 2 4 6 12 18 36 54 108 162 „., . Данные системы счисления обладают значительными преимуществами по сравнению с фибонач- чиевыми и обобщенными г, р-системами

чи, а диапазон представления чисел в

j.,k,r-кoдax не ниже, чем в обобщенных гр-кодах. Вьшолнение арифметических операций в з,и,г-кодах значительно 20 проще, чем в известных кодах с естественной избыточностью. Это обусловлено тем, что формирование как прямых.

в jfk,rпитму Ме таб чены гра пр

ет, что

в jfk,rKOAax по общеизвестному алго- питму Мерсера (см. табл. 2). табл. 2 и далее апострофами отме чены границы между группами разрядов. примера и уравнения (1) вытека2 }, ),г гг2 .

,.,:

При этом в первом саучае всегда а

j-,l

- b. О (где а,- и b, - 1-е значения операндов А и В соответственно ), а во втором случае а -4, Ьи, 0. В первом случае, если а :. ь 5, то распространение переноса в следующем частичном цикле может быть

35 - b. О (где а,- и b, - 1-е значения операндов А и В соответственно ), а во втором случае а -4, Ьи, 0. В первом случае, если а :. ь 5, то распространение переноса в 40 следующем частичном цикле может быть

не далее чем в J,l-.paзpяд, во втором случае распространение переноса в i-i-l , 1-разряд заканчивается в первом частичном цикле суммирования. Это ис- 45 ключает формирование цепочки обратного переноса более чем в пределах двух

смежных групп для любых а - - и Ь и образование в промежуточном цикле трех единиц слагаемых (Sy. перенос 50 прямой л.перенос обратный 1). При этом j,I-разрядах регистра хранения обратного переноса всегда содержатся нули.

55

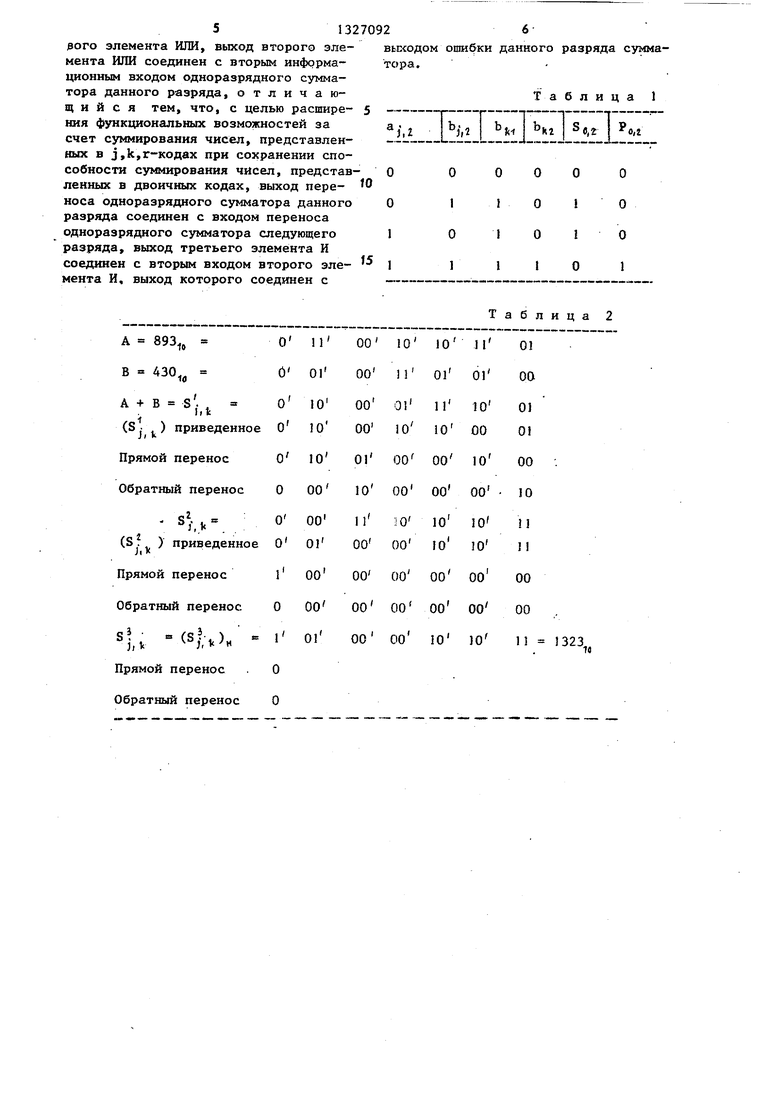

Приведенный пример сложения в i,k,r-кoдax позволяет записать таблицу истинности для логических функций каждого из п четных разрядов комбинационного сумматора.

3

Применяя табл. 1, перепишем табл. в более удобном виде. Для этого исключим повторяющиеся и запрещенные (#) комбинации. В результате первые 12 наборов (в табл. 3 они отделены пунктиром) перепишутся в виде таблицы истинности для традиционного двоичного одноразрядного сумматора. При

этом логическая функция первого входа IQ Ю одноразрядного сумматора (обозначим 5. ) запишется в виде sT t a , V Ь у j ). Согласно наборам 13 14 табл. 3 при а. j,i Ь j 1 |

, 1-ь2 ОСледовательно, логическая функция

второго входа одноразрядного сумматора записывается в виде

Р:.

/,г Ь1 ),г j,i- i.i

Отсюда вытекает реализация функции контроля

fc

}.i ° J.i J.,i-,i,a- На основе данной логики строится омбинационный сумматор в j,k,r-KO- а-х.

Работу устройства рассмотрим на римере сложения чисел А 5 и В 3. А 01 01 5 В 00

:сде де нич в р

15 3jтета зн ро

20 сп

сб эл сл

25 (п

N вт

во

вх

430 чт зу ва 1 3А + В 10

Согласно (2) обратный перенос из 0,1-го разряда равен нулю. Согласно значений слагаемых в устройстве возбуждаются соответствующие входы 10 и

4

разряде и на втором входе элемента I-2 через элемент 2-1 ИЛИ устанавливается единичное значение операнда. В ре зультате 8, 1; S, 1, а g,

Ю

О, что и определяет окончание суммирования. На выходе устройства устанавливается код А + В 10 10.

Пусть имеем слагаемые А В 00 2. Тогда согласно (1) и (2) сделанного ранее анализа в 1,1-разряе операндов А и В не может быть единичных значений. При такой комбинации разряде 1,2 срабатывают элементы

1 ИЛИ, 5-1 И и 2-1 ИЛИ. В результа- те на первом и втором входах элемен-, та 1-2 будут установлены единичные, значения операндов, после чего суммирование производится традиционным

способом.

При возникновении структурного сбоя (переход типа О - 1) в любом из элементов схемы или возникновении случайной ошибки во входных цепях

(при равенстве 1 одного из слагаемых,

второй ложно переходит из О в 1)

возможна ситуация, когда на обоих

входах элемента 4-1 И или элемента

42 И появляются единичные сигналы,

что свидетельствует об ошибке. В ре- зультате на выходе 7 будет зафиксирован сигнал ошибки. Аналогично при 1,1 12 срабатывают элементы 32 ИЛИ, 5-2 И и 2-2 ИЛИ.

Формула изобретения Комбинационный сумматор, содержащий в каждом разряде одноразрядный . сумматор, а в каждом четном разряде, кроме того, три элемента И и два эле11 (а g ,bQ, Ьо,7 ai.i ) В результа- 40 мента ИЛИ, причем вход управления рете на выходе 9 одноразрядного сумматора 1-1 будут сформированы значения S д., О и Ро,1 1. В то же время , на первых входах элементов 1-2 и 1,3 появятся единичные сигналы с выхода элемента- 3-1 ИЛИ и входа 10 (а, 1) соответственно. На остальных входах элементов 1-2, 1-3 и 1-4 будут нулевые сигналы. После появления на выходе элемента 1-1 Р, 1 на элементе 1-2 производится подсум- мирование. В результате этого значение прямого переноса с выхода элеменжимом сумматора соединен с первым входом первого элемента И, второй вход которого соединен с входом переноса из (1+2)-го разряда сумматора,

45 где i 1,п, п - разрядность операндов, выход первого элемента И соединен с первыми входами второго элемента И и первого элемента ИЛИ, выход которого соединен с первым информаци50 онным входом одноразрядного сумматора данного разряда, выход которого соединен с выходом результата данного разряда сумматора, входы соответствующих разрядов первого и второго операнта 1-2 Р

0.1

1, а S

о.г

0. Традиционным споеобэм производится подсум- мирование на элементе 1-3. При этом ria третий вход элемента 1-4 поступает единичный сигнал (Р 1, 1). Этим сиг- налом открывается элемент 6 И в 0,2-м

жимом сумматора соединен с первым входом первого элемента И, второй вход которого соединен с входом переноса из (1+2)-го разряда сумматора,

где i 1,п, п - разрядность операндов, выход первого элемента И соединен с первыми входами второго элемента И и первого элемента ИЛИ, выход которого соединен с первым информационным входом одноразрядного сумматора данного разряда, выход которого соединен с выходом результата данного разряда сумматора, входы соответствующих разрядов первого и второго операндов сумматора соединены соответственно с первыми и вторыми входами третьего элемента И и второго элемента ИДИ данного разряда, выход третьего эле-- мента И соединен с вторым В24одом пер513270926

эого элемента ИЛИ, выход второго эле- вькодом ошибки данного разряда сумма- мента ИЛИ соединен с вторым инфррма- тора. ционным входом одноразрядного сумматора данного разряда.отличаю-Таблица

Примечание, i-e значение первого слагаемого в четном j,2-M разряде; bj - i-e значение второго слагаемого в j,2-M разряде; P j + - обратный перенос из (j + l,l)-ro в ),2-й разряд; Р - прямой перенос из j,l-ro разряда; S , j i-e значение суммы в j,2-M разряде; Р ji2 значение переноса в j,2-м разряде.

Составитель М. Есенина Редактор Е. Копча Техред Л.Сердюкова Корректор Н. Король .

. -

Заказ 3390/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.

л п-г -I--..-.- -----.- -- - - -.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Накапливающий сумматор избыточного кода | 1988 |

|

SU1603370A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Изобретение относится к вычислительной технике и может быть испольт зовано при построении помехоустойчи,вых специализированных цифровых систем контроля и регистрации технологических параметров. Цель изобретения - расширение функциональных возможностей за счет суммирования чисел, представленных в ,К,г-кодах при сохране НИИ способности суммирования чисел, представленных в двоичных кодах. Комбинационный сумматор содержит в каждом разряде одноразрядный сумматор 1, а в каждом четном разряде - два элемента ИЛИ 2, 3 и три элемента И 4, 5, 6. 1 ил. 3 табл. (Л оо1C о со to

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-02-07—Подача