1С

CD

00 00

счисления с сохранением работоспособности с числами, представленными в коде Фибоначчи, традиционной двоичной системе счисления и двоичной минимальной единичной системе счисления, а также упрощение сумматора. Комбинационный сумматор содержит в каждом разряде одноразрядный сумматор 1 и логический узел 2, причем

2988

логический узел содержит два элемента И, пять двухвходовьт элементов ИЛИ. Комбинационный сумматор охвачен цепями переноса. В зависимости от системы счисления логический узел формирует сигналы на вход одноразрядного сумматора в соответствии с реализуемыми правилами сложения. 2 ил... 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Устройство для сложения п-разрядных десятичных чисел | 1980 |

|

SU900282A1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Комбинационный сумматор | 1986 |

|

SU1327092A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

Изобретение относится к вычислительной технике и может быть использовано для параллельного суммирования, многоразрядных двоичных чисел в нескольких различных системах счисления. Цель изобретения - расширение функциональных возможностей за счет способности суммировать числа в модифицированной единичной системе

1

Изобретение относится к вычисли- тельной технике и может быть использовано для параллельного суммирования многоразрядных двоичных чисел в нескольких различных системах счисления.

Цель изобретения - расширение функциональных возможностей за счет способности суммировать числа в моди фицированной единичной системе счисления с сохранением работоспособности с числами, представленными в коде Фибоначчи, традиционной двоичной системе счисления и двоичной мини- мальной единичной системе счисления, а также упрощения сумматора.

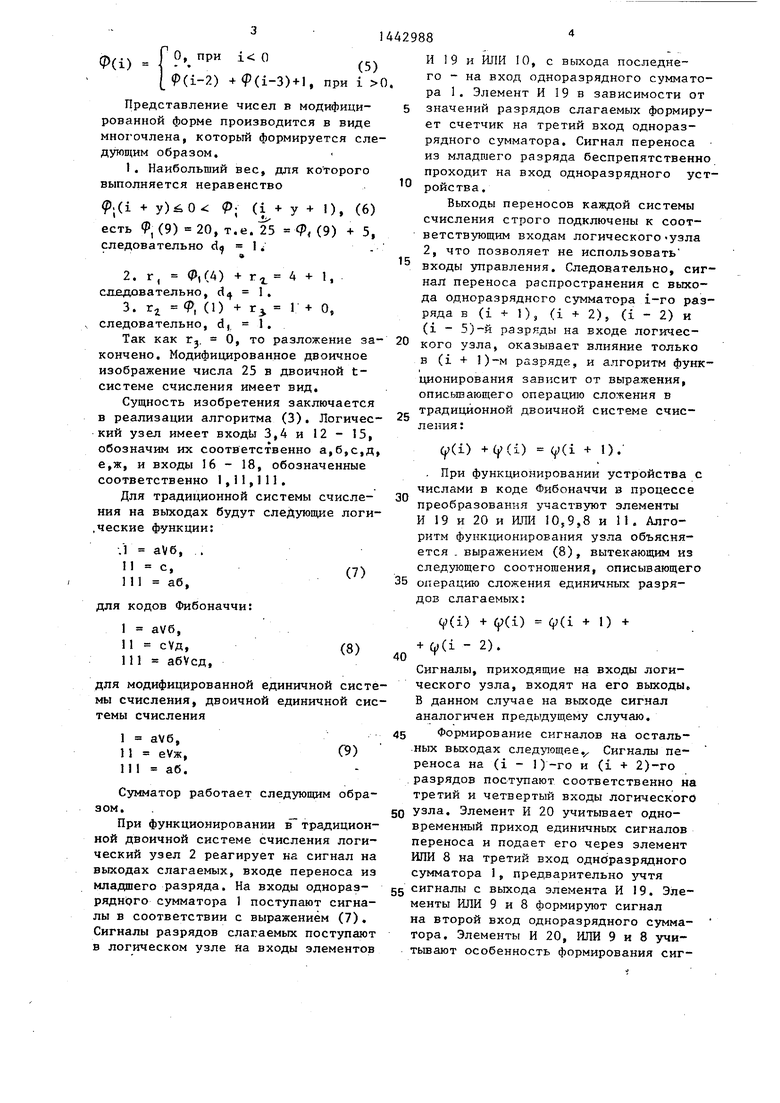

На фиг. I представлена функциональная схема комбинационного сумма™ тора; на фиг. 2 - функциональная . схема логического узла.

Комбинационньй сумматор (фиг, 1) содержит в каждом i-м разряде, где i Ifti, п - разрядность, операндов, одноразрядный сумматор 1, логический узел 2, входы 3 и 4 данного разряда первого и второго операндов, выходы Суммы 5 и переноса 6 данного разряда сумматора.

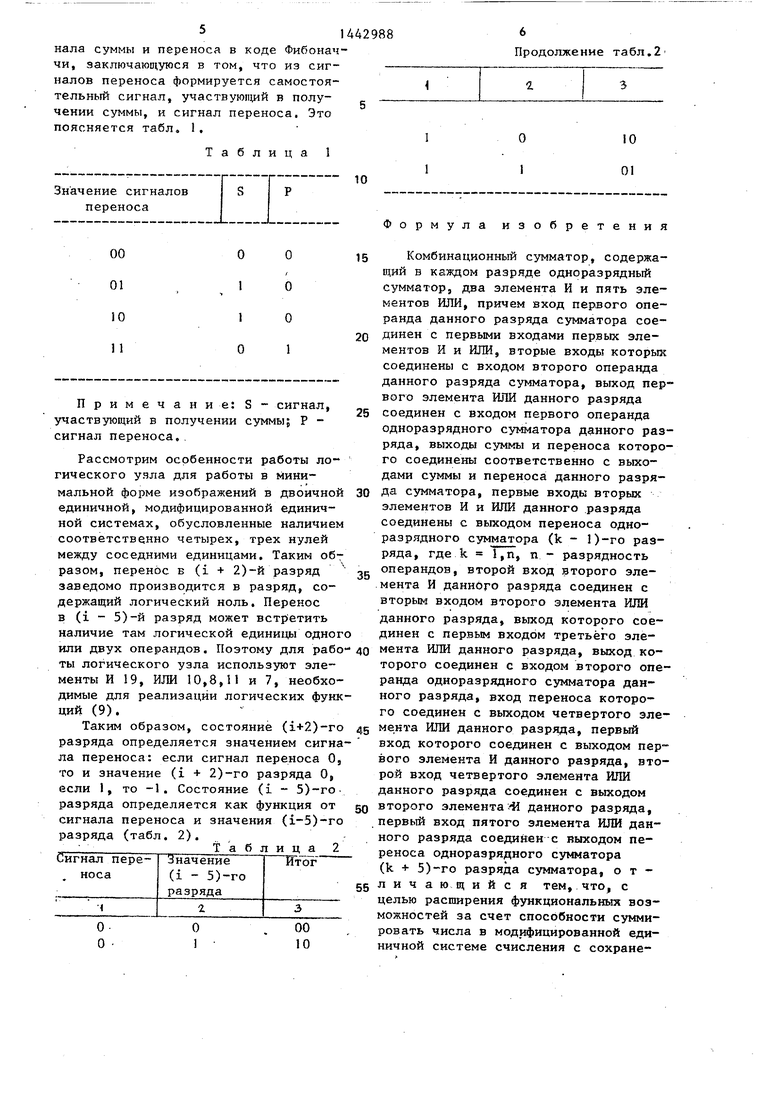

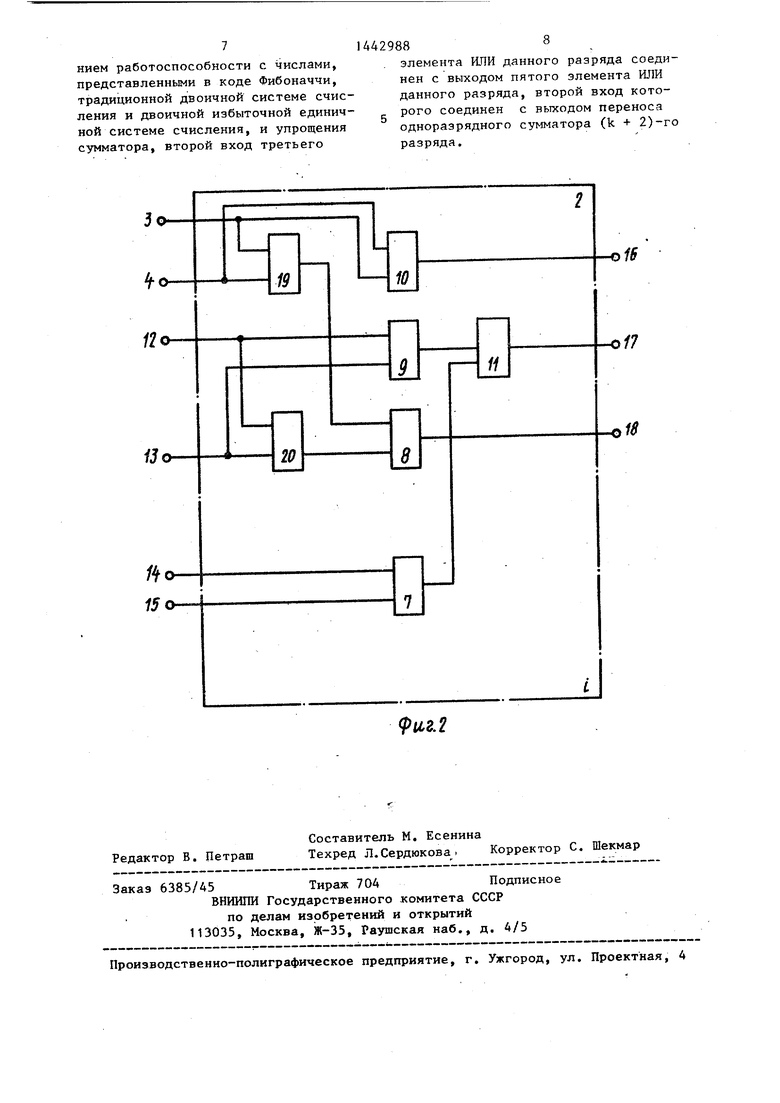

Логический узел (фиг. 2) содержит пять элементов ШШ 7 - 11, входы 12 - 15 переноса соответственно из (i - 1), (i - 2), (i -t- 2) и (i + 5)разрядов сумматора, выходы 16 - 18, элементы И 19 и 20.

Любое натуральное число А в двоичной минимальной системе счисления, представляется в виде многочлена

п

А IIa;t(i),

(1)

1--1

О 5 l.

((i)

где a,j е

0,при i О

1,при 1(2)

((i-2)+C|Jj() при 1 1

Значение (, (п + 1) является мощностью п-разрядного минимального кода

Минимальная система счисления предполагает наличие не менее четырех нулей после логической единигцы. Это вытекает из выражения (2), что определяет обнаруживающие и коррек- тируюш1ие свойства информации, представляемой в этой системе счисления ,

Предлагаемый способ сложения основан на соотношении

9(1) + q)(i) + (f(i 5).

y(i + 2) + (31

Правило сложения, следовательно, имеет вид:

О 1 1 10000001

(4)

Анализ выражения (3) позволяет предположить, что операция будет протекать с появлением промежуточных сумм в ряде случаев.

Представление чисел в двоичной модифицированной единичной системе счисления производится также в виде многочлена, но для, этой цели используется

(i)

О, при i О

(5)

(i-2) +Ф(1-3) + 1, при 1 0.

Представление чисел в модифицированной форме производится в виде многочлена, который формируется следующим образом.

I . Наибольший вес, для ко торого выполняется неравенство

;(i + у)0 Р; ( У 1), (6)

есть Ф, (9) 20, Т.е. 25 Ф, (9) + 5, следовательно dij 1 .

О,

сл довательно, 4

Так как г. О, то разложение закончено. Модифицированное двоичное изображение числа 25 в двоичной t- системе счисления имеет вид.

Сущность изобретения заключается в реализации алгоритма (3). Логический узел имеет входУ 3,4 и 12 - 15, обозначим их соответственно а,б,с,д е,ж, и входы 16 - 18, обозначенные соответственно 1,11,111.

Для традиционной системы счисления на выходах будут следующие логи .ческие функции:

.1 aV6, .

II с,

III аб.

(7)

для кодов Фибоначчи:

I aV6,

II сУд,

III абУсд,

(8)

40

. При функционировании устройства с числами в коде Фибоначчи в процессе преобразования участвуют элементы И 19 и 20 и ИЛИ 10,9,8 и П. Алгоритм функционирования узла объясняется . выражением (8), вытекающим из следующего соотношения, описывающего операцию сложения единичных разрядов слагаемых:

V(i) + 9(1) (V(i + 1) + + ф(1 - 2).

для модифицированной единичной системы счисления, двоичной единичной системы счисления

1 aV6, 1 1 еУж, 111 аб.

Сумматор работает следующим образом.

При функционировании в традиционной двоичной системе счисления логический узел 2 реагирует на сигнал на выходах слагаемых, входе переноса из младшего разряда. На входы одноразрядного сумматора 1 поступают сигналы в соответствии с выражением (7). Сигналы разрядов слагаемых поступают в логическом узле на входы элементов

Сигналы, приходящие на входы логического узла, входят на его выходы. В данном случае на выходе сигнал аналогичен предыдущему случаю. ,. 45 Формирование сигналов на осталь- С9) ных выходах следующее./ Сигналы переноса на (i - 1)-го и (i + 2)-го разрядов поступают соответственно на третий и четвертый входы логического

50 узла. Элемент И 20 учитывает одновременный приход единичных сигналов переноса и подает его через элемент ИЛИ 8 на третий вход одноразрядного сумматора 1, предварительно учтя

55 сигналы с выхода элемента И 19. Элементы ИЛИ 9 и 8 формируют сигнал на второй вход одноразрядного сумматора. Элементы И 20, ИЛИ 9 и В учи- тьшают особенность формирования сиг

ДА2988

И 19 и ИЛИ

.

10

15

20

25

30

35

40

О, с выхода последнего - на вход одноразрядного сумматора 1. Элемент И 19 в зависимости от значений разрядов слагаемых формирует счетчик на третий вход одноразрядного сумматора. Сигнал переноса из млaдDJeгo разряда беспрепятственно проходит на вход одноразрядного устройства.

Выходы переносов каждой системы счисления строго подключены к соответствующим входам логического «узла 2, что позволяет не использовать входы управления. Следовательно, сигнал переноса распространения с выхода одноразрядного сзпчматора i-ro разряда в (i + 1), (i + 2), (i - 2) и (i - 5)-и разряды на входе логического узла, оказывает влияние только в (i + 1)-м разряде, и алгоритм функционирования зависит от выражения, описывающего операцию сложения в традиционной двоичной системе счисления :

((i) +(j;(i) ((i + 1).

. При функционировании устройства с числами в коде Фибоначчи в процессе преобразования участвуют элементы И 19 и 20 и ИЛИ 10,9,8 и П. Алгоритм функционирования узла объясняется . выражением (8), вытекающим из следующего соотношения, описывающего операцию сложения единичных разрядов слагаемых:

V(i) + 9(1) (V(i + 1) + + ф(1 - 2).

51442988

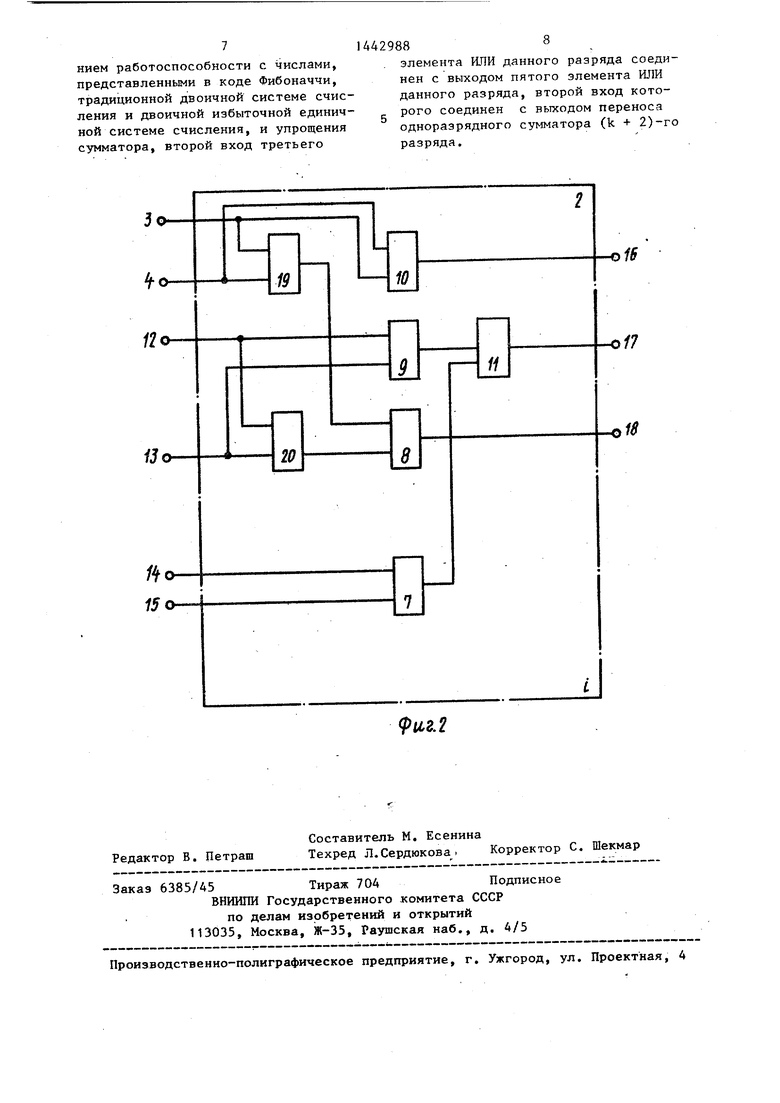

нала суммы и переноса в коде Фибоначчи, заключаюп1утося в том, что из сигналов переноса формируется самостоя- тeльньrt сигнал, участвующий в получении суммы, и сигнал переноса. Это поясняется табл, 1.

1

Таблица

Примечание: S сигнал, участвующий в получении суммы; Р - сигнал переноса..

Рассмотрим особенности работы ло- гического узла для работы в минимальной форме изображений в двоичной единичной, модифицированной единичной системах, обусловленные наличием соответственно четырех, трех нулей между соседними единицами. Таким образом, перенос в (i + 2)-и разряд заведомо производится в разряд, содержащий логический ноль. Перенос в (1 - 5)-и разряд может встретить наличие там логической единицы одного или двух операндов. Поэтому для рабо- ты логического узла используют элементы И 19, ИЛИ 10,8,11 и 7, необходимые для реализации логических функций (9).

Таким образом, состояние (i+2)-ro разряда определяется значением сигна- ла переноса: если сигнал переноса Oj то и значение (i + 2)-го разряда О, если 1, то -1. Состояние (i - 5)-го разряда определяется как функция от сигнала переноса и значения (i-5)-ro разряда (табл. 2).

Таблица 2

Продолжение табл.2

10 01

5

0

25

30 gg 40

45 50

55

Формула изобретения

Комбинационный сумматор, содержащий в каждом разряде одноразрядный сумматор, два элемента И и пять элементов ИЛИ, причем вход первого операнда данного разряда сумматора соединен с первыми входами первых элементов И и ИЛИ, вторые входы которых соединены с входом второго операнда данного разряда сумматора, выход первого элемента ИЛИ данного разряда соединен с входом первого операнда одноразрядного сугшатора данного разряда, выходы суммы и переноса которого соединены соответственно с выходами суммы и переноса данного разряда сумматора, первые входы вторых элементов И и ИЛИ данного разряда соединены с выходом переноса одноразрядного сумматора (k - 1)-го разряда, где k ,п, п - разрядность операндов, второй вход второго элемента И данного разряда соединен с вторым входом второго элемента ИЛИ данного разряда, выход которого соединен с первым входом третьего элемента ИЛИ данного разряда, выход которого соединен с входом второго операнда одноразрядного сумматора данного разряда, вход переноса которого соединен с выходом четвертого элемента ИЛИ данного разряда, первый вход которого соединен с выходом первого элемента И данного разряда, второй вход четвертого элемента ИЛИ данного разряда соединен с выходом второго элемента;41 данного разряда, первый вход пятого элемента ИЛИ данного разряда соединен с выходом переноса одноразрядного сумматора (k + 5)-го разряда сумматора, отличающийся тем, что, с целью расширения функциональных возможностей за счет способности суммировать числа в модифицированной единичной системе счисления с сохранением работоспособности с числами, представленными в коде Фибоначчи, традиционной двоичной системе счисления и двоичной избыточной единичной системе счисления, и упрощения сумматора, второй вход третьего

/20fJo20

14429888

. элемента ИЛИ данного разряда соединен с выходом пятого элемента ИЛИ данного разряда, второй вход которого соединен с выходом переноса одноразрядного сумматора (k + 2)-го разряда.

2

10

-о16

11

-0/7

1$

Риг.2

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-01—Подача