го коммутирующего блока соединен с первым информационным входом первого вычитателя, выход которого соединен с первым информационным входом первого сумматора-вы штателя, информационный выход которого соединен с первым информационным выходом устройства и со входом старшего разряда второго сдвигающего регистра, выход младшего разряда которого соединен со вторым информационным первого вычитателя, информацион ный выход третьего коммутатора соединен с первым информационным входом второго сумматора-вычитателя, информационный выход которого соедич иен со вторым информационным выходом устройства, второй информационный вход второго сумматора-вычитателя соединен с информационным выходом второго вычитателя, выход младшего разряда третьего сдвигающего регист,ра соединен с первым информационным входом третьего сумматора-вычи.татвля, информационный выход которого соединен с третьим информационным выходом устройства и со входом старшего разряда третьего сдвигающего регистра, второй информационный вход третьего сумматора-вычитателя соединен с первым информационным входом угловой константы, разрядные выходы четвертого сдвигающего регистра соединены с группой информационных входов четвертого коммутирующего блока, содержит пятый и шестой сдвигающие регистры, шестой, седьмой, восьмой, девятый коммутирующие блоки, четвертый, пятый, шестой, седьмой , восьмой и девятый суммато)Ывычитатели и элемент И, причем информационный выход первого коммутирующего блока соединен с первым информационным входом первого сумматора, информационный выход которого соединен с четвертым информационным выходом устройства и входом старшего разряда первого сдвигающего регистра, выход младшего разряда четг« вертого сдвигающего регистра соеди нен с первым информационным входом четвертого сумматора-вычитателя, второй информационный вход которого ссединеч с информационным выходом четвертого коммутирующего блока, раз рядные выходы пятого сдвигающего регистра соединены с группами информационных входов пятого и шестого коммутирующих блоков, информационный выход шестого коммутирующего блока соединен со вторым информационным входом первого сумматора-вычитателя, информационный выход пятого коммутирующего блока соединен с первым информационным входом второго вычитателя, второй информационный вход которого соединен с выходом младшего разряда пятого сдвигающего регистра, вход старшего разряда которого соединен с информационным выходом второго сумматора-вычитателя, выход младшего разряда шестого сдвигающего регистра соединен с первым информацИонным входом пятого сумматоравычитателя , второй информационный вход которого соединен с информационным выходом седьмого коммутирующего блока, разр5шные выходы шестого

0 и четвертого сдвигающих регистров соединены с группами информационных входов соответственно седьмого и восьмого коммутирующих блоков, информационные выходы четвертого и

5 пятого сумматоров-вычитателей соединены с первыми информационными входами соответственно шестого и седьмого сумматоров-вычитателей, вторые информационные входы которых соеди0 иены с первыми информационными входами соответственно восьмого и девятого сумматоров-вычитателей и информационными выходами соответственно девятого и восьмого коммутирующих

5 блоков, вторые информационные входы восьмого и девятого сумматоров-вычиТателей соединены с информационными выходами соответственно шестого и седьмого сумматоров-вычитателей, информационные выходы восьмого и девятого сумматоров-вычитателей соединены соответственно с пятым и шестым информационными выходами устройства и со входами старших разрядов соответственно четвертого и

S шестого сдвигающих регистров, разрядные выходы шестого сдвигающего регистра соединены с группами информационных входов девятого коммутирующего блока, знаковые входы первого,

0 второго, шестого и седьмого сумматоров-вычитателей и первый вход элемента И соединены с первым управляющим входом первого операнда устройства, знаковые входы третьего, вось5 мого и девятого сумматоров-вычитателей и второй вход элемента И соединены со вторым управляющим входом второго операнда устройства, знаковые входы четвертого и пятого сумл маторов-вычитателей соединены с вы колом элемента И.

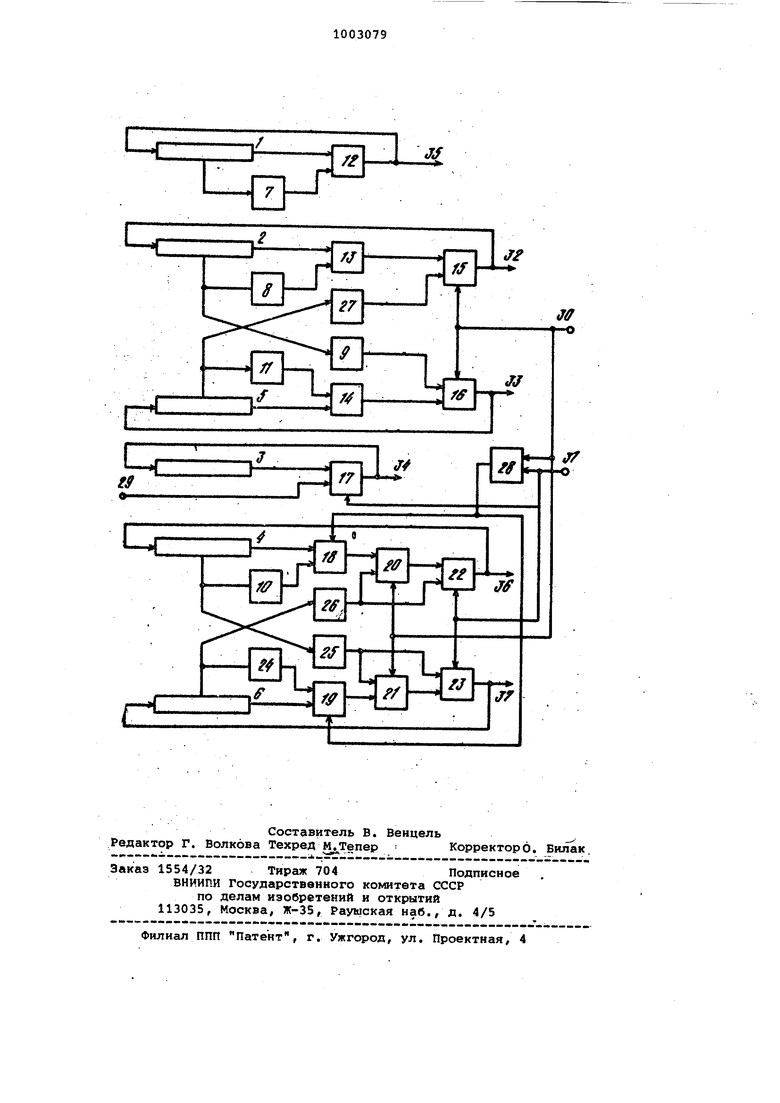

На чертеже показана структурная схема арифметического устройства.

Устройство содержит с первого : по шестой сдвигающие регистры 1, 2,

3, 4, 5 и б, с первого по пятый коммутирующие блоки 7-11, сумматор 12, первый и второй вычитатели 13 и 14, первый-девятый сумматоры-вычитатели 15-23, седьмой-девятый коммутиру0 тощий блоки 24-26, шестой коммутирующий блок 27, элемент И 28, первый информационный вход угловой постоян ной d 29f первый управляющий вход первого оператора устройства 30,

5 второй управляющий вход второго oneратора устройства 31, с первого по шестой информационные выходы устрой ства 32-37. Устройство содержит шесть сдвига ющих регистров, девять коммутирующи блоков, два вычитателя, сумматор и девять суммьторов-вычитателей. Сдви гающий регистр 1 соединен в кольцо с сумматором 12, сдвигающий регистр 2 соединен в кольцо с вычитателем 13 и сумматором-вычитателем 15, сдв гающий регистр 5 соединен в кольцо с вычитателем 14 и сумматором-вычитателем 16, сдвигающий регистр 3 соединен в кольцо с сумматором-вычи тателем 17, сдвигающий регистр 4 соединен в кольцо с сумматорами-вычдтателями 18, 20, 22, сдвигающий регистр б Соединен в кольцо с суммато р.ами-вычитателями 19, 21 и 23. Сдви говые выходы сдвигающих регистров 1 2-,,.5, 4 и б соединены с соответству ющими входами коммутирующих блоков ,,7, 8 и 9, 11 и 27, 10 и 25, 24 и 26 соответственно.Выходы коммутирующих блоков 8 и 11 соединены со вторыми входс1ми вычитателей 13 и 14 соответ ственно, выходы блоков 27, 9 - со вторыми входами сумматоров-вычитате лей 15 и 16 соответственно, выход коммутирующего блока 7 соединен со вторым входом сумматора 12, выходы коммутирующих блоков 10 и 24 соединены со вторыми входами сумматороввычитателей 18 и 19 соответственно, а выходы блоков 2.6 и 25 - со входами сумматоров-вычитателей 20, 22 и 21, 23 соответственно, второй вход сумматора-вычитатеЛя 17 соединен со входом устройства 29. Управляющие входы сумматоров-вычитател.ей 15 , 16 20, 21 и первый вход элемента И 28 соединены со входом устройства для первого оператора, а управляющие входы сумматоров-вычитателей 17, 22 23 и второй вход элемента И 28 со входом устройства для второго оператора. Выход элемента И 28 подключен к управляющим входгм сумматоров-вычитателей 18 и 19. Выходы сум лматора 12 и сумматороввычитателей .15, 16, 17, 22 и 23 йвляются выхода ми устройства 35, 32, 33, 34, 36 и 3.7 соответственно. При вычислении соотношения (1) работу устройства можно onHCiaTb алг ри йом- С yf. .е,42. /xlt,- xt- xt2-t- - а, . - + , а; slgn( ) ), «L- Ьь singe , .-() Y-i- Y.-3.-b;2 + x.a.2 V + x.b ;2Hi- , NV. i,- .. y.a.. -V b, . oi 2arctg , где a и - операторы направления поворота векторов. Исполнительный алгоритм получается из произведения матриц плоского вращения вектора J х, уj . При вычислении соотношения (1 ) задаются следующие начальные условия; .; У, О, х7 с; х. А; z Ч, в; D, При у, -)t О устройство реализует следующие преобразования; у у. cosfarccos-S + DJ + + X einfarccos + DJ, 1 х X и X COS j rccos- + Dj y siniarccos + D Устройство работа ет слегуютим обРазом. Текущие значения х , yJf, г, я х , Уд хранятся в соответствующих регистрах 2, 5,1, 3, 4 и б. С началом очередной итерации по команде из устройства управления коммутирующие блоки соединяют свои выходы с выходами соответствующих сдвигающих регистров так, что на выходах коммутирующих блоков 7, 8, 11, 10 и 24 при сдвиге информации в регистрах появляются операнды, сдвинутые на 2(i-2)-разряда, на выходах коммутирующих блоков 27, 9 - операнды, сдвинутые на {i-3)-р.азряда, а на выходах коммутирующих блоков 26 и 25 операнды, сдвинутые на vi-2)-разряда. На управляющие входы сумматороввычитателей 16, 15, 20 и 21 из устройства управления по входу 30 подается сигнал, соответствующийа|, га управлякияие входы сумматоров-вычитателей 17, 22, 23 - сигнал по входу 31, соответствующий b.j, а на управляющие входы сумматоров-вычитателей 18 и 19 - сигнал, соответствующий произведению , вырабатываемый элементом И 28. В соответствии с сигналов управления сумматоры-вычитатели настраиваются на выполнение итераций по алгоритму J2). При сдвиге информации значение х с-выхода регистра 2 по- ступает на вычитатель 13 , в котором.. из него вычитается величина | поступаюй1а9 с выхода комь утирукчпего блока 8, значение ( ( ) с выхода вычитателя 13 поступ1 ет на вход сумматора-вычитателя 15, в котором в соответствии с а вычитается (суммируется) с , поступаЮ1ЦИМ с выхода коммутируюиего блока 27. Значение х,.;, , получающееся на выходе сумматора-вычитателя 15, поступает на вход регистра 2 для хранения и через выход 32 в устройство управления для определения а,-. ,

Значение у. с выхода регистра 5 поступает на вычитатель.14 ,.в котором вычитается с yf. , поступающим с выхода коммутирующего бло. ка 11, значение (- ) . с выхода вычитателя 14 поступает на вход сумматора-вычитателя 16, в котором в соответствии с а| суммирует ся (вычитается) с , поступающим с выхода коммутирующего блока 9, значение y. , получающееся на выходе сумм4тора-вычитателя 16, поступает на вход регистра 5 для хранения И на выход устройства 33.

Значение z с выхода регистра поступает на сумматор 12, в котором суммируется с (,поступаю1аим с выхода комг«1утирующего блока 7, знчение z|j , получающееся на -выходе сумматора 12, поступает на вход регистра 1 для хранения и через выход 35 в,устройство управления для onpe деления .,) . Текущее значение угла О с выхода регистра 3 поступает на вход сумматора-вычитателя 17, где. в соответствии с Ь из него вычитается (к нему прибавляется) угловая постоянная , поступающая из запом нающего устройства по входу. 29,0,) с выхода сумматрра-вычитателя. 17 записывается в регистр 3 и через выход 34 поступает в устройство управления для определения . .

Одновременно значение х- с выход регистра 4 поступает на сумматорвычитатель 18, в котором, в соответ ствии с произведением а Ь ,вычитается (суммируется) с Х;,- поступающим с первого выхода коммутируютёгб бло ка 10, значение ( с выхода сумматора-вычитртеля 18 поступает на вход сумматора-вычитателя 20, в котором в соответствии с вычитается , (суммируется) с , поступающим с выхода KOMI м тируюыего блока 26 зн.ачение ( х.- - 4 1- У:,.а, 2-ti- r|c выхода. сумматора-вычитателя 20 поступает на вход сумматора-вычитателя 22, в котором в соответствии с вычитается (суммируется) с у ) , поступаюглим с выхода коммутирующего блока 26, значение х,,-4-ц с выхода сумматора-вычитателя 22 поступает на вход регистра 4 для хранения и на выход устройства 36.

Значение с выхода регистра 6 поступает на сумматор-вычитатель 19f в котором в соотйетствии с проиведением вычитается суммируется) , пocтvпaюIttим с выхода коммутирукччего .Рлока 24, значение (у У, я Ь;{ ) свыхода сумматора-вычитателя 19, поступает на

сумматора-вычитателя 21, в котором в соответствии с а суммируется (вычитается) с х:;-2(-2- , VocTynaKHflHM , с выхода коммутирукчгего 5лока 25, значение : V| . Ь. выхода суммматора-вычитателя 21 поступает на вход сумматора-вычитателя 23, в котором в соответствии с Ь,- -суммируется (вычитается) .с , поступающим с выхода коммутирующего блока 25, значение y.,-.,, g выхода сумматора-вычитателя 23 по ступает на вход регистра 6 для хранения и на выход устройства 37. Затем процесс продолжается до

набора заданного числа итераций.

Эффективность изобретения заключается в сокращении времени HHTepno ляции гармочическ го сигнала более, чем в два раза, при увеличении объема оборудования примерно в полтора .раза.

Формула изобретения

Устройство для вычисления тригонометрических функций, содержащ.ее первый, второй, третий и четвертый сдвигающие регистры, первый, второй, третий, четвертый и пятый коммутируЮщие блоки, сумматор, первый и ыторой вычитатели, первый, второй и. третий сумматоры-вычитатели, причем разрядные выходы первого сдвигающего регистра соединены с группой инг

Формаци.онных входов первого коммути-. рующего блока, разрядные выходы второго сдвигающего регистра соединены с группами информационных входов второго и третьего коммутирующих блоков, информационный выход второго

коммутирующего блока соединен с пср--вым информационным входом первого вычитателя, выход которого соединен с первым информационным входом первого сумматора-вычитателя, информационный выход которого соединен с первым информационным выходом устройства и с входом старшего разряда второго сдвигающего регистра, выход мпад1цего разряда которого соединен

5 со вторым информационным входом первого .вычитателя, информационный выход третьего коммутатора соединен с первым информационным входом второго сумматора-вычитателя, информа0 ционный -зыход которого сгоединен со вторым информационным выходом устрой ства, второй информационный вход второго, су1 яиатора-вычитателя соединен с информационным выходом второго вычитателя, выход младшего разряда

третьего сдвигающего регистра соединен с первым информационным входом третьего сумматора-вычитателя, информационный выход которого соединен с третьим информационным выходом устройства и с входом старшего разряда третьего сдвигающего регистра, второй информационный вход третьего сумматора-вычитателя соединен с первым информационным входом угловой константы, разрядные выходы четверто го сдвигающего регистра соединены с группой информационных входов четвертого коммутирующего блока, отличающееся тем, что, с целью повышения быстродействия устройства оно содержит пятый и шестой сдвигающие регистры, шестой, седьмой, восьмой, девятый коммутирующие блоки, четвёртый, пятый, шестой, седьмой, восьмой и девятый сумматоры-вычитатели и элемент И, причем информационный выход -первого комму.тирующе го блока соединен с первым информационным входом первого сумматора, информационный выход которого соеди-- нен с четвертым информационным выходом устройства и входом старшего разряда первого сдвигающего регистра, выход младшего разряда четвертого сдвигаюст.его регистра соединен с первым информационным входом четвертого сумматора-вычитателя, .второй информационный вход которого соединен с информационным вы-ходом четвертого коммутирующего блока, разрядные выходы пятого сдвигающего регистра соединены с группами информационных входов пятого и uiecToro коммутирующих .блоков, информационный выход шестого коммутирующего блока соединен со вторым информационным входом первого сумматора-вычитателя, информационный выход пятого коммутирующего блока соединен г: первым информационным входом гторого вычитателя, второй информационный вход которого соединен с выходом младшего разряда пятого сдвигающего регистра, вход CTapiuero разряда которого соединен с информационным выходом второго сумматора-В1Ычитателя, выход младшего разряда шестого сдвигакяяего регистра соединен с первым информационным входом пятого сумматора-вычитателя, второй информационный вход которого соединен с информационным выходом седьмого коммутирующего блока, разрядные выходы шестого и четвертого сдвигакняих регистров соеди5 нены с группал-ти информационных входов соответственно седьмого и восьт мого коммутирующих блоков, информационные выходы четвертого и пятого сумматоров-вычитателей соединены с

0 первыми информационными входами соответственно шестого и седьмого сумматоров-вычитателей, вторые информационные входы которых соединены с первыми информационными входами со5 ответственно восьмого и девятого сум( маторов-вычитателей и информационными Ъыходами соответственно девятого и восьмого коммутирующих блоков, вторые информационные входы восьмого

0 и девятого сумматоров-вычитателей соединены с информационными выходами соответственно шестого и седьмого с у мма торов - выч итателей, ин формаци о н ные выходы восьмого и девятого сум5 маторов-вычитателей соединены соответственно с пятым и-шестым информационными выходами устройства и с входами старших разрядов соответственно четвертого и шестого сдвигающих регистров, разрядные выходы шестого сдвигающего регистра соединены с группами информа.ционннх входов девятого коммутирующего блока, знаковые входы первого, второго, шестого и седьмого сумматоров-вычи5 тателей и первый вход элемента И соединены с первым управляющим входом первого операнда устройства, знаковые входы третьего, восьмого и девятого сумматоров-вычитателей

0 и второй вход элемента И соединены со вторым управ тяющим входом второго операнда устройства, знаковые входы четвертого и пятого сумматоров-вычитателей соединены с выходом

5 элемента И..

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР Q 697994, нл. G 06 F 7/544, 1976.

2.Авторское свидетельство СССР 445042 кй. С 06 F 7/38, 1973

прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

Авторы

Даты

1983-03-07—Публикация

1981-03-25—Подача