Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях

Цель изобретения - упрощение устройства и повышение точности.

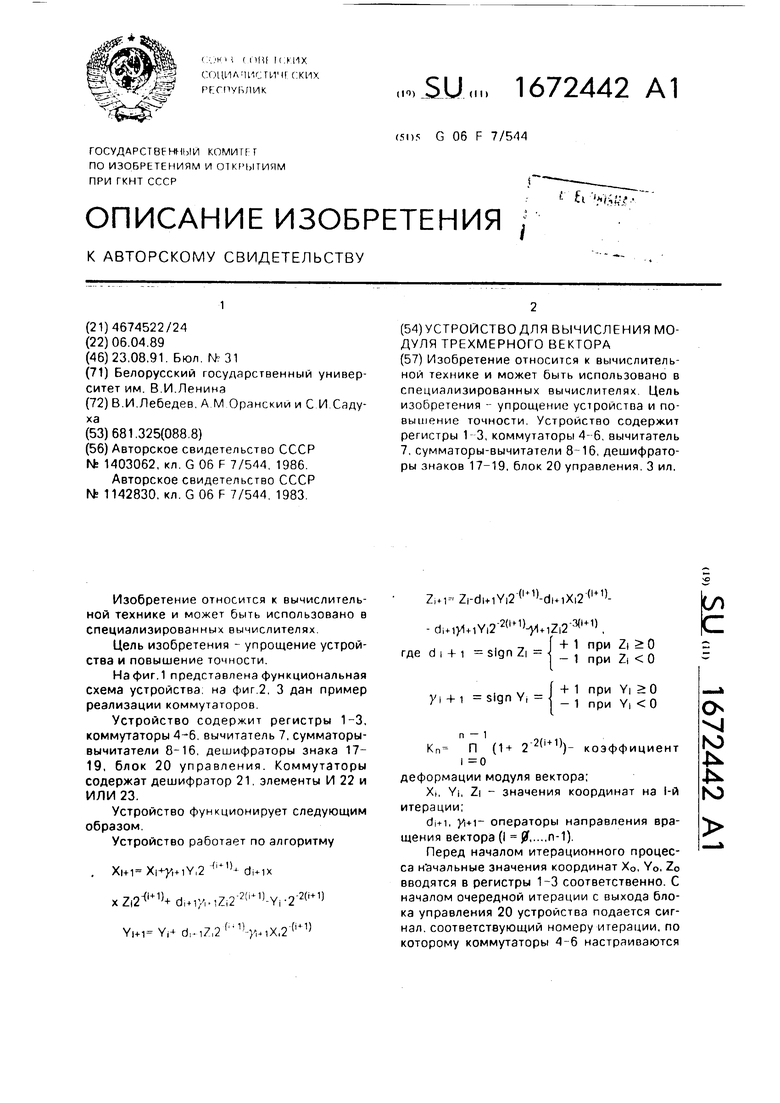

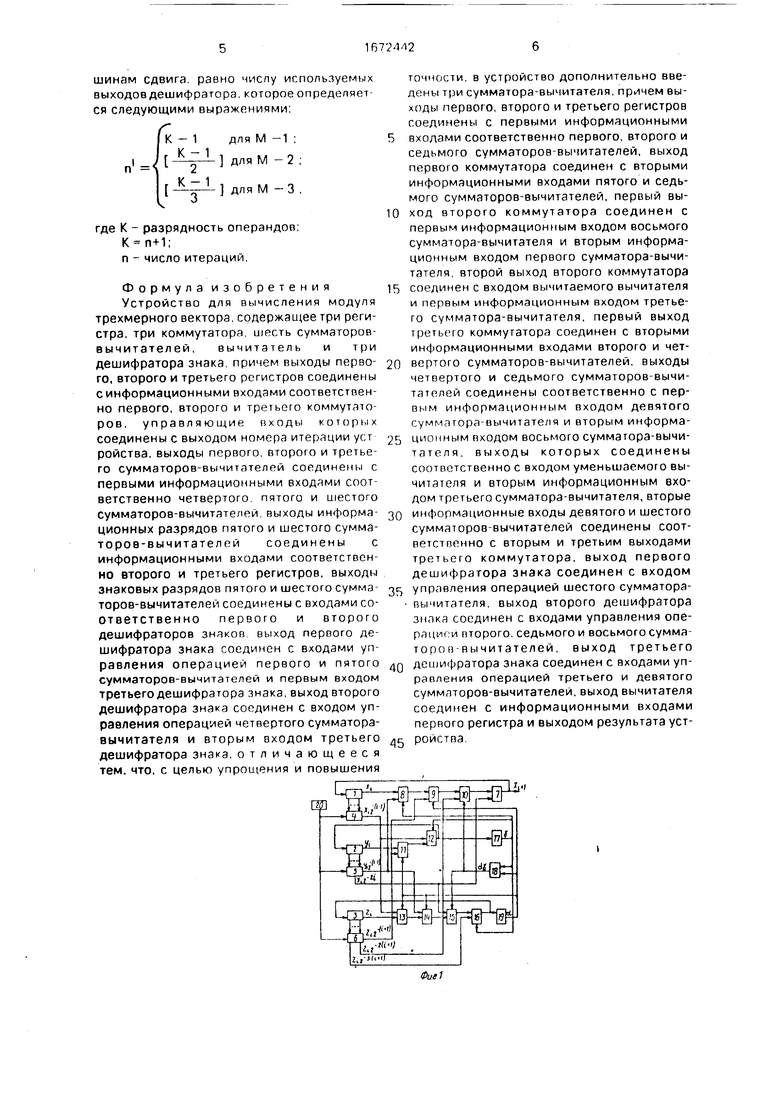

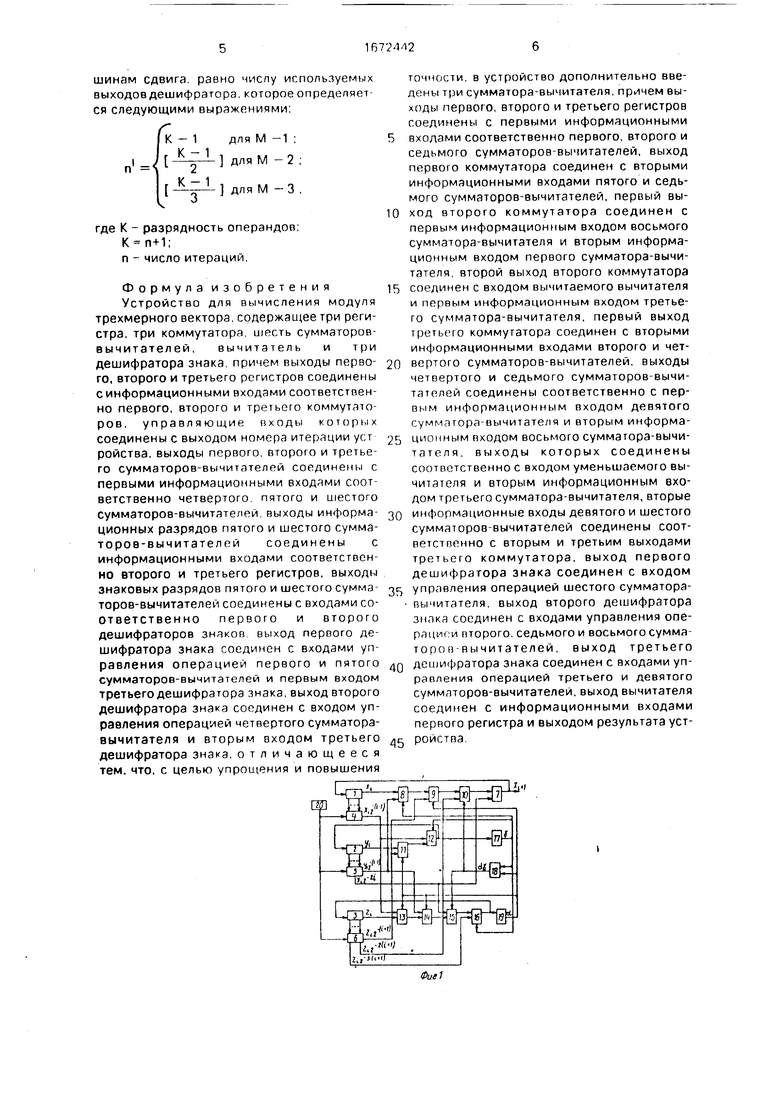

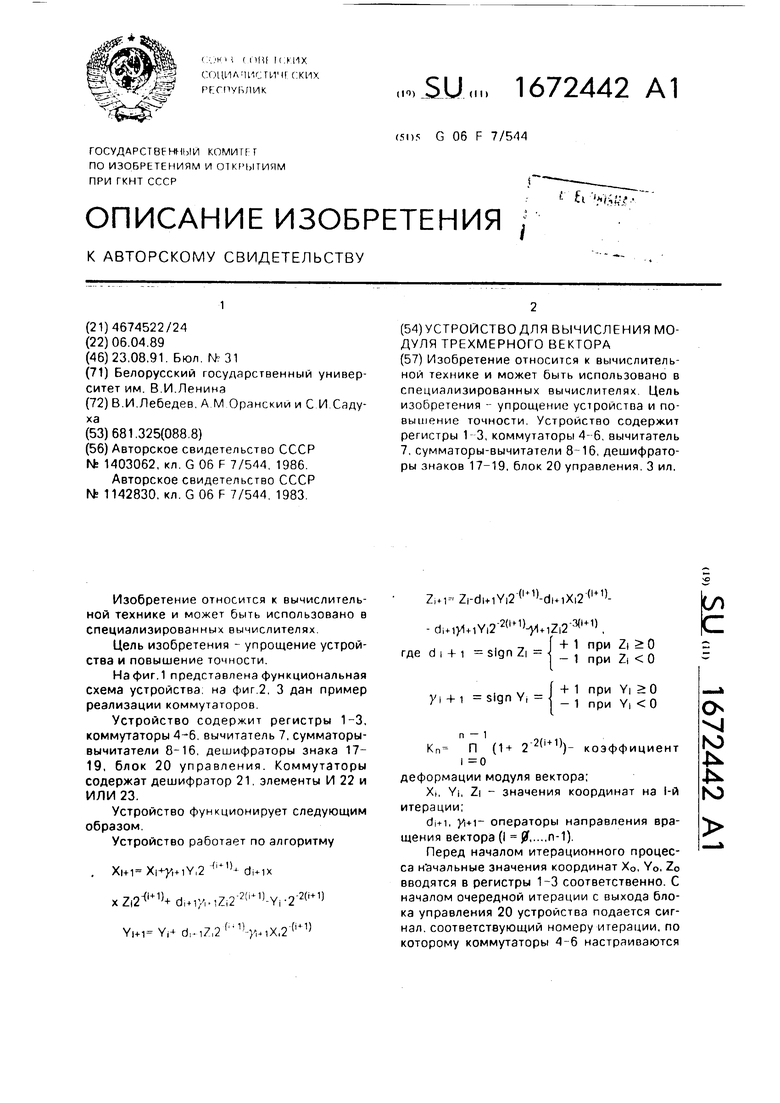

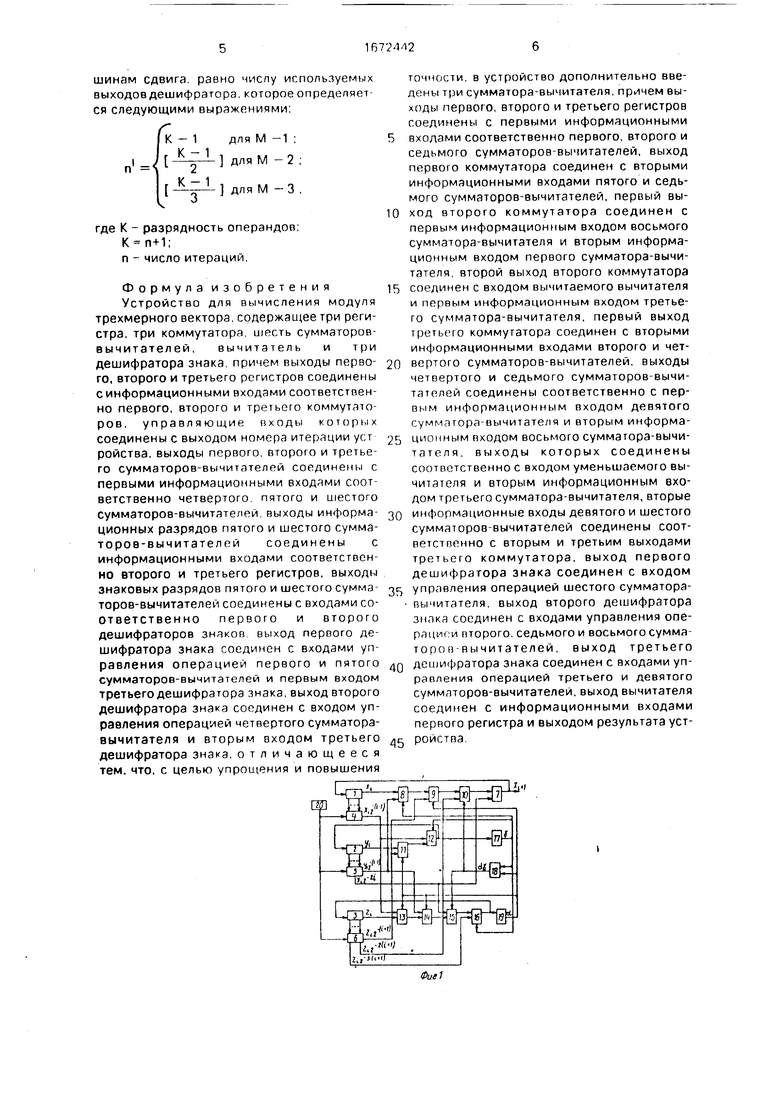

На фиг,1 представлена функциональная схема устройства, на фиг.2, 3 дан пример реализации коммутаторов.

Устройство содержит регистры 1-3, коммутаторы 4-6. вычитатель 7, сумматоры- вычитатели 8-16, дешифраторы знака 17- 19, блок 20 управления. Коммутаторы содержат дешифратор 21. элементы И 22 и ИЛИ 23.

Устройство функционирует следующим образом.

Устройство работает по алгоритму

. Хц-1 Xi+r,+ iY,2 {l d.-нх

,1 Yi+i Y,+ d,-i,,)

Z,Zrd,+ iY,)-dKiX,2(l+1)- - d yl+iY ViZ.2-3 ,

где d i + 1 sign Zi

J + 1 при Zi 0 - 1 при Z( 0

fe

yi 4-1 sign Y, | 1

j + 1 при Yi 0 при YI 0

i

Kn П (1+ (l+1))- коэффициент

i 0 деформации модуля вектора;

X,, Yi, Zi - значения координат на 1-й итерации;

di+i, yi+i операторы направления вращения вектора (I )

Перед началом итерационного процесса начальные значения координат Хо, Yo, Zo вводятся в регистры 1-3 соответственно. С началом очередной итерации с выхода блока управления 20 устройства подается сигнал, соответствующий номеру итерации, по которому коммутаторы 4-6 настраиваются

О

VJ

ю

N ю

Таким образом, чтобы с их первого выхода снималось число (Xi, Yi, Zi), сдвинутое на i+1 разрядов, со второго выхода коммутаторов 5 и 6- на 2(1+1) разрядов, а с третьего выхода коммутатора 6- на 3(1+1) разрядов. При этом на выходе суммэтора-вычитателя 8 получается значение Xi+yi+iYi2 , на выходе сумматора-вычитателя 9 - значение Xi-t yi + i Yj2() + di+iZi2(i+1). на выходе сумматора-вычитателя 10 - значение Xi+ r,+ iY,2-(IH)+ di+iZ,2-(l+1)+ dUiyi+iZi2-2(i+1)n на выходе вычитателя 7 получается значение Хм, которое записывается в регистр 1 вместо числа Х|. Аналогично на выходах сум- маторов-вычитателей 12 и 16 получаются значения YH-I и Zi+i, которые записываются в регистры 2 и 3, а также на входы дешифраторов 17 и 19, где вырабатываются знаки операторов поворота ум и di-м соответственно. Дешифратор 18 служит для определения знака произведения операторов di-t-i yi+1. по которому сумматоры-вычитате- ли 10 и 15 настраиваются на выполнение операции сложения и вычитания соответственно. После выполнения п итераций исходный вектор совпадает с осью X. а в регистре 1 записывается значение

Хп К X2+Y2+Z2, где К П (1+ (i+1)) - коэффициент

i 0

деформации модуля вектора.

Схема коммутатора 6 приведена на фиг.2. В его состав входит дешифратор 21. элмент И 22, элемент ИЛИ 23. На входы Zi коммутатора поступает код операнда Zi из регистра 3 (1-й разряд является старшим), а на входы jfo qoqTn, qm) код номера итерации i (i 0, п-1) из счетчика итераций (блока 20 устройства). При возбуждении соответствующей номеру итерации выходной шины Wj(,n) дешифратора на входах 1 коммутатора имеем код числа . на выходах 2 - Z,), на выходах 3 - Z,2-3(M) Пе- ред началом итерационного процесса в устройстве на входы дешифратора подается из счетчика итераций код числа N, отличного от номера итерации i, например N п. В этом случае ни одна из шин щ дешифратора не возбуждена и на выходах 1 - 3 коммутатора имеем код числа ноль. Аналогичным образом работают и коммутаторы 4 и 5 устройства. Однако первый из них содержит лишь выходы 1 (и соответствующие им элементы И, ИЛИ), а второй - выходы 1 и 2 (и соответствующие им элементы И, ИЛИ). В устройстве достаточно использовать дешифратор, общий для всех трех коммутаторов 4-6. Если элементы И допускают

объединение выходов по схеме МОНТАЖНОЕ ИЛИ, то логические элементы ИЛИ в схеме отсутствуют. Пример построения такого коммутатора для 10-разрядных операндов Zi приведен на фиг.З. Коммутатор конструктивно представляет собой комплекс треугольных матриц, в которых пересечения горизонтальных и вертикальных шин образуются из однотипных эоементов, реа0 лизующих логическую операцию И. Количество разрядных (горизонтальных) шин определяется разрядностью сдвиговых операций: в матрице М-1 не используется одна шина (младший разряд Zi), в М-2 не исполь5 зуются два младших разряда, а в М-3 - соответственно три младших разряда. Элементы И представляют собой транзисторы, эмиттеры которых объединяются выходными разрядными шинами. Аналогично

0 вертикальные шины объединяют базы транзисторов вертикальной группы элементов И. Диагональные шины матриц объединяют коллекторы соответствующих (диагонально расположенных) элементов И и присоединяются

5 к разрядным шинам входного операнда Zi.

Коммутатор работает следующим образом.

При подаче с дешифратора сигнала MI отпираются по базовым цепям транзи0 сторы первого вертикального ряда элементов И, что обеспечивает появление на выходных разрядных шинах значений Z02 , , матриц М-1, М-2 и М-3 соответственно. При появлении сигнала Ш2 на следу5 ющей шине дешифратора отпираются транзисторы второго вертикального ряда элементов И. а на выходных шинах матриц появляются очередные значения Zi2 ,Zi2 , . Последний сигнал сдвига (для матри0 цы М-1 на 9-й шине од дешифратора) открывает последний элемент И. На выходной шине 10-го (младшего) разряда фиксируется старший разряд числа Zg, что соответствует величине . С прекращением

5 действия этого сигнала запирается элемент И, а на вгех выходных разрядных шинах фиксируются нулевые состояния, что в данном случае для десятиразрядного операнда соответствует Zg2 . Аналогичные операции

0 происходят и в матрицах М-2 и М-3. Для М-2 с приходом сигнала на шину сдвига ом на выходах девятого и десятого разрядов фиксируются значения 1-го и 2-го разрядов числа Z4, а на десятой выходной шине М-3 при

5 наличии сигнала на третьей сдвиговой шине первый (старший) разряд числа Za фиксируется на 10-м разряде выходных шин. Такие состояния матриц соответствуют для М-2 и для М-3. Количество вертикаль- ных групп элементов И, объединенных по

шинам сдвига, равно числу используемых выходов дешифратора, которое определяется следующими выражениями:

п

К - 1для М -1 ;

г К - 1

для М - 2 ;

ДляМ -3.

где К - разрядность операндов; К п+1; п - число итераций.

Формула изобретения Устройство для вычисления модуля трехмерного вектора, содержащее три регистра, три коммутатора, шесть сумматоров- вычитателей, вычитатель и три дешифратора знака, причем выходы первого, второго и третьего регистров соединены синформационными входами соответственно первого, второго и третьего коммутаторов, управляющие входы которых соединены с выходом номера итерации уст ройства, выходы первого, второго и третьего сумматоров-вычитателей соединены с первыми информационными входами соответственно четвертого, пятого и шестого сумматоров-вычитателей. выходы информационных разрядов пятого и шестого сумматоров-вычитателей соединены с информационными входами соответственно второго и третьего регистров, выходы знаковых разрядов пятого и шестого сумматоров-вычитателей соединены с входами со- ответственно первого и второго дешифраторов знаков выход первого дешифратора знака соединен с входами управления операцией первого и пятого сумматоров-вычитателей и первым входом третьего дешифратора знака, выход второго дешифратора знака соединен с входом управления операцией четвертого сумматора- вычитателя и вторым входом третьего дешифратора знака, отличающееся тем, что. с целью упрощения и повышения

точности, в устройство дополнительно введены три сумматора-вычитателя, причем выходы первого, второго и третьего регистров соединены с первыми информационными

входами соответственно первого, второго и седьмого сумматоров-вычитателей, выход первого коммутатора соединен с вторыми информационными входами пятого и седьмого сумматоров-вычитателей, первый выход второго коммутатора соединен с первым информационным входом восьмого сумматора-вычитателя и вторым информационным входом первого сумматора-вычитателя. второй выход второго коммутатора

соединен с входом вычитаемого вычитателя и первым информационным входом третьего сумматора-вычитателя, первый выход третьего коммутатора соединен с вторыми информационными входами второго и четвертого сумматоров-вычитателей, выходы четвертого и седьмого сумматоров-вычитателей соединены соответственно с первым информационным входом девятого суммагора-вычитателя и вторым информационным входом восьмого сумматора-вычи- тателя, выходы которых соединены соответственно с входом уменьшаемого вычитателя и вторым информационным входом третьего сумматора-вычитателя, вторые

информационные входы девятого и шестого сумматоров-вычитателей соединены соответственно с вторым и третьим выходами третьего коммутатора, выход первого дешифратора знака соединен с входом

управления операцией шестого сумматора- вычитателя, выход второго дешифратора знака соединен с входами управления операцией второго, седьмого и восьмого сумма- торов-вычитателей, выход третьего

дешифратора знака соединен с входами управления операцией третьего и девятого сумматоров-вычитателей, выход вычитателя соединен с информационными входами первого регистра и выходом результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство | 1988 |

|

SU1522196A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 2004 |

|

RU2268482C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Цель изобретения - упрощение устройства и повышение точности. Устройство содержит регистры 1 - 3, коммутаторы 4 - 6, вычитатель 7, сумматоры-вычитатели 8 - 16, дешифраторы знаков 17 - 19, блок 20 управления. 3 ил.

ptMfrp

t

гч

Bbix T(Zi2-3a J))

л -

40 I I

ff-o

N31

HI

1-1

s

5

См

Ј

No

VJ

fsa

к 1

&1

NO

.-2(ZL2 2Utl))

Зых Г(1;2-а))

if

От дш

п-з

-3114)

| Устройство для преобразования координат вектора в трехмерном пространстве | 1986 |

|

SU1403062A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-04-06—Подача