1

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах, выполняющих операции десятичной арифметики .

Цель изобретения - сокращение количества оборудования устройства.

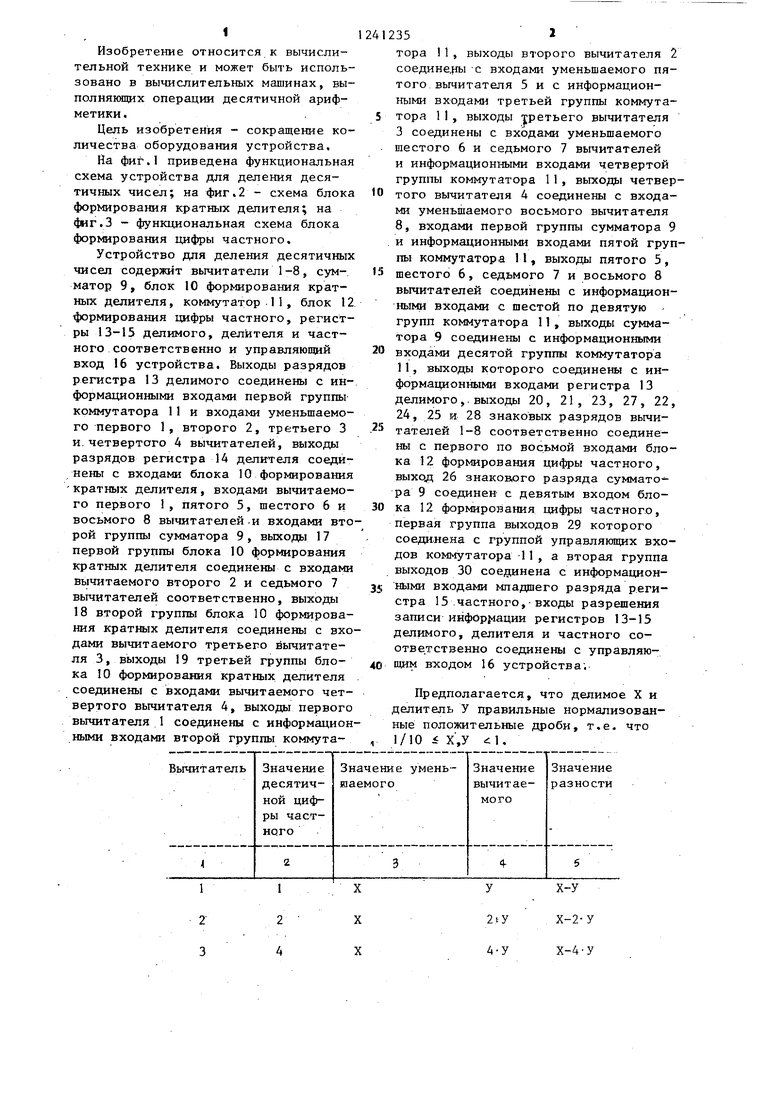

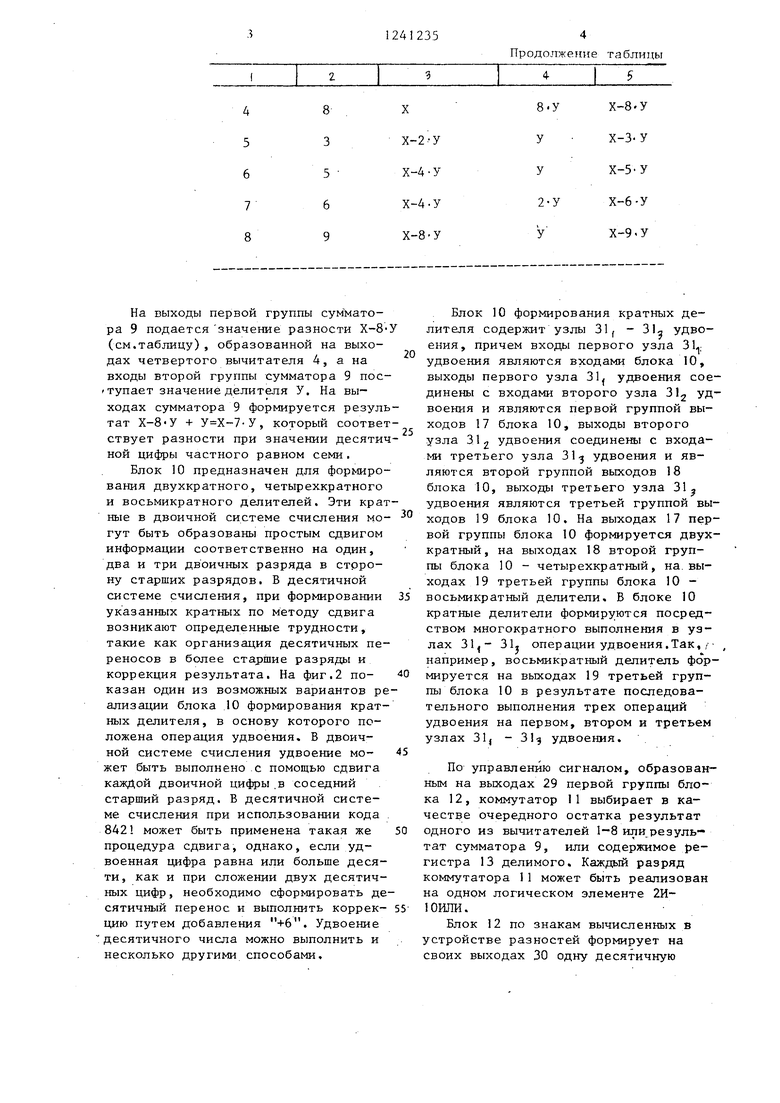

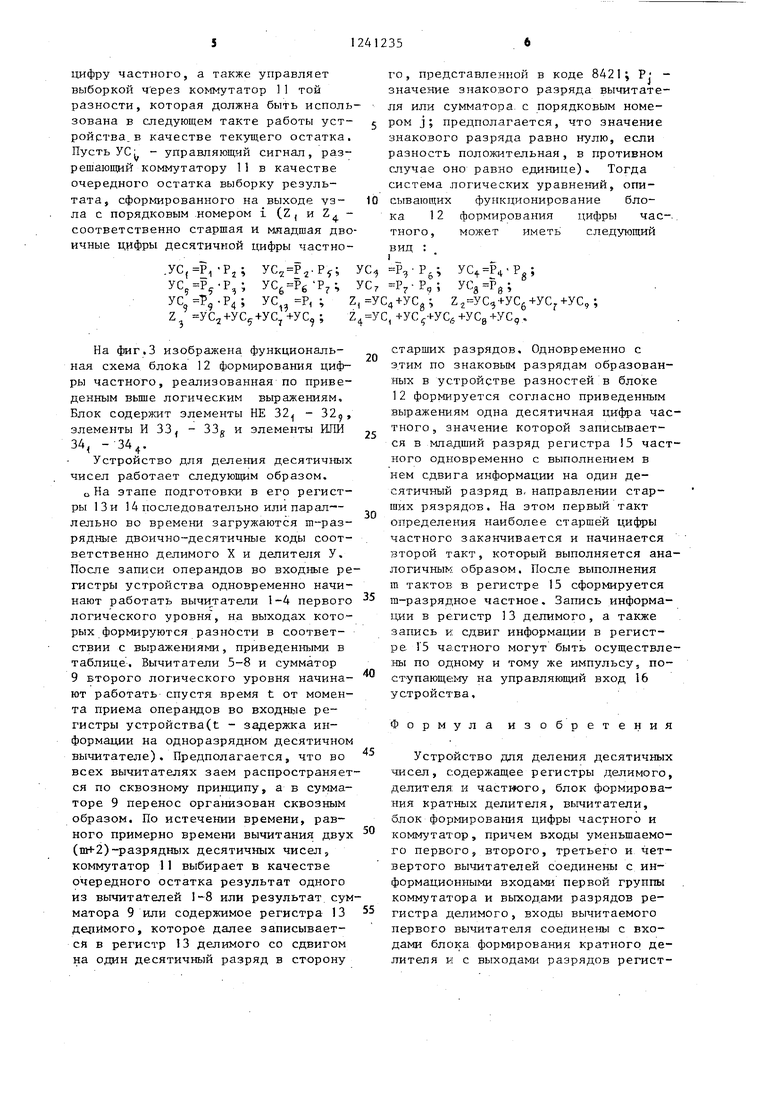

На фиг.1 приведена функциональная схема устройства для деления десятичных чисел; на фиг.2 - схема блока формирования кратных делителя; на 4нг.З - функциональная схема блока формирования цифры частного.

Устройство для деления десятичных чисел содержит вычитатели 1-8, сум-, матор 9, блок 10 формирования кратных делителя, коммутатор.11, блок 12 формирования цифры частного, регистры 13-15 делимого, делителя и частного соответственно и управляющий вход 16 устройства. Выходы разрядов регистра 13 делимого соединены с информационными входами первой группы- коммутатора 11 и входами уменьшаемого первого 1, второго 2, третьего 3 и. четвертого 4 вычитателей, выходы разрядов регистра 14 делителя соединены с входами блока 10 формирования Кратных делителя, входами вычитаемого первого , пятого 5, шестого 6 и восьмого 8 вычитателей -и входами второй группы сумматора 9, выходы 17 первой группы блока 10 формирования кратных делителя соединены с входами Вычитаемого второго 2 и седьмого 7 вычитателей соответственно, выходы 18 второй группы блока 10 формирования кратных делителя соединены с входами вычитаемого третьего вычитате- ля 3, выходы 19 третьей группы блока 10 формирования кратных делителя соединены с входами вычитаемого четвертого вычитателя 4, выходы первого вычитателя 1 соединены с информационными входами второй группы коммута20

41235

тора 1, выходы второго вычитателя 2 соедине, -с входами уменьшаемого пятого вычитателя 5 и с информационными входами третьей группы коммута5 тора II, выходы ретьего вычитателя

3 соединены с входами уменьшаемого . шестого 6 и седьмого 7 вычитателей и информацион л 1ми входами четвертой группы коммутатора 11, выходы четвер10 того вычитателя 4 соединены с входами уменьшаемого восьмого вычитателя 8, входами первой группы сумматора 9 и информационными входами пятой группы коммутатора 11, выходы пятого 5,

5 шестого 6, седьмого 7 и восьмого 8 вычитателей соединены с информационными входами с шестой по девятую групп коммутатора 11, выходы сумматора 9 соединены с информационными входами десятой группы коммутатора 11, выходы которого соединены с информационными входами регистра 13 делимого,.выходы 20, 21, 23, 27, 22, 24, 25 и 28 знаковых разрядов вычитателей 1-8 соответственно соединены с первого по восьмой входами блока 12 формирования цифры частного, выход 26 знакового разряда сумматора 9 соединен с девятым входом бло30 ка 12 формирования цифры частного, первая группа выходов 29 которого соединена с группой управляющих входов коммутатора -11 , а вторая группа выходов 30 соединена с информацион35 ными входами младшего разряда регистра 15 .частного,-входы разрешения записи инфОр14ации регистров 13-15 делимого, делителя и частного соответственно соединены с управляю40 щим входом 16 устройства;

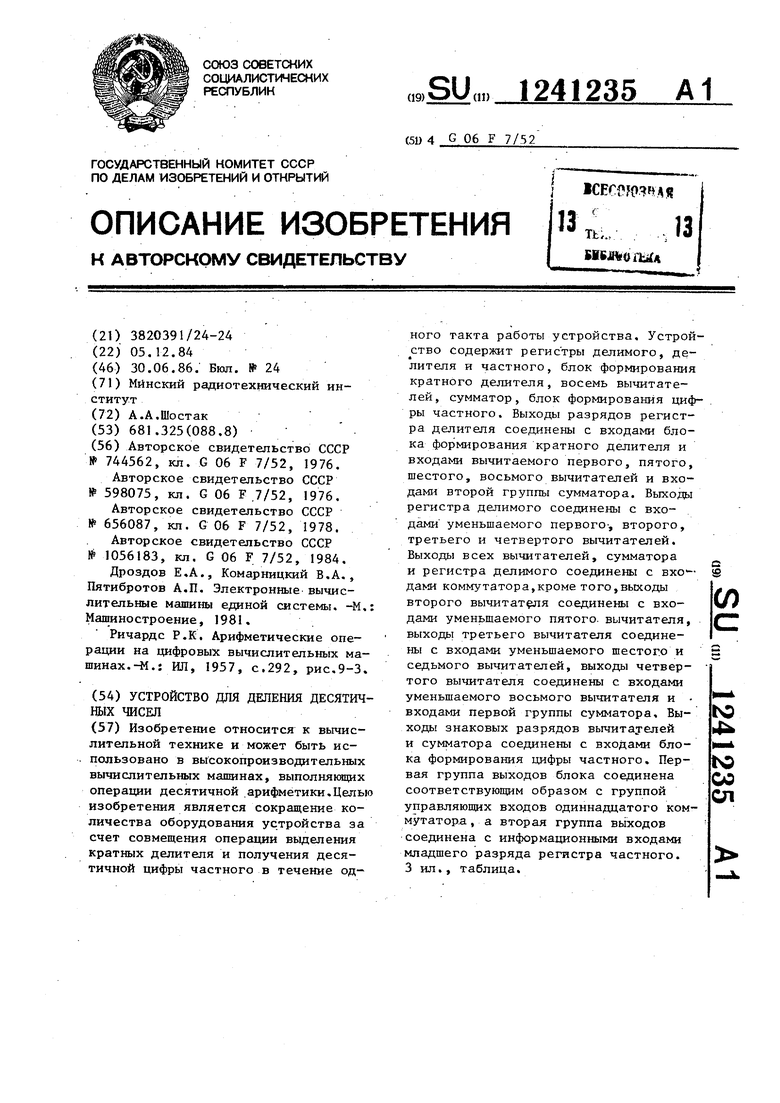

Предполагается, что делимое X и делитель У правильные нормализованные положительные дроби, т.е. что , 1/10 i Х,У 1.

25

20

25

35

На выходы первой группы сумматора 9 подается значение разности Х-8 У (см.таблицу), образованной на выходах четвертого вычитателя 4, а на входы второй группы сумматора 9 пос- Тупает значение делителя У. На выходах сумматора 9 формируется результат Х-8 У + У Х-7-У, который соответствует разности при значении десятичной цифры частного равном семи.

БЛОК 10 предназначен для формирования двухкратного, четырехкратного и восьмикратного делителей. Эти кратные в двоичной системе счисления мо- гут быть образованы простым сдвигом информации соответственно на один, два и три двоичных разряда в стрро- ну старших разрядов. В десятичной системе счисления, при формировании указанных кратных по методу сдвига возникают определенные трудности, такие как организация десятичных переносов в более старшие разряды и коррекция результата. На фиг.2 показан один из возможных вариантов реализации блока 10 формирования кратных делителя, в основу которого положена операция удвоения. В двоичной системе счисления удвоение моет быть выполнено .с помощью сдвига каждой двоичной цифры.в соседний старший разряд. В десятичной систее счисления при использовании кода 842 может быть применена такая же процедура сдвига, однако, если удвоенная цифра равна или больше десяти, как и при сложении двух десятичных цифр, необходимо сформировать десятичный перенос и выполнить коррек- 55 ию путем добавления +6. Удвоение есятичного числа можно выполнить и несколько другими способами.

40

45

50

Продолжение таблицы

20

25

35

5

40

5

0

Блок 10 формирования кратных делителя содержит узлы 31, 31 удвоения, причем входы первого узла 31,. удвоения являются входами блока 10, выходы первого узла 31 удвоения соединены с входами второго узла 312 УД воения и являются первой группой выходов 17 блока 10, выходы второго узла 312 удвоения соединены с входами третьего узла 31 удвоения и являются второй группой выходов 18 блока 10, выходы третьего узла 31 удвоения являются третьей группой выходов 19 блока 10, На выходах 17 первой группы блока 10 формируется двухкратный, на выходах 18 второй группы блока 10 - четырехкратный, на. выходах 19 третьей группы блока 10 - восьмикратный делители. В блоке 10 кратные делители формируются посредством многократного выполнения в узлах 31,- 31, операции удвоения.Так,/ , например, восьмикратный делитель формируется на выходах 19 третьей группы блока 10 в результате последовательного выполнения трех операций удвоения на первом, втором и третьем узлах 31, 31-) удвоения.

По управлению сигналом, образованным на выходах 29 первой группы блока 12, коммутатор 11 выбирает в качестве очередного остатка результат одного из вычитателей 1-8 или результат сумматора 9, или содержимое регистра 13 делимого. Каждый разряд коммутатора 11 может быть реализован на одном логическом элементе 2И- 1ОИЛИ.

Блок 12 по знакам вычисленных в устройстве разностей формирует на своих выходах 30 одну десятичную

цифру частного, а также управляет выборкой ч ерез коммутатор 1 1 той разности, которая должна быть использована в следующем такте работы уст- ройртва,в качестве текущего остатка. Пусть УС; - управляющий сигнал, разрешающий коммутатору 11 в качестве очередного остатка выборку результата, сформированного на выходе узла с порядковым номером i (Z, и Z - соответственно старшая и мяадшая двоичные цифры десятичной цифры частноГ Р Р ( LI 2

Р,;

.Р

f 9

УС,Рб Р,

t

.р4; УС р, ,

УС,г+УС5+УС +УС ;

УС УС,

вид : I -р

i -л

Р Э 6- -Р . Р

h +УС

yc,

1) 1

УСп

Z, -УС

, +УС -ьУСй+УС,

8

g;

На фиг.З изображена функциональная схема блока 12 формирования цифры частного, реализованная по приведенным вьше логическим выражениям. Блок содержит элементы НЕ 32 - 32, элементы И 33 - 33g и элементы ИЛИ 34, --34,.

Устройство для деления десятичных чисел работает следующим образом.

о На этапе подготовки в его регистры 13и 14 последовательно или парал- лельно во времени загружаются ш-раз- рядные двоично-десятичные коды соответственно делимого X и делителя У. После записи операндов во входные регистры устройства одновременно начинают работать вычи/гатели 1-4 первого логического уровня , на выходах которых формируются разности в соответствии с выражениями, приведенными в таблице. Вычитатели 5-8 и сумматор 9 второго логического уровня начинают работать спустя время t от момента приема операндов во входные регистры ycтpoйcтвa(t - задержка информации На одноразрядном десятичном вычитателе). Предполагается, что во всех вычитателях заем распространяется по сквозному принципу, а в сумматоре 9 перенос организован сквозным образом. По истечении времени, равного примерно времени вычитания двух (пН-2)-разрядных десятичных чисел, коммутатор 11 выбирает в качестве очередного остатка результат одного из вьгчитателей 1-8 или результат сумматора 9 или содержимое регистра 13 де химого, которое далее записывается в регистр 13 делимого со сдвигом на один десятичный разряд в сторону

10

С С,

го, представленной в коде 8A2I; - значение знакового разряда вычитате- ля или сумматора, с порядковым номером J; предполагается, что значение знакового разряда равно нулю, если разность положительная, в противном случае оно равно единице), Тогда система логических уравнений, описывающих функционирование блока 12 формирования цифры час-., тного, может иметь следующий

вид : I -р

i -л

Р Э 6- -Р . Р

h +УС

yc,p,.pg;

1) 1

УСп Р

-УС

yC, +УС -ьУСй+УС,

8 в

g; ,;

+УС,

старших разрядов. Одновременно с этим по знаковым разрядам образованных в устройстве разностей в блоке 12 форми:руется согласно приведенным выражени.ям одна десятичная цифра частного, значение которой записывается в младший разряд регистра 15 частного одновременно с выполнением в нем сдвига информации на один десятичный разряд в, направлении старших рязрядов. На этом первый такт определения наиболее старшей цифры частного заканчивается и начинается второй такт, который выполняется аналогичным образом. После выполнения m тактов в регистре 15 сформируется т-разрядное частное. Запись информации в рб .гистр 3 делимого , а также запись и сдвиг информации в регистре 5 частного могут быть осуществле- ;ны по одному и тому же импульсу, поступающему на управляющий вход 16 устройства.

Формула изобретения

Устройство для деления десятичных чисел, содержа.щее регистры делимого, делителя; и частного, блок формирования кратнь1х делителя, вьгчитатели, блок формирования цифры частного и коммутатор, причем входы уменьшаемого первого, второго, третьего и четвертого вычитателей соединены с информационными входами первой группы коммутатора и выходами разрядов регистра делимого, входы вычитаемого первого вычитателя соединены с входами блока формирования кратного делителя и с выходами разрядов регистpa делителя, входы вычитаемого второго, третьего и четвертого вычита- телей соединены с выходами первой, второй и третьей групп блока форми- рования кратных делителя соответственно , выходы вычитателей с первого по восьмой соединены с информационными входами с второй по девятую групп коммутатора соответственно, вы ходы которого соединены с информационными входами регистра делимого, выходы знаковых разрядов с первого по восьмой вычитателей соединены с первого по восьмой входами блока фор мирования цифры частного соответственно, первая группа выходов которого соединена с группой управляющих входов коммутатора, а вторая группа выходов соединена с информационными входами младшего разряда регистра частного, входы разрешения записи информации регистров делимого, делителя и частного соединены с управляющим входом устройства, о т л и ч а- ю щ е е с я тем, что, с целью сокращения объема оборудования, входы уменьшаемого пятого вычитателя соединены с выходами второго вычитателя входы уменьшаемого шестого .вычитате- ля соединены с входами уменьшаемого

седьмого вычитателя и выходами треть его вычитателя входы уменьшаемого восьмого вычитателя соединены с входами первой группы сумматора и выхо- дами четвертого выЕШтателя, входы вы чит-аемого пятого вычитателя соединены с входами вычитаемого первого, шестого и восьмого вычитателей и входами второй группы сумматора, входы вычитаемого седьмого вычитателя соединены с входами вычитаемого второго вычитателя, выходы сумматора соединены с информационными входами десятой группы коммутатора, выход зна- кового разряда сумматора соединен с девятым входом блока формирования цифры частного, который содержит девять элементов НЕ, восемь элементов И и четыре элемента ИЛИ, причем пер- вый вх,од блока формирования цифры частного соединен с входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И, второй вход блока формирования циф- ры частного соединен с вторым входом первого элемента И и входом второго элемента НЕ, выход которого соединен

с первым-входом второго элемента И, третий вход блока форм 1рования цифры частного соединен с вторым входом второго элемента И и входом третьего элемента НЕ, выход которого соединен с первым входом третьего элемента И, четвертый вход блока формирования Ш 1фры частного соединен с вторым входом третьего элемента И и входом четвертого элемента НЕ, выход которого соединен с первым входом четвертого элемента И, пятый блока формирования цифры частного соединен с вторым входом четвертого элемента И и входом пятого элемента НЕ, выход которого соединен с первым входом пятого элемента И, шестой вход блока .формирования цифры частного соединен с вторым входом пятого элемента И и входом шестого элемента НЕ, выход которого соединен с первым входом шестого элемента И, седьмой вход блока формирования цифры частного соединен с вторым входом шестого элемента И и входом седьмого элемента НЕ, выход которого соединен с первым вхо.тт; , дом седьмого элемента И, восьмой вход блока формирования цифры частного соединен с вторым входом седь- мого элемента И и входом восьмого элемента НЕ, выход которого соединен с первым входом восьмого элемента И, девятый вход блока формирования цифры частного соединен с вторым входом восьмого элемента И и входом девятого элемента НЕ, выход которого соединен с первыми входами первого и четвертого элементов ИЛИ, второй вход первого элемента ИЛИ соединен с выходом восьлмого элемента И, первый вход второго элемента ИЛИ соединен с выходом четвертого элемента И, первый вход третьего элемента ИЛИ соединен с выходом второго элемента

И, вторые входы второго и четвертого

(

элементов ИЛИ соединены с выходом

пятого элемента И, третий вход второго элемента ИЛИ соединен с.вторым входом третьего элемента ИЛИ и выходом шестого элемента И, четвертый вход второго элемента ИЛИ соединен с третьими входами третьего и четвертого элементов ИЛИ и выходом седьмого элемента И, четвертые входы третьего и четвертого элементов ИЛИ соединены с выходом третьего элемента И, пятый вход четвертого элемента ИЛИ соединен с выходом первого элемента И, выходы с первого по четвертый элементов ИЛИ являются выходами старшей и младшей двоичнь1х цифр десятичной цифры частного, выходы с первого восьмой элементов И образуют первую группу выходов блока формирования цифры частного,

фи., 7

;

Редактор Л.Пчелинская.

Заказ ЗА90/44Тираж 671Подписное

ВНИИПИ Государственного коьштета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигра(|нческое предприятие,г.Ужгород,ул .Проектная ,4

фиг,3

Составитель Н.Маркелова

Техред О.Гортвай Корректор Е.Сирохман

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления чисел | 1987 |

|

SU1441388A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

Изобретение относится к вычислительной технике и может быть ис- пользовано в высокопроизводительных вычислительных машинах, выполняющих операции десятичной .арифметики.Целью изобретения является сокращение количества оборудования устройства за счет совмещения операции выделения кратных делителя и получения десятичной цифры частного в течение одного такта работы устройства. Устрой- ство содержит регистры делимого, делителя и частного, блок формирования кратного делителя, восемь вычитате- лей, сумматор, блок формирования цифры частного. Выходы разрядов регистра делителя соединены с входами блока формирования кратного делителя и входами вычитаемого первого, пятого, шестого, восьмого вычитателей и входами второй группы сумматора. Выходы регистра делимого соединены с входами уменьшаемого первого-, второго, третьего и четвертого вычитателей. Выходы всех вычитателей, сумматора и регистра делимого соединены с дами коммутатор а, кроме того, выходы второго вычитат я соединены с входами уменьшаемого пятого, вычитателя, выходь третьего вычитателя соединены с входами уменьшаемого шестого и седьмого вычитателей, выходы четвертого вычитателя соединены с входами уменьшаемого восьмого вычитателя и входами первой группы сумматора. Выходы знаковых разрядов вычитaJeлeй и сумматора соединены с входами блока формирования цифры частного. Первая группа выходов блока соединена соответствующим образом с группой управляющих входов одиннадцатого коммутатора , а вторая группа вь:ходов соединена с информационными входами младшего разряда регистра частного. 3 ил., таблица. - S (Л L g to 00 сл

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1976 |

|

SU598075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления десятичных чисел | 1978 |

|

SU656087A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дроздов Е,А., Комарницкий В,А., Пятибротов А.П | |||

| Электронные-вычислительные машины единой системы | |||

| -М.: Машиностроение, 1981 | |||

| Ричарде Р.К | |||

| Арифметические операции на цифровых вычислительных машинах | |||

| НИ.: ИЛ, 1957, с.292, рис,9-3. | |||

Авторы

Даты

1986-06-30—Публикация

1984-12-05—Подача