редачи контрольных разрядов и Невозможность проверки оборудов-ания без этих шин. Кроме того, выбор комбинации контрольных разрядов ограничен областью свободных адресов памяти, не. занятых программой, так как контрольные разряды соответствуют отдельным разрядам адреса.

Недостатком устройства является также то, что для задания контрольных разрядов при проверке используется часть адресных разрядов, что делает невозможным проверку обору- дования при небольшом объеме памяти, т.е. малом количестве адресных шин, либо для осуществления такой проверки требуются дополнительные шины и дополнительное приемно-переда ющее оборудование. ,

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в устройство для проверки узлов контроля памяти., содержащее регистр управляющей информации, регистр входной информации, блок управления памятью, блок формирования контрольных разрядов, входной коммутатор, блок памяти, регистр выходной информации, блок контроля выходной информации, выходной коммутатор, причем группа управляющих входов устройства соединена с группой входов регистра управляющей информации, группа информационных выходов которого является группой информационных входов блока управления памятью, управляющий вход которого соединен с выходов разряда блокировки формирования контрольных разрядов региЪтра управляющей информации, первая группа выходов блока управления памятью соединена с управляющими входами блока памяти, первая группа информационных входов которого соединена с группой выходов входного коммутатора, группа управляющих входов которого соединена с второй группой выходов блока управления памятью, третья группа выходов которого соединена с группой управляющих входов выходного ..коммутатора, группа выходов которого является группой информационных выходов ycтpoйcfЪa, группа информационных входов устройства соединена с группой входов регистра входной информации, выходы регистра входной информации соединены с второй группой информационных входов блока-памяти и с группой входов блока формирования контрольных разрядов, группа выходов которого соединена с первой группой информационных входов входного коммутатора, группа выходов блока памяти соединена соответственно с группой информационных входов регистра выходной информации, группа управляющих входов которого соединена с первой группой выходов блока контроля выходной информации, вторая группа выходов которого является группой выходов сигналов ошибки устройства, группа выходов информационных разрядов регистра выходной информации соединена с третьей группой информационных входов блока памяти и с первой группой входов блока контроля выходной информации, введен регистр контрольной информации, выходы которого соединены с первой группой информационных входов выходного коммутатора, вторая группа информацион ных- входов которого соединена с ин формационными выходами регистра выходной информации, группа входов регистра контрольной информации соединена с третьей группой выходов блока контроля выходной информации, вторая группа которого соединена с выходами контрольных разрядов регистра выходной информации и с второй группой информационных входов входного коммутатора.

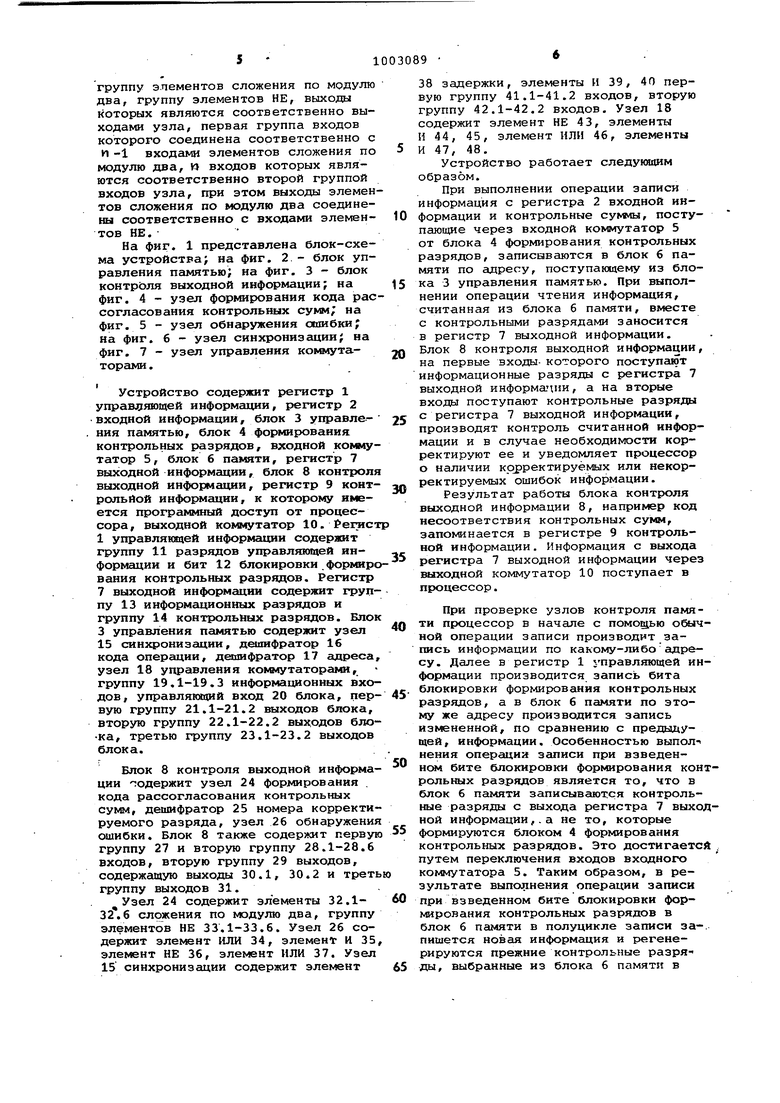

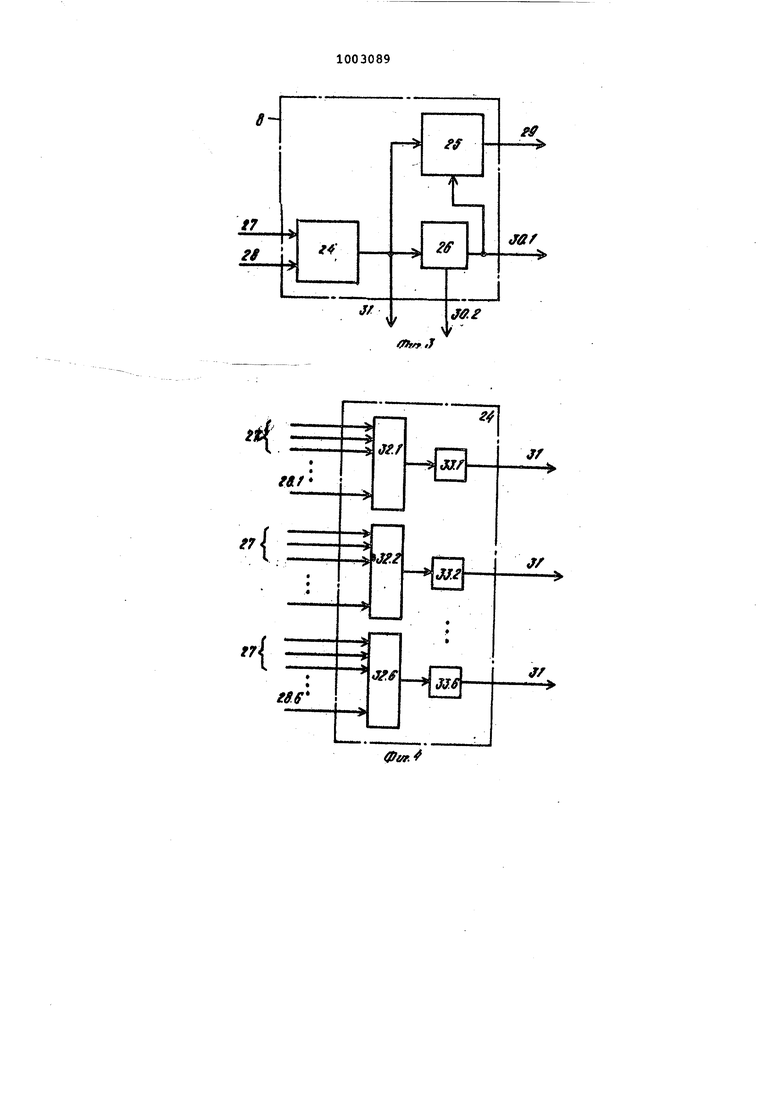

Блок контроля выходной информации содержит узел формирования кода рассогласования контрольных сумм, дешифратор номера корректируемого разряда, узел обнаружения ошибки, причем первая и вторая группы входов блока соединена соответственно с входами узла формирования кода рассогласования контрольных сумм, выходы которого соединены с группой информационных входов дешифратора номера корректируемого разряда, с .группой входов узла обнаружения ошибки и .являются третьей группой выходов .блока, первая группа выхо- дов которого соединена с .выходами дешифратора номера корректируемого разряда, управляющий вход которого соединен с первым выходом узла обнаружения ошибки и является первым выходом второй группы выходов блока, второй выход второй группы выходов блока соединен с вторым выходом узла обнаружения ошибки.

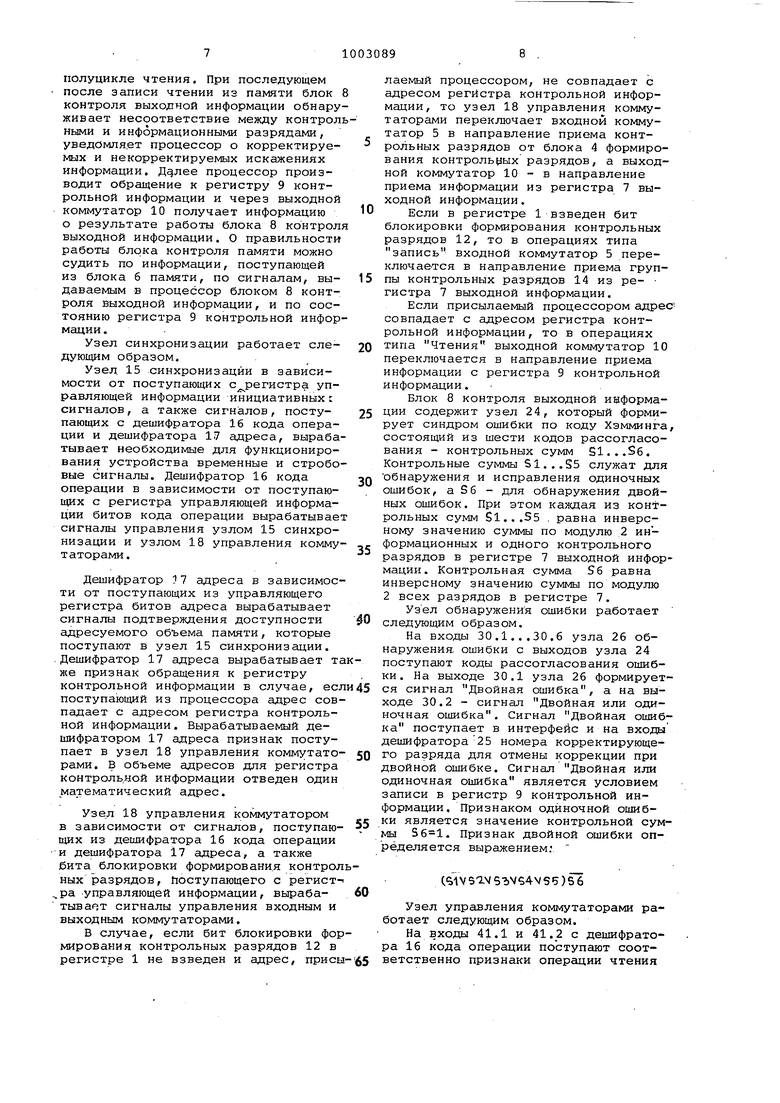

Узел обнаружения ошибки содержит дв элемента ИЛИ, элемент НЕТ элемент И, выход которого является первым выходом группы выходов узла, второй выход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом второго элемента ИЛИ и с первым входом элемента И , второй вход которого соединен с выходом элемента НЕ, вход которого соединен с вторым входом элемента ИЛИ и с .Ц -входом узла (где h входов узла, И -1 входы которого соединены соответственно с входами второго элемента ИЛИ.

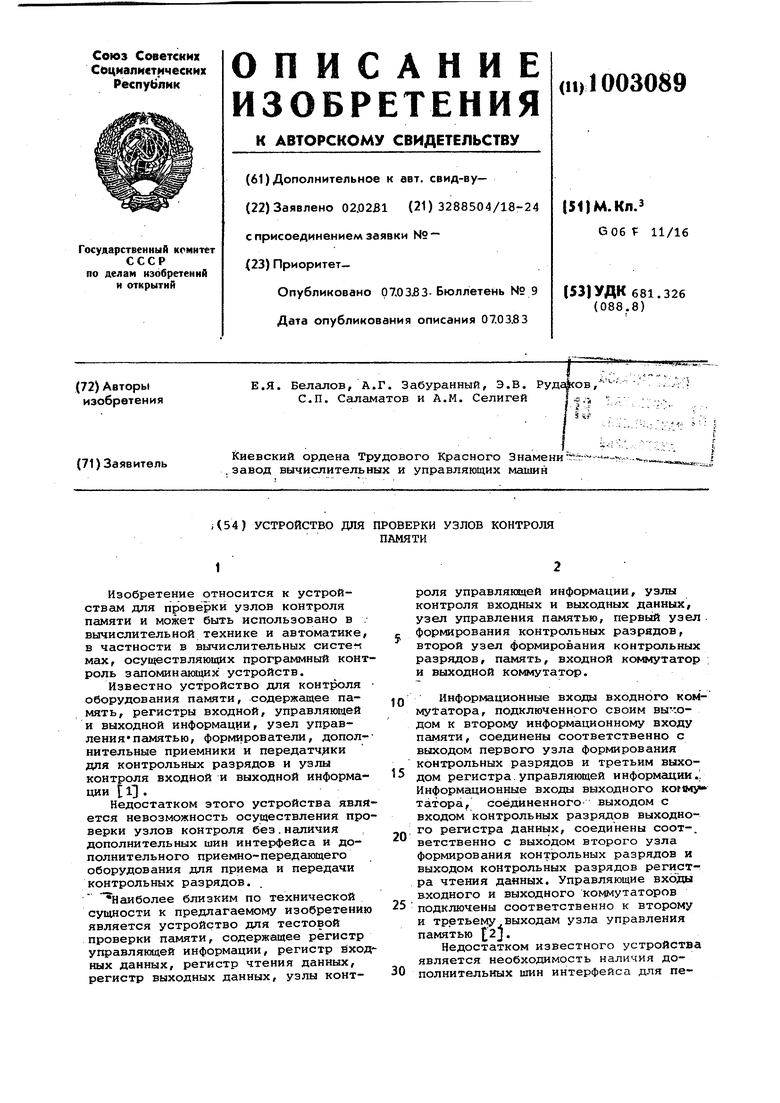

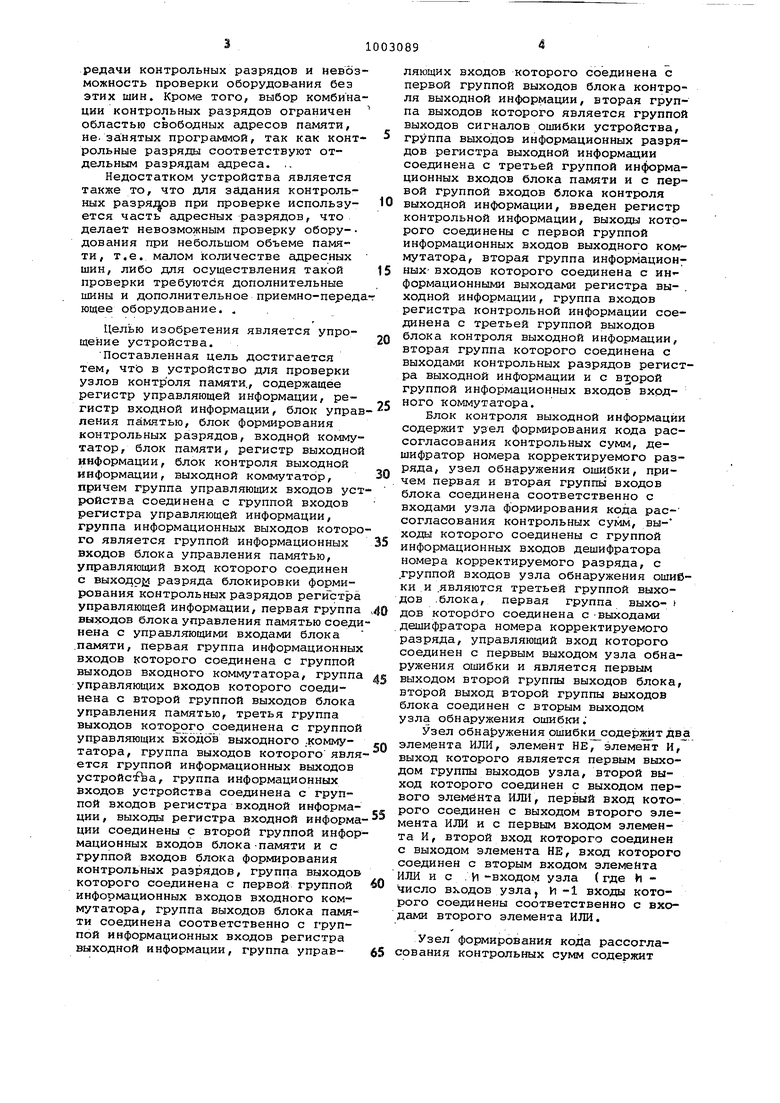

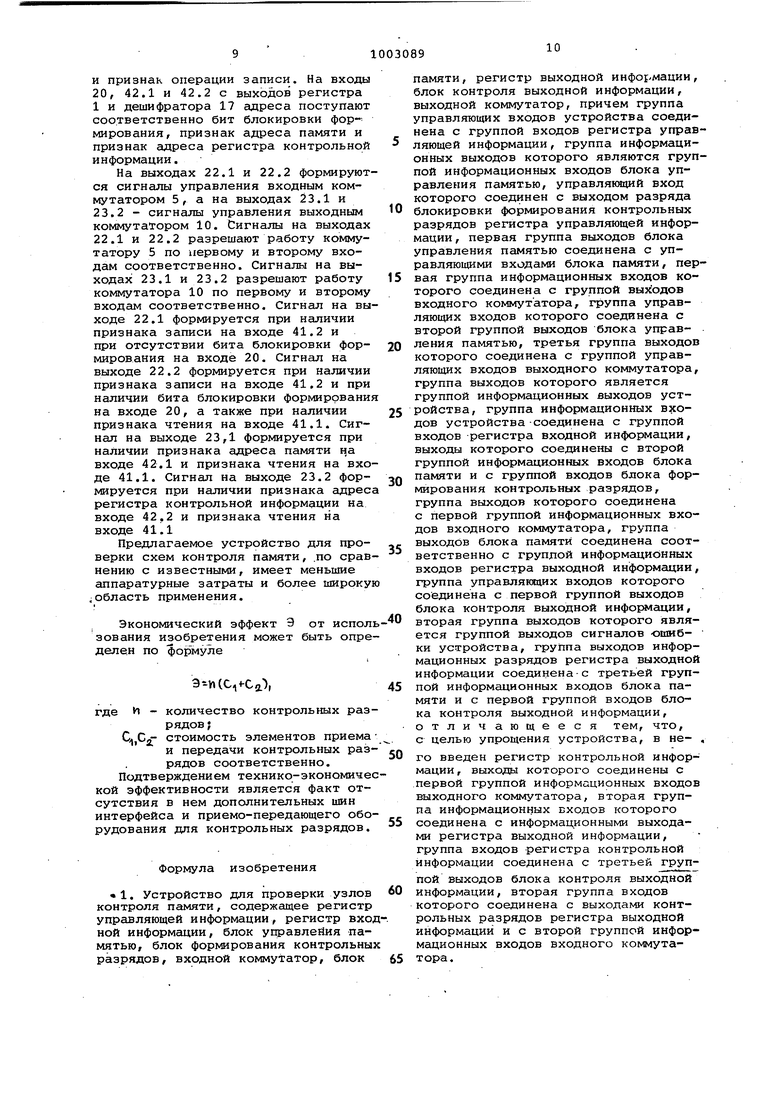

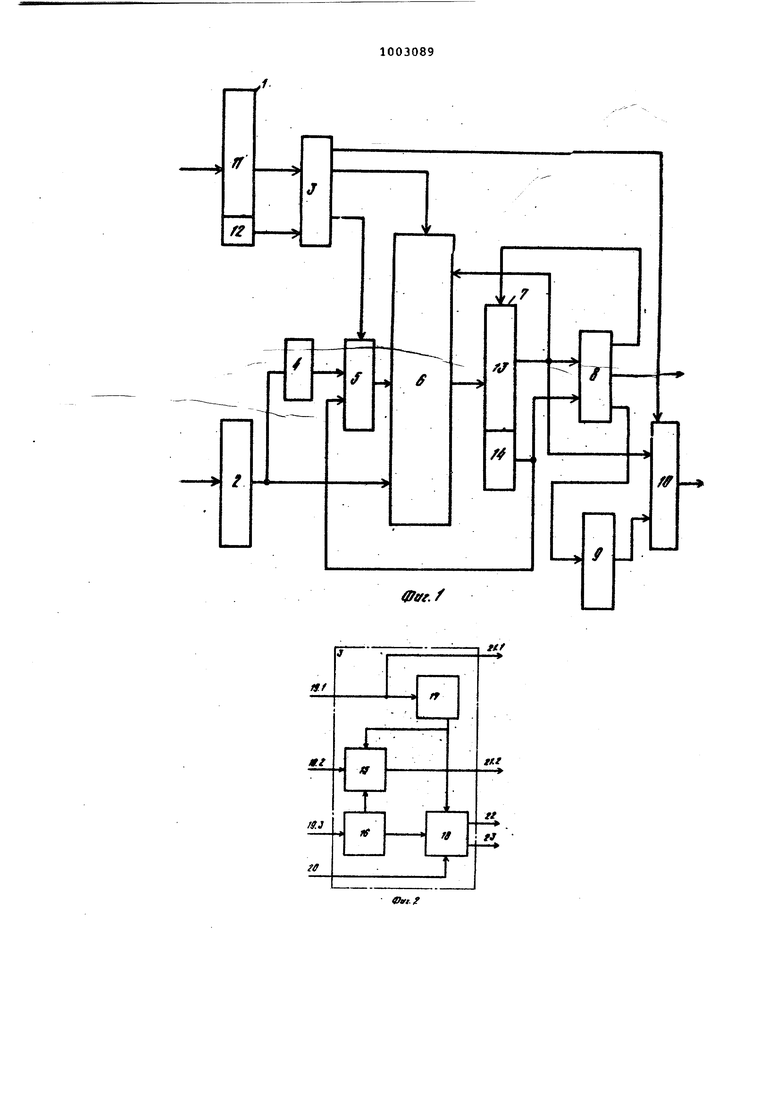

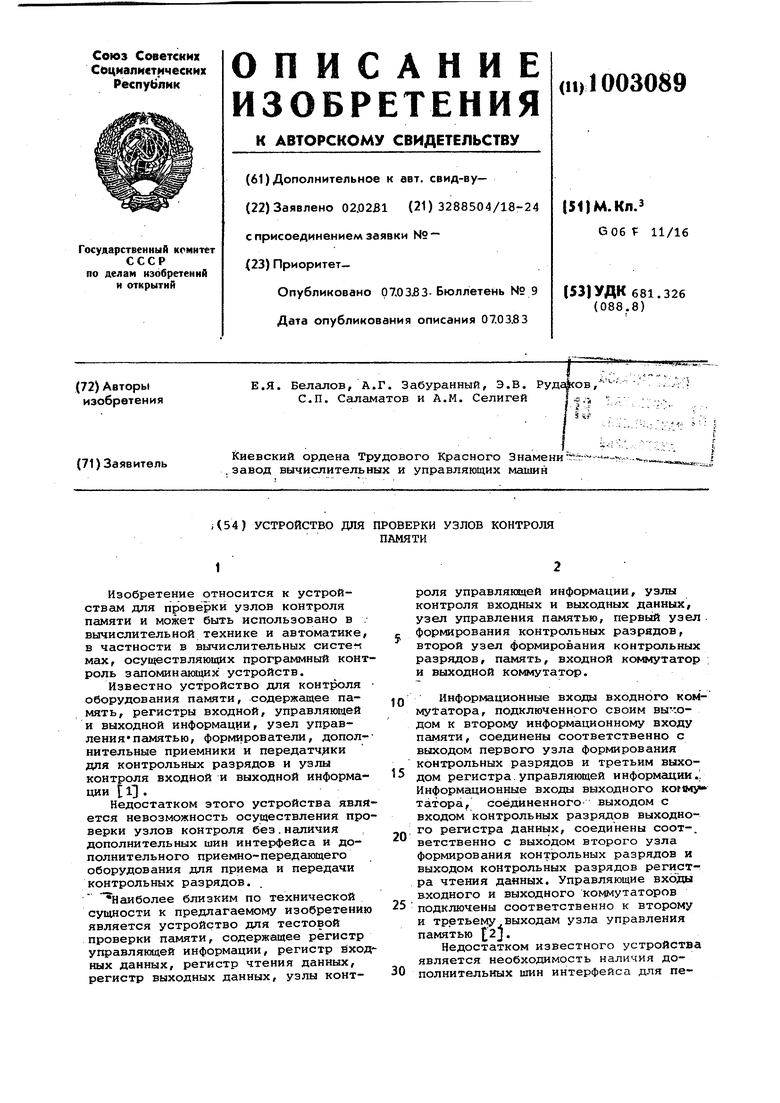

Узел формирования кода рассогласования контрольных сумм содержит группу элементов сложения по модулю два, группу элементов НЕ, выходы которых являются соответственно выходами узла, первая группа входов которого соединена соответственно с И-1 входами элементов сложения по модулю два, входов которых являются соответственно второй группой входов узла, при этом выходы элемен тов сложения по модулю два соединены соответственно с входами элементов НЕ. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок управления памятью; на фиг. 3 - блок контроля выходной информации; на фиг. 4 - узел формирования кода рас согласования контрольных сумм; на фиг. 5 - узел обнаружения сшибки; на фиг. б - узел синхронизации; на фиг. 7 - узел управления коммутаторами. Устройство содержит регистр 1 управд яющей информации, регистр 2 входной информации, блок 3 управле-ния памятью, блок 4 формирования контрольных разрядов, входной коммутатор 5, блок 6 пазчяти, регистр 7 выходной информации, блок 8 контроля выходной информации, регистр 9 контрольйой информсщии, к которому имеется программный доступ от процессора, выходной коммутатор 10. Регтют 1 управляющей информации содержит группу 11 разрядов управляющей информации и бит 12 блокировки.формиро вания контрольных разрядов. Регистр 7 выходной информации содержит группу 13 информахцюнных разрядов и группу 14 контрольных разрядов. Блок 3 управления памятью содержит узел 15 синхронизации, дешифратор 16 кода операции, дешифратор 17 гщреса узел 18 упрсшления коивлутаторами, группу 19.1-19.3 информационных входов, управляюодай вход 20 блока, первую группу 21.1-21.2 выходов блока, вторую группу 22.1-22.2 выходов блока, третью группу 23.1-23.2 выходов блока. Блок 8 контроля выходной информации одержит узел 24 формирования кода рассогласования контрольных сумм, дешифратор 25 номера корректируемого разряда, узел 26 обнаружения ошибки. Блок 8 также содержит первую группу 27 и вторую группу 28.1-28.6 входов, вторую группу 29 выходов, содержащую выходы 30.1, 30.2 и треть группу выходов 31. Узел 24 содержит элементы 32.132.6 сложения по модулю два, группу элементов НЕ 33.1-33.6. Узел 26 содержит элемент ИЛИ 34, элемент И 35 элемент НЕ 36, элемент ИЛИ 37. Узел 15 синхронизации содержит элемент 38 задержки, элементы И 39, 40 первую группу 41.1-41.2 входов, вторую группу 42.1-42.2 входов. Узел 18 содержит элемент НЕ 43, элементы Н 44, 45, элемент ИЛИ 46, элементы И 47, 48. Устройство работает следуклцим образом. При выполнении операции записи информация с регистра 2 входной информации и контрольные сукиы, поступающие через входной коммутатор 5 от блока 4 формирования контрольных разрядов, записываются в блок 6 памяти по адресу, поступающему из блока 3 управления памятью. При выполнении операции чтения информация, считанная из блока 6 памяти, вместе с контрольными разрядами заносится в регистр 7 выходной информации. Блок 8 контроля выходной информации, на первые входы- которого поступгиот информационные разряды с регистра 7 выходной информахии, а на вторые входы поступают контрольные разряды с регистра 7 выходной информации, производят контроль считанной информации и в случае необходимости корректируют ее и уведомляет процессор о наличии кр)ректируемых или некорректируемых ошибок информации. Результат работы блока контроля выходной информации 8, например код несоответствия контрольных сумм, запоминается в регистре 9 контрольной информации. Информация с выхода регистра 7 выходной информации через выходной коммутатор 10 поступает в процессор. При проверке узлов контроля памяти процессор в начале с помощью обычной операции записи производит запись информации по какому-либо адресу. Далее в регистр 1 управляющей информации производится запись бита блокировки фoplvtиpoвaния контрольных разрядов, а в блок 6 памяти по этому же адресу производится запись измененной, по сравнению с предыдущей, информации. Особенностью выпол- нения операции записи при взведение бите блокировки формирования контрольных разрядов является то, что в блок 6 Пс1Мяти записываиотся контрольные разряды с выхода регистра 7 выходной информации,.а не то, которые формируются блоком 4 формирования контрольных разрядов. Это достигаете путем переключения входов входного коммутатора 5. Таким образом, в результате выполнения операции записи при взведенном бите блокировки формирования контрольных разрядов в блок 6 в полуцикле записи за-. пишется новая информация и регенерируются прежние контрольные разряды, выбранные из блока 6 памяти в полуцикле чтения, При последующем после записи чтении из памяти блок контроля выходной информации обнару живает несоответствие между контрол ными и информационными разрядами, уведомляет процессор о корректируемых и некорректируемых искажениях информации. процессор производит обращение к регистру 9 контрольной информации и через выходной коммутатор 10 получает информацию о результате работы блока 8 контрол выходной информации, О правильности работы блока контроля памяти можно судить по информации, поступающей из блока б памяти, по сигналам, выдаваемым в процессор блоком 8 контроля выходной информации, и по состоянию регистра 9 контрольной инфор мации . Узел синхронизации работает еледующим образом. Узел. 15 синхронизации в зависимости от поступающих с регистра управляющей информации инициативных : сигналов, а также сигналов, поступающих с дешифратора 16 кода операции и дешифратора 17 адреса, выраба тывает необходимые для функционирования устройства временные и стробо вые сигналы. Дешифратор 16 кода операции в зависимости от поступающих с регистра управляющей информации битов кода операции вырабатывае сигналы управления узлом 15 синхронизации и узлом 18 управления комму таторами. Дешифратор 7 адреса в зависимос ти от поступающих из управляющего регистра битов адреса вырабатывает сигналы подтверждения доступности адресуемого объема памяти, которые поступают в узел 15 синхронизации. .Дешифратор 17 адреса вырабатывает т же признак обращения к регистру контрольной информации в случае, ес поступающий из процессора адрес сов падает с адресом регистра контрольной информации. Вырабатываемый дешифратором 17 адреса признак поступает в узел 18 управления коммутато рами. В объеме адресов для регистра контроль,иой информации отведен один математический адрес. Узел 18 управления коммутатором в зависимости от сигналов, поступаю щих из дешифратора 16 кода операции и дешифратора 17 адреса, а также бита блокировки формирования контро ных разрядов, поступающего с регист ра -управляющей информации, вырабатывавт сигналы управления входным и выходным коммутаторами. В случае, если бит блокировки фо мирования контрольных разрядов 12 в регистре 1 не взведен и адрес, прис лаемый процессором, не совпадает с адресом регистра контрольной информации, то узел 18 управления коммутаторами переключает входной коммутатор 5 в направление приема контрольных разрядов от блока 4 формирования контрольных разрядов, а выходной коммутатор 10 - в направление приема информации из регистра 7 выходной информации. Если в регистре 1 взведен бит блокировки формирования контрольных разрядов 12, то в операциях типа запись входной коммутатор 5 переключается в направление приема группы контрольных разрядов 14 из ре- гистра 7 ВЫХОДНОЙ информации. Если присылаемый процессором адрес совпадает с адресом регистра контрольной информации, то в операциях типа Чтения выходной коммутатор 10 переключается в направление приема информации с регистра 9 контрольной информации. Блок 8 контроля выходной информации содержит узел 24, который формирует синдром ошибки по коду Хэмминга, состоящий из шести кодов рассогласования - контрольных сумм S1...S6. Контрольные суммы S1...S5 служат для обнаружения и исправления одиночных ошибок, а S6 - для обнаружения двойных ошибок. При этом каждая из контрольных сумм S1...S5 . равна инверсному значению суммы по модулю 2 информационных и одного контрольного разрядов в регистре 7 выходной информации. Контрольная сумма S6 равна инверсному значению суммы по модулю 2 всех разрядов в регистре 7. Узел обнаружения ошибки работает следующим образом. На входы 30.1...30.6 узла 26 обнаружения ошибки с выходов узла 24 поступают коды рассогласования ошибки. На выходе 30.1 узла 26 формируется сигнал Двойная ошибка, а на выходе 30.2 - сигнал Двойная или одиночная ошибка. Сигнал Двойная ошибка поступает в интерфейс и на входы дешифратора 25 номера корректирующего разряда для отмены коррекции при двойной ошибке. Сигнал Двойная или одиночная ошибка является условием записи в регистр 9 контрольной информации. Признаком одиночной ошибки является значение контрольной суммы . Признак двойной ошибки определяется выражением: C Tv5a /s-bve4vs5)S6 Узел управления коммутаторами работает следующим образом. На входы 41.1 и 41.2 с дешифратора 16 кода операции поступают соответственно признаки операции чтения и признак операции записи. На входы 20, 42.1 и 42.2 с выходов регистра 1 и дешифратора 17 адреса поступают соответственно бит блокировки формирования, признак адреса памяти и признак адреса регистра контрольной информации. На выходах 22.1 и 22.2 формируют ся сигналы управления входным коммутатором 5, а на выходах 23.1 и 23.2 - сигналы управления выходным коммутатором 1C. Сигналы на выходах 22.1 и 22.2 разрешают работу коммутатору 5 по первому и второму входам соответственно. Сигналы на выходах 23.1 и 23.2 разрешают работу коммутатора 10 по первому и второму входам соответственно. Сигнал на вы ходе 22.1 формируется при наличии признака записи на входе 41.2 и при отсутствии бита блокировки формирования на входе 20. Сигнал на выходе 22.2 формируется при наличии признака записи на входе 41.2 и при наличии бита блокировки формировани на входе 20, а также при наличии признака чтения на входе 41.1. Сигнал на выходе 23,1 формируется при наличии признака адреса памяти на входе 42.1 и признака чтения на вхо де 41.1. Сигнал на выходе 23.2 формируется при наличии признака адрес регистра контрольной информации на входе 42.2 и признака чтения на входе 41.1 Предлагаемое устройство для проверки схем контроля памяти, .по срав нению с известными, имеет меньшие аппаратурные затраты и более широку ;область применения. Экономический эффект Э от испол зования изобретения может быть опре делен по формуле a-vtcc i-Ca), где И - количество контрольных разрядов;С,,С стоимость элементов приема и передачи контрольных разрядов соответственно. Подтверждением технико-экономичес кой эффективности является факт отсутствия в нем дополнительных шин интерфейса и приемо-передающего оборудования для контрольных разрядов. Формула изобретения 1. Устройство для проверки узлов контроля памяти, содержащее регистр управляющей информации, регистр вход ной информации, блок уцравлейия памятью, блок формирования контрольных разрядов, входной коммутатор, блок памяти, регистр выходной информации, блок контроля выходной информации, выходной коммутатор, причем группа управляющих входов устройства соединена с группой входов регистра управляющей информации, группа информационных выходов которого являются группой информационных входов блока управления памятью, управлякяций вход которого соединен с выходом разряда блокировки формирования контрольных разрядов регистра управляющей информации , первая группа выходов блока управления памятью соединена с управляющими входами блока памяти, первая группа информационных входов которого соединена с группой выходов входного коммутатора, группа управляющих входов которого соединена с второй группой выходов блока управления памятью, третья группа выходов которого соединена с группой управляющих входов выходного коммутатора, группа выходов которого является группой информационных выходов устройства, группа информационных входов устройства -соединена с группой входов -регистра входной информации, выходы которого соединены с второй группой информационных входов блока памяти и с группой входов блока формирования контрольных разрядов, группа выходов которого соединена с первой группой информационных входов входного коммутатора, группа выходов блока памяти соединена соответственно с групдой информационных входов регистра выходной информации, группа управляющих входов которого соединена с первой группой выходов блока контроля выходной информации, вторая группа выходов которого является группой выходов сигналов ошиб- ки устройства, группа выходов информационных разрядов регистра выходной информации соединена-с третьей группой информационных входов блока памяти и с первой группой входов блока контроля выходной информации, отличающееся тем, что, с целью упрощения устройства, в не- , го введен регистр контрольной информации, выходы которого соединены с первой группой информационных входов выходного коммутатора, вторая группа информационных входов которого соединена с информационными выходами регистра выходной информации, группа входов регистра контрольной информации соединена с третьей группой выходов блока контроля выходной информации, вторая группа входов которого соединена с выходами контрольных разрядов регистра выходной информации и с второй группой информационных входов входного коммутатора.

2.Устройство по п. 1, отличающееся тем, что -блок контроля выходной информации содержит узел формирования кода рассогласования контрольных сумм, дешифратор номера корректируемого разряда, узел обнаружения ошибки, причем первая и вторая группы входов блока соединены соответственно с.входами узла формирования кода рассогласования контрольных сумм, выходы которого соединены с группой информационных входов дешифратора номера корректируемого разряда, с группой входов узла обнаружения ошибки и являются третьей группой выходов блока, первая группа выходов которого соединена с выходами дешифратора i номера корректируемого разряда,, управляющий вход которого соединен с первым выходом узла обнаружения ошибки и является первым выходом второй групч пы выхолов блока, второй выход второй группы выходов блока соединен с вторым выходом узла обнаружения ошибки.

3.Устройство по п. 2, отличающееся тем, что узел обна- ружения ошибки содержит два элемента ИЛИ, элемент НЕ, элемент И, выход которого является первым выходом группы выходов узла, второй выход которого соединен с выходом первого

элемента ИЛИ, первый вход которого соединен с выходом второго элемента ИЛИ и с первым входом элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого сое,динен с вторым входом элемента ИЛИ и с и-входом узла (л - число входов узла), и-1 входы которого соединены соответственно с входами второго элемента ИЛИ,

.

4, Устройство поп, 2, отличающееся тем, что узел формирования рассогласования контрольных сумм содержит группу элементов сложения по модулю два, группу элементов НЕ, выходы которых являются соответственно выходами узла, первая Группа входов которого соединена соответственно с П.-1 входами элементов сложения по модулю два, « -входов которых являются соответственно второй группой входов узла, при этом выходы элементов сложения по модулю два соединены соответственно с входами элементов НЕ.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3465132, кл. 235-153, опублик, 1970,

2. Авторское свидетельство СССР № 744577, кл, G06F 11/00, 1978 (прототип).

Г -

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

0lff.f

ti.f

г

///

-

// //

{

{

фиг «f

Фг/г. f

Авторы

Даты

1983-03-07—Публикация

1981-02-02—Подача