введены дешифратор адреса и регистр контрольной информации, причем группа информационных входов дешифратора адреса связана с группой информационных выходов управляющего регистра, управляющий выход дешифратора адреса соединен с вторым управляющим входом узла синхронизации и узла управления коммутацией, третий управляющий вход которого подключен к управляющему выходу регистра контрольной информации,, информационный выход которого связан с второй группой информационных входов коммутатора, первая группа информационных входов регистра контрольной информации соединена с группой информационных выходов узла формирования синдромов, вторая группа информационных входов регистра контрольной ин- формации связана с первой группой информационных входов устройства, подключенных к соответствующим входам входного регистра, вторая группа информационных входов устройства подключена к соответствующим входам управляющего регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки узлов контроля памяти | 1981 |

|

SU1003089A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

1 ; .

Изобретение относится к устройствам дЛя проверки схем контроля памяти и может быть использовано в вычислительной технике и автоматике, в частности в вычислительных системах, осуществляющих программный контроль зaпoм ft aющиx устройств.

Известны устройства для контроля оборудования памяти, содержащие память, регистры входной, управляющей и выходной информации, узел управления, формирователи контрольных разрядов, дополнительные приемники и передатчики для контрольных разрядов и узел контроля входной и выходной информации О

К недостаткам устройства относится невозможность осуществления проверки схем контроля без наличия дополнительных шин интерфейса и дополнительного приемопередающего оборудования для приема и передачи контрольных разрядов.

Наиболее близким по технической сущности к предлагаемому является уст ройство для тестовой проверки памяти, содержащее регистр управляющей информации, регистр входных данных, регистр чтения данных, регистр выходных данных, узлы контроля управляющей информации, входных данных и выходных данных, .узел упр авления памятью, первый узел формирования контрольных разрядов, второй узел формирования контрольных разрядов, память, входной коммутатор и выходной коммутатор. Информационные входы входного комм/гатора, подключенного своим выходом

к второму информационному входу памяти, соединены соответственно с выходом первого узла формирования контрольных разрядов и третьим выходом регистра управляющей информации. Информационные входы выходного коммутатора, соединенного выходом с входом контрольных разрядов выходного регистра данных, соединены соответственно с выходом второго узла форми|Х)вания контрольных разрядов и выходом контрольных разрядов регистра чтения данных. Управляющие входы входного и выходного коммутаторов подключены со|ответст аенно к второму и третьему выходам узла управления памятью С,

Недостатками известного устройства являются необходимость наличия дополнительных шин интерфейса для передачи контрольных разрядов и специального признака диагностических операций и невозможность проверки оборудования без наличия тактовых шин. Кроме того, выбор комбинации контрольных разрядов ограничен областью свободных адресов памяти, не занятых программой так как контрольные ;разряды соответствуют отдельным разрядам адреса.

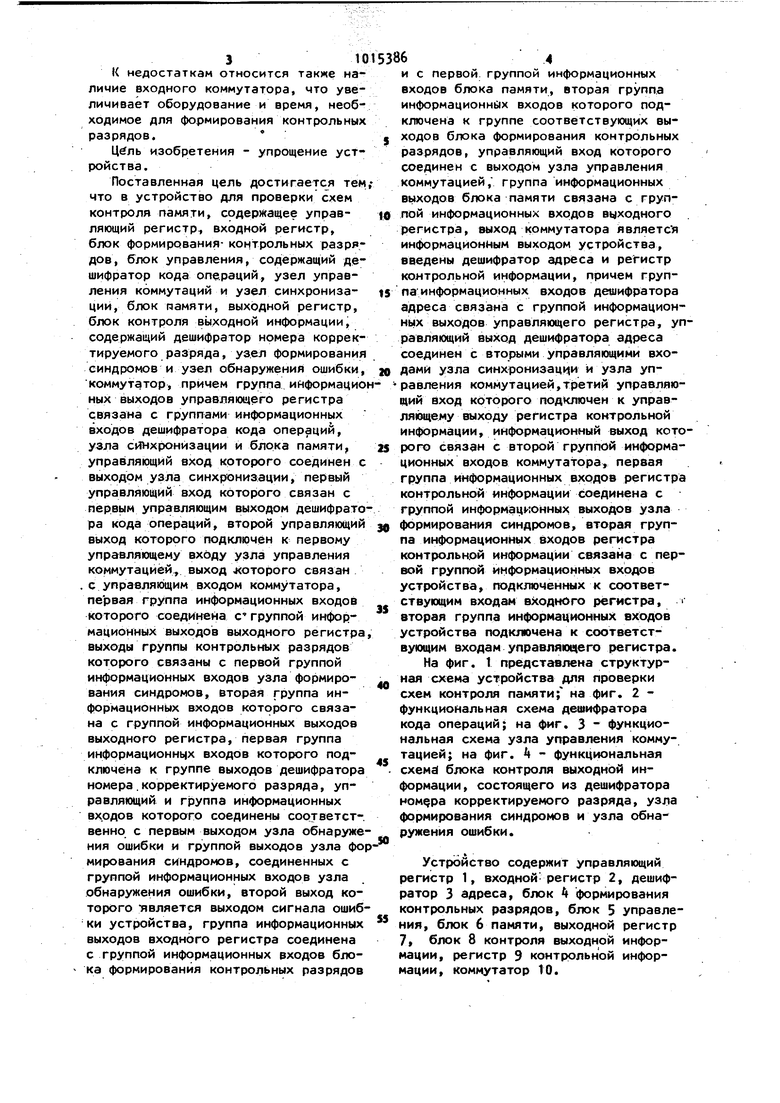

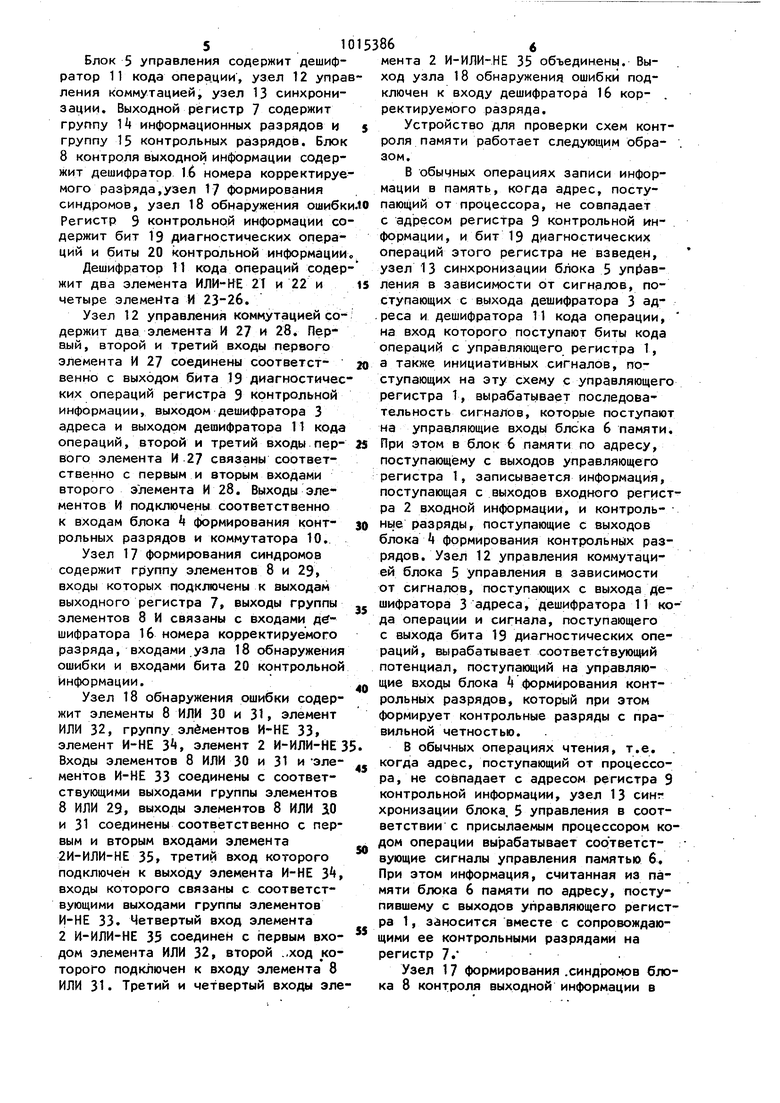

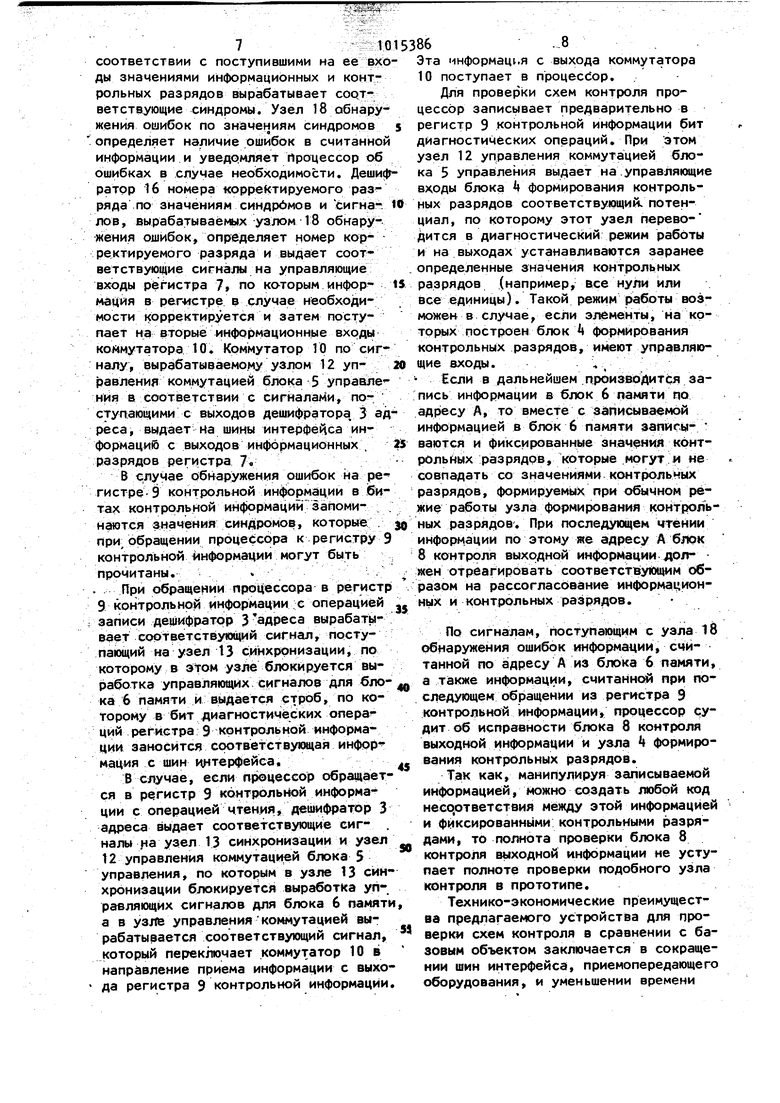

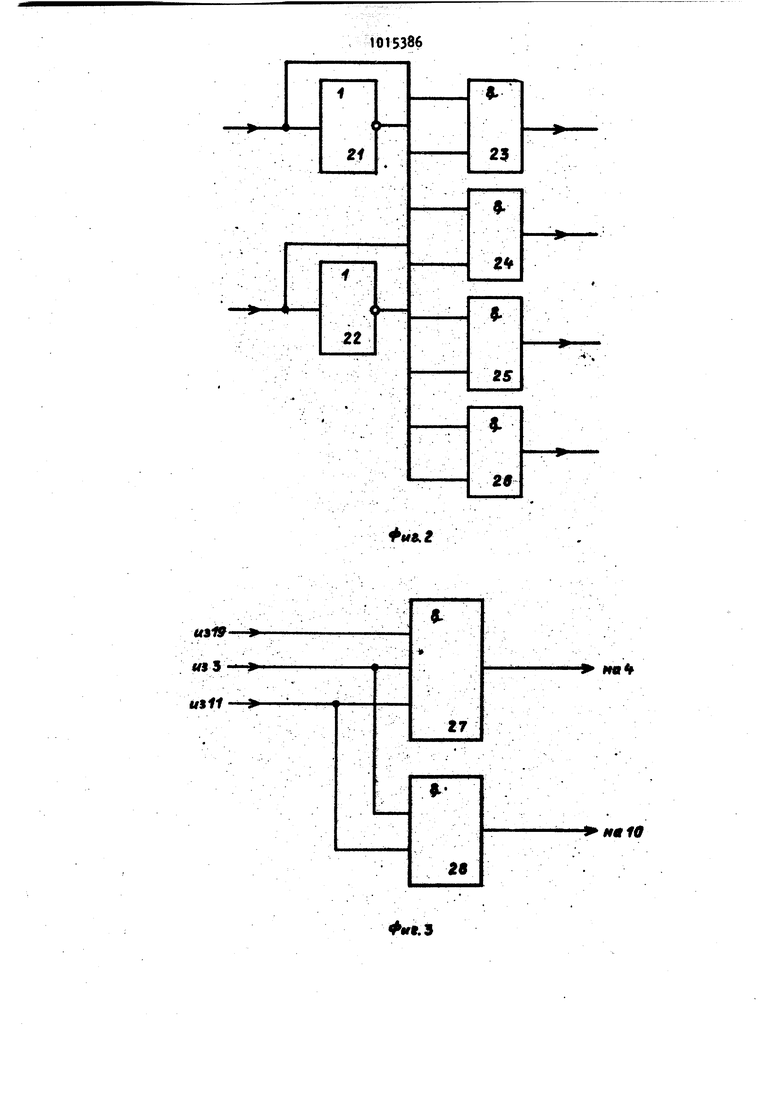

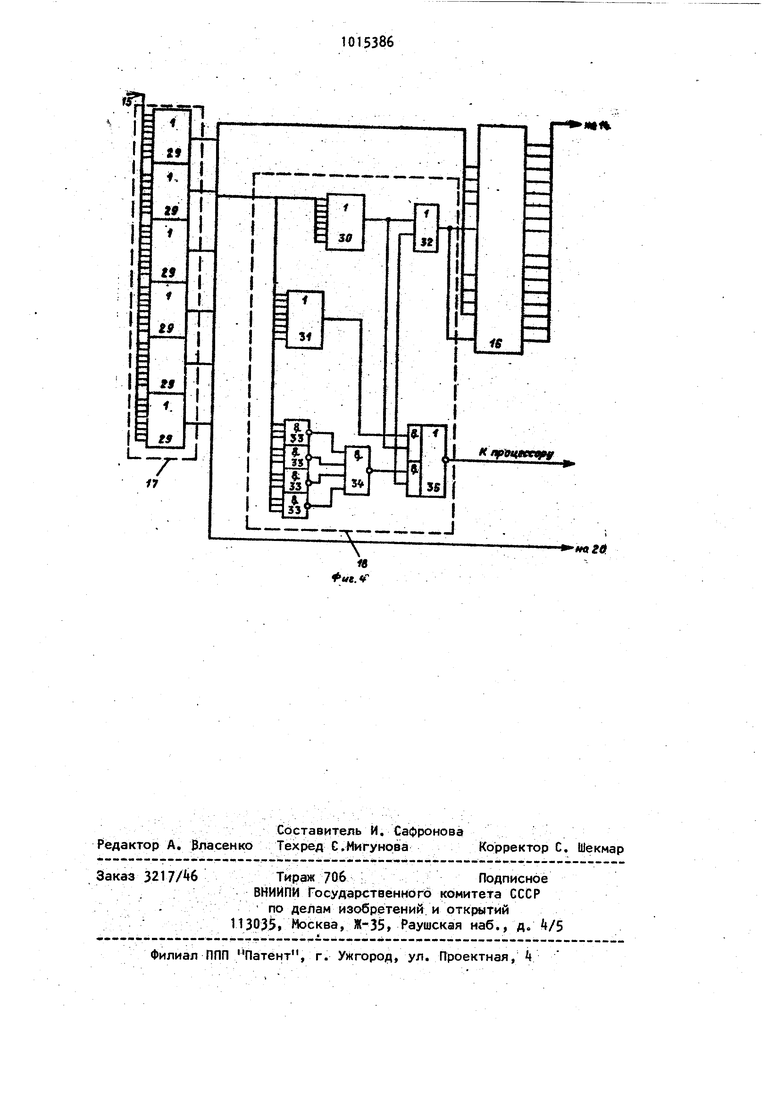

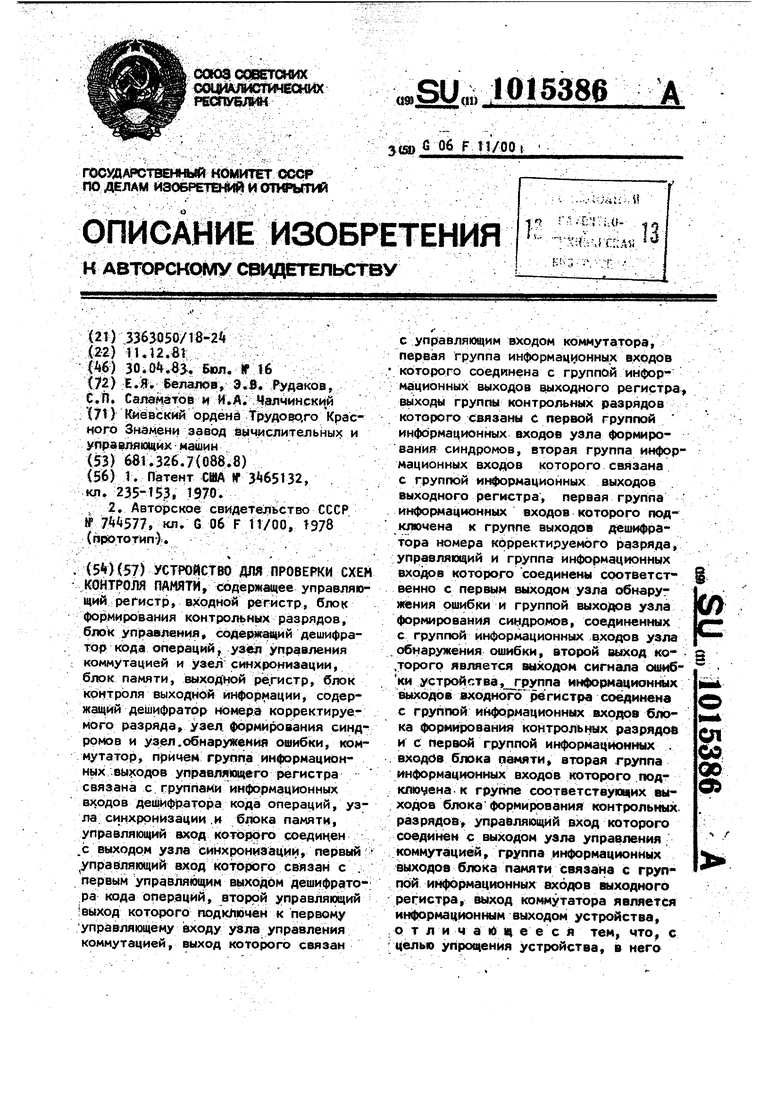

Недостатком устройства является также то, что для задания контрольных разрядов пр1И проверке используется часть адресных разрядов, что (елает невозможным проверку оборудования при небольшом объеме памяти, т.е, малом количестве адресных шин, ибо для осуществления такой проверки требуютСи дополнительные шины и дополнительное приемопередающее оборудование. К недостаткам относится также наличие входного коммутатора, что увеличивает оборудование и время, необходимое для формирования контрольных разрядов. Цйль изобретения - упрощение устройства. Поставленная цель достигается тем что в устройство для проверки схем контроля памяти, содержащее управляющий регистр входной регистр, блок формирования- контрольных разрядов, блок управления, содержащий дешифратор кода операций, узел управления коммутаций и узел синхронизации, блок памяти, выходной регистр, блок контроля выходной информации, содержащий дешифратор номера корректируемого разряда, узел формирования синдромов и узел обнаружения ошибки, коммутатор, причем группа информацио ных выходов управляющего регистра связана с группами информационных входов дешифратора кода операций, узла синхронизации и блока памяти, управляющий вход которого соединен с выходом узла синхронизации, первый управляющий вход которого связан с первым управляющим выходом дешифрато ра кода операций, второй управляющий выход которого подключен к первому управлякядему входу узла управления коммутацией, выход которого связан , с управляющим входом коммутатора, первая группа информационных входов которого соедикена сгруппой информационных выходов выходного регистра выходы группы контрольных разрядов которого связаны с первой группой информационных входов узла формирования синдромов, вторая группа информационных входов которого связана с группой информационных выходов выходного регистра, первая группа информационных входов которого подключена к группе выходов дешифратора номера.корректируемого разряда, управляющий и группа информационных входов которого соединены coojBeTCTвенно с первым выходом узла обнаруже ния ошибки и группой выходов узла фо мирования синдромов, соединенных с группой информационных входов узла обнаружения ошибки, второй выход которого является выходом сигнала ошиб ки устройства, группа информационных выходов входного регистра соединена с группой информационных входов блока формирования контрольных разрядов и с первой группой информационных входов блока памяти, вторая группа информационных входов которого подключена к группе соответствующих выходов блока формирования контрольных разрядов, управляющий вход которого соединен с выходом узла управления коммутацией, группа информационных выходов блока памяти связана с группой информационных входов выходного регистра, выход коммутатора является информационным выходом устройства, введены дешифратор адреса и регистр контрольной информации, причем группа информационных входов дешифратора адреса связана с группой информационных выходов управляющего регистра, управляющий выход дешифратора адреса соединен с вторыми управляющими входами узла синхронизации и узла управления коммутацией,третий управляющий вход которого подключен к управляющему выходу регистра контрольной информации, информационный выход которого связан с второй группой информационных входов коммутатора, первая группа информационных входов регистра контрольной информации соединена с группой информационных выходов узла формирования синдромов, вторая группа информационных входов регистра контрольной информации связана с первой группой информационных входов устройства, подключенных к соответствующим входам входного регистра, вторая группа информаиионных входов устройства подключена к соответствующим входам управляющего регистра. На фиг. 1 представлена структурная схема устройства для проверки схем контроля памяти; на фиг. 2 функциональная схема дешифратора кода операций; на фиг. 3 - функциональная схема узла управления коммутацией; на фиг. 4 - функциональная схема блока контроля выходной информации, состоящего из дешифратора номера корректируемого разряда, узла формирования синдромов и узла обнаружения ошибки. Устройство содержит управляющий регистр 1, входной регистр 2, дешифратор 3 адреса, блок 4 формирования контрольных разрядов, блок 5 управления, блок 6 памяти, выходной регистр 7, блок 8 контроля выходной информации, регистр 9 контрольной информации, коммутатор 10. Блок 5 управления содержит дешифратор 11 кода операции, узел 12 упра ления коммутацией, узел 13 синхронизации. Выходной регистр 7 содержит группу 1 информационных разрядов и группу 15 контрольных разрядов. Блок 8 контроля выходной информации содержит дешифратор 16 номера корректируе мого разряда, узел 17 формирования синдромов, узел 18 обнаружения ошибк Регистр 9 контрольной информации со держит бит 19 диагностических операций и биты 20 контрольной информации Дешифратор 11 кода операций содер жит два элемента ИЛИ-НЕ 2Т и 22 и четыре элемента И . Узел 12 управления коммутацией содержит два элемента И 27 и 28, Первый, второй и третий входы первого элемента И 27 соединены соответственно с выходом бита 19 диагностичес ких операций регистра 9 контрольной информации, выходом дешифратора 3 адреса и выходом дешифратора 11 кода операций, второй и третий входы первого элемента И 27 связаны соответственно с первым и вторым входами второго элемента И 28, Выходы элементов И подключены соответственно к входам блока формирования контрольных разрядов и коммутатора 10, Узел 17 формирования синдромов содержит группу элементов 8 и 29, входы которых подключены к выходам выходного регистра 7 выходы группы элементов 8 И связаны с входами дешифратора 16 номера корректируемого разряда, входами узла 18 обнаружения ошибки и входами бита 20 контрольной информации. Узел 18 обнаружения ошибки содержит элементы 8 ИЛИ 30 и 31, элемент ИЛИ 32, группу элементов И-НЕ 33, элемент И-НЕ З, элемент 2 И-ИЛИ-НЕ 3 Входы элементов 8 ИЛИ 30 и 31 иэлементов И-НЕ 33 соединены с соответствующими выходами группы элементов 8 ИЛИ 29, выходы элементов 8 ИЛИ 310 и 31 соединены соответственно с первым и вторым входами элемента 2И-ИЛИ-НЕ 35, третий вход которого подключен к выходу элемента И-НЕ 3, входы которого связаны с соответствующими выходами группы элементов И-НЕ 33. Четвертый вход элемента 2 И-ИЛИ-НЕ 35 соединен с первым входом элемента ИЛИ 32, второй ..ход которого подключен к входу элемента 8 ИЛИ 31. Третий и четвертый входы эле мента 2 И-ИЛИ-НЕ 35 объединены. Выход узла 18 обнаружения ошибки подключен к входу дешифратора 16 кор- . ректируемого разряда. Устройство для проверки схем контроля памяти работает следующим образом, В обычных операциях записи информации в память, когда адрес, поступающий от процессора, не совпадает с адресом регистра 9 контрольной информации, и бит 19 диагностических операций этого регистра не взведен, узел 13 синхронизации блока 5 управления в зависимости от сигналов, поступающих с выхода дешифратора 3 адреса и дешифратора 11 кода операции, на вход которого поступают биты кода операций с управляющего регистра 1, а также инициативных сигналов, поступающих на эту схему с управляющего регистра 1, вырабатывает последовательность сигналов, которые поступают на управляющие входы блЬка 6 памяти. При этом в блок 6 памяти по адресу, поступающему с выходов управляющего регистра 1, записывается информация, поступающая с выходов входного регистра 2 входной информации, и контрольные разряды, поступающие с выходов блока i формирования контрольных разрядов. Узел 12 управления коммутацией блока 5 управления в зависимости от сигналов, поступающих с выхода дешифратора 3 адреса, дешифратора 11 кода операции и сигнала, поступающего с выхода бита 19 диагностических операций, вырабатывает соответствующий потенциал, поступающий на управляющие входы блока А формирования контрольных разрядов, который при этом формирует контрольные разряды с правильной четностью, В обычных операциях чтения, т,е, . когда адрес, поступающий от процессора , не совпадает с адресом регистра 9 контрольной информации, узел 13 синг хронизации блока. 5 управления в соответствии с присылаемым процессором кодом операции вырабатывает соответст- вующие сигналы управления памятью 6, При этом информация, считанная из памяти блока 6 памяти по адресу, поступившему с выходов управляющего регистра 1, заносится вместе с сопровождающими ее контрольными разрядами на регистр 7. Узел 17 формирования .синдромов блока 8 контроля выходной информации в соответствии с поступившими на ды значениями информационных и контрольных разрядов вырабатывает соответствующие синдромы. Узел 18 обнару жения ошибок по значениям синдромов определяет наличие ошибок в считанно информации и уведомляет Процессор t ошибках в случае необходимости. Деши ратор 16 номера корректируемого разряда по значениям синдрбмов и сигналов, вырабатываемых узлом 18 обнаружения ошибок, определяет номер корректируемого разряда и выдает соответствующие сигналы на управляющие входы регистра 7, по которым инфрр мацйя в регистре в случае необходимости корректируется и затем поступает на вторые информационные входы коммутатора 10. Коммутатор 10 по сигналу, вырабатываемому узлом 12 управления коммутацией 5 управления в соответствии с сигналами, поступающими с выходов дешифратора 3 эл реса, выдает на шины интерфейса информаци10 с выходов информационных , разрядов регистра 7, В случае обнаружения ошибок На регистре. 9 контрольной инфо|р|мации в Ьитах контрольной информации заломиНаются значения синдромов, которые, при обращении процессора к регистру 9 контрольной информации могут быть прочитаны, .. . При обращении проц1ессора в регист 9 контрольной информации с операцией записи дешифратор 3 адреса вырабатывает соответствующий сигнал, поступающий на узел 13 )низации, по которому в узле блокируется выработка управляющих сигналов для бло ка 6 памяти и выдается стрОб, по которому в бит диагностических опера ций регистра 9 контрольной информации заносится соответствующая информация с шин интерфейса. В случае, если процессор обращает ся в регистр 9 контрольной информации с операцией чтения, деимфратор 3 адреса выдает соответствующие сигналы на узел 13 синхронизации и Узел 12 управления коммутацией блока 5 управления, по которым в узле 13 син хронизации блокируется выработка управляющих сигналов для блока 6 памят а в узле управления коммутацией вырабатывается соответствующий сигнал, который переключает коммутатор 10 в направление приема информации с выхо да регистра 9 контрольной информации Эта информация с выхода коммутатора 10 поступает в процессор. Для проверки схем контроля процессор записывает предварительно в регистр 9 контрольной информации бит диагностических операций. При этом узел 12 управления коммутацией блока 5 управления выдает на.управляющие входы блока 4 формирования контрольных разрядов соответствующий, потенциал, по которому этот узел переводится в диагностический режим работы и на выходах устанавливаются заранее определенные значения контрольных разрядов (например, все нули или все единицы. Такой режим работы возкюжен в Случае, есЛи элементы, на которых построен блок формирования контрольных разрядов, имеют управляющие входа. . :. Если в дальнейшем производится запись информации в блок 6 памяти по адресу А, то вместе с записываемой информацией в бгюк 6 памяти записываются и фиксированные значения контрольных разрядов, которые могут и не совпадать со значениями контрольных разрядов, формируемых при обычном рёжие работы узла формирования контрольных разрядов. При последующем чтении информации по этому же адресу А блок В контроля выходной информации, .дол- жен отреагировать соответствуйщим образом на рассогласование информационных и контрольных разрядов. По сигналам, поступающим с узла 18 обнаружения ошибок информации, считанной по адресу А из блока 6 памяти, а также информации, считанной при последующем обращении из регистра Э контрольной информации, процессор судит об исправности блока В контроля выходной информации и узла формирования контрольных разрядов. Так как, манипулируя записываемой информацией, можно создать код несо,ответствия между этой информацией и фиксированными контрольными разрядами, то полнота проверки блока В контроля выходной информации не уступает полноте проверки подобного узла контроля в прототипе. Технико-экономические преимущества предлагаемого устройства для проверки схем контроля в сравнении с базовым объектом заключается в сокращении шин интерфейса, приемопередающего оборудования, и уменьшении времени

. 1015386

для формирования контрольных раз- где рядов.

Экономический эффект, достигамый при использовании изобретения, определяется возможностью сокращения обо- $ рудования и повышения быстродействия и может быть определен по формуле 9 ( Cj Сз)-п ,

ъг

г

1

11

J

I

L-..

I

6

I

- f

IS

t

у

Фиг,1

10

стоимость оборудования шин интерфейса;

стоимость приемопередающего: оборудования;

стоимость оборудования коммутации контрольных разрядов; отношение быстродействия базового объекта к быстродействию созданного.

п

- J

8

.A.

1$

18

17

L-

jj

10

20

rrlJ

из19--«13-

ujff

wi

Фч9.Ъ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ,- - - .- | |||

Авторы

Даты

1983-04-30—Публикация

1981-12-11—Подача