Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, осуществляющих аппаратно-программный контроль запоминающих устройств.

Известно устройство для контроля оборудования памяти, содержащее память, регистры входной, управляющей и выходной информации, узел управления памятью, формирователи контрольных разрядов, дополнительные приемники и передатчики для контрольных раз.рядов и узлы контроля входной и выходной информации m

Недостатком этого устройства явияется невозможность осуществления )проверки узлов контроля без наличия дополнительных шин интерфейса и дополнительного приемо передающего оборудования для приема и передачи контрольных разрядов.

Наиболее близким по техничеакой сущности к изобретению является устройство для тестовой проверки памяти содержащее регистр управляющей информации, регистр входных данных, ре- гистр чтения данных; регистр выходных данных, узлы контроля входных и выходных данных, узел управления памятью, первый и второй узел формироаания-контрольных разрядов, память входной и выходной коммутаторы. Информационные входы .входного коммутатора, подключенного своим выходом к второму информационному входу памяти соединены соответственно с выходом первого узла формирования контрольных разрядов и третьим выходом регистра управляющей информации. Информа1 ионные входы выходного коммутатора, соединенного выходом с входом контрольных разрядов выходного регистра данных, соединены соответственно с выходом второго узла формирования контрольных разрядов и выходом контрольных разрядов регистра чтения данных. Управляющие входы входного и выходного коммутаторов подкхпочены соответственно к второму и третьему выходам узла управления памятью 21.

Недостатком известного устройства является необходимость наличия дополнительных шин интерфейса для передачи контрольных разрядов и невозможность проверки оборудования без этих шин. Кроме того, выбор комбинации контрольных разрядов ограничен .областью свободных адресов памяти, не

занятых программой, так как контрольные разряды соответствуютотдельньм разрядам адреса. Недостатком устройства является также то, что для зада|ния контрольных разрядов при проверке используется часть разрядов адреса, что делает невозможным проверку оборудования при небольшом объеме памяти, т.е. малом количестве адресных шин, либо для осуществления такой проверки требуются дополнитеЛьные шины и дополнительные приемопередающее оборудование.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство с контролем, содержащее блок памяти, выходы которого подключены к входам первого регистра, а входы управления - к выходам группы блока управления, первый выход которого соединен с управляющим входом первого регистра, второй выход - с управляющим входом выходного коммутатора, а третий выход и входы . группы блока управления являются соответственно первьм выходом и входами управления устройства, выходы первой группы первого регистра подключены к входам первой группы блока контроля, а вторые выходы первого регистра - к входам второй группы блока контроля и выходного коммутатора, входы первой группы которого соединены с выходами группы блока контроля, выходы выходного коммутатора являются информационными выходами устройства, адресные и информационные входы первой группы блока памяти являются соответственно адресными и ин формационными входами устройства, информационные входы второй группы подключены к выходам входного кс ммутатора, входы первой группы которого соединены с выходами блока кодирования, входы которого подключены к информационным входам первой группы блока памяти, первый и второй выходы блока контроля являются соответственно вторым и третьим выходами управления устройства, в него введены дешифратор и второй регистр, причем входы дешифратора соединены с адресньми входами блока памяти, а выходы - с входами второй груцпы блока управления, входы второго регистра подключены к информационньм входам первой группы блока памяти, управляняций

вход - к четвертому выходу блока управления выход второго регистра к управляющему входу, а выходы группы - к входам второй группы входного коммутатора соответственно. 5

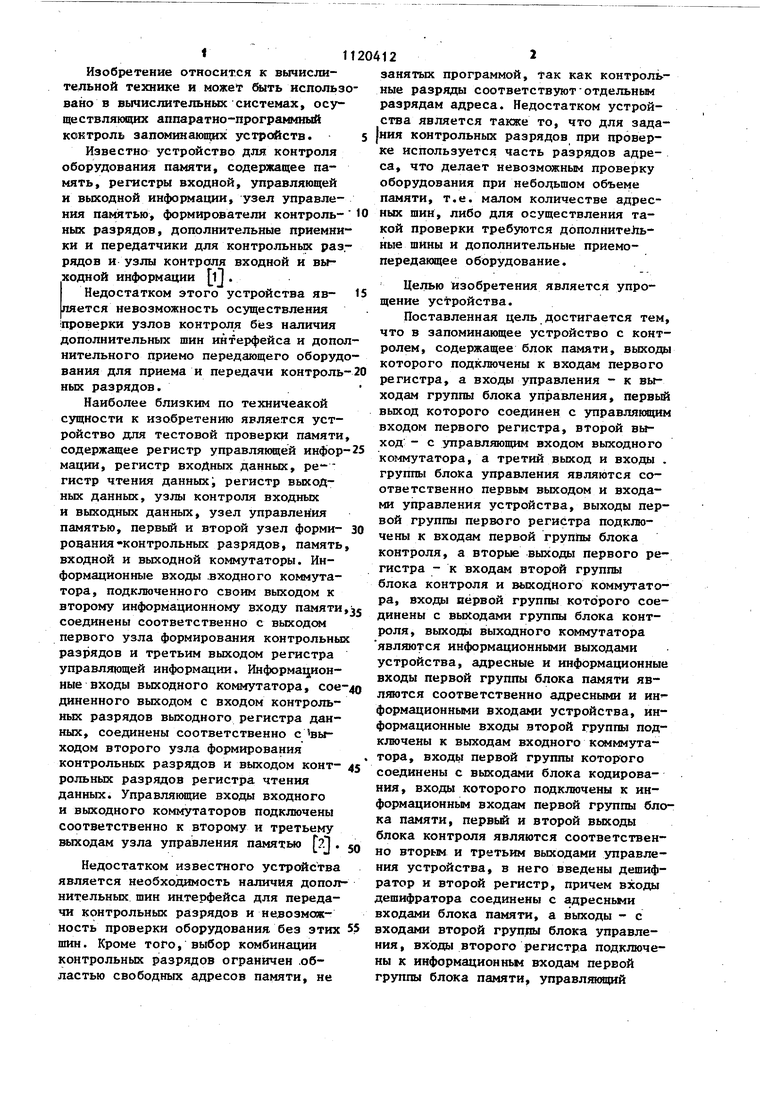

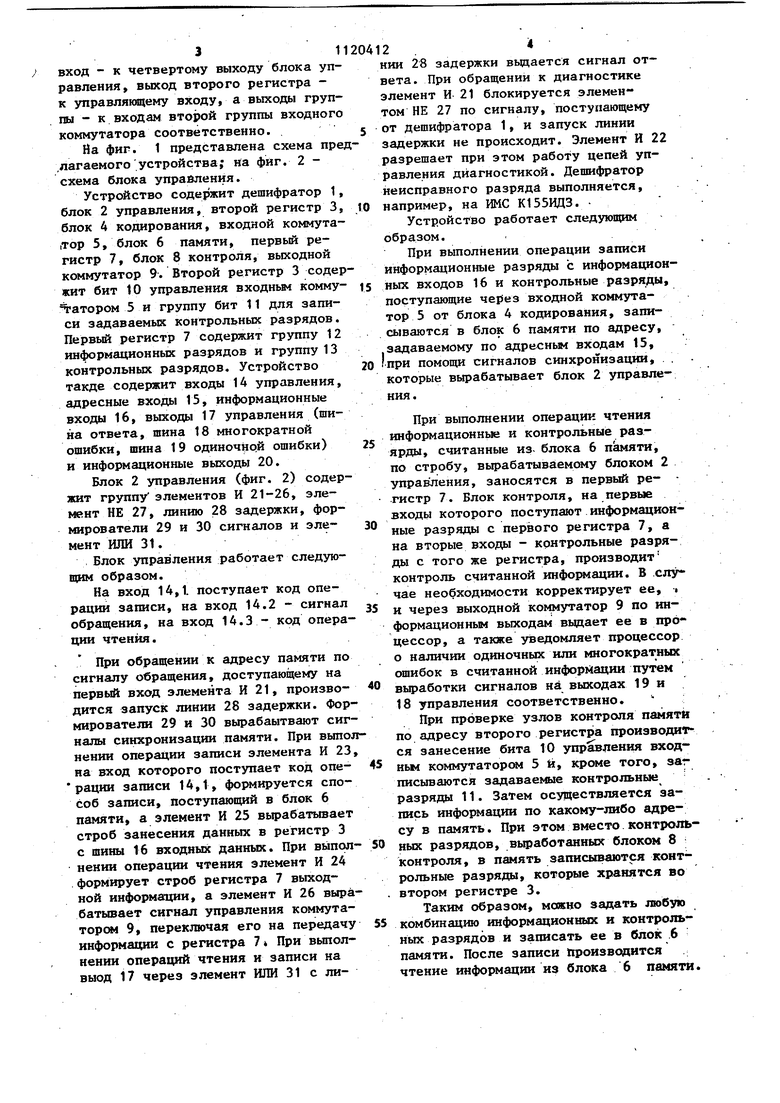

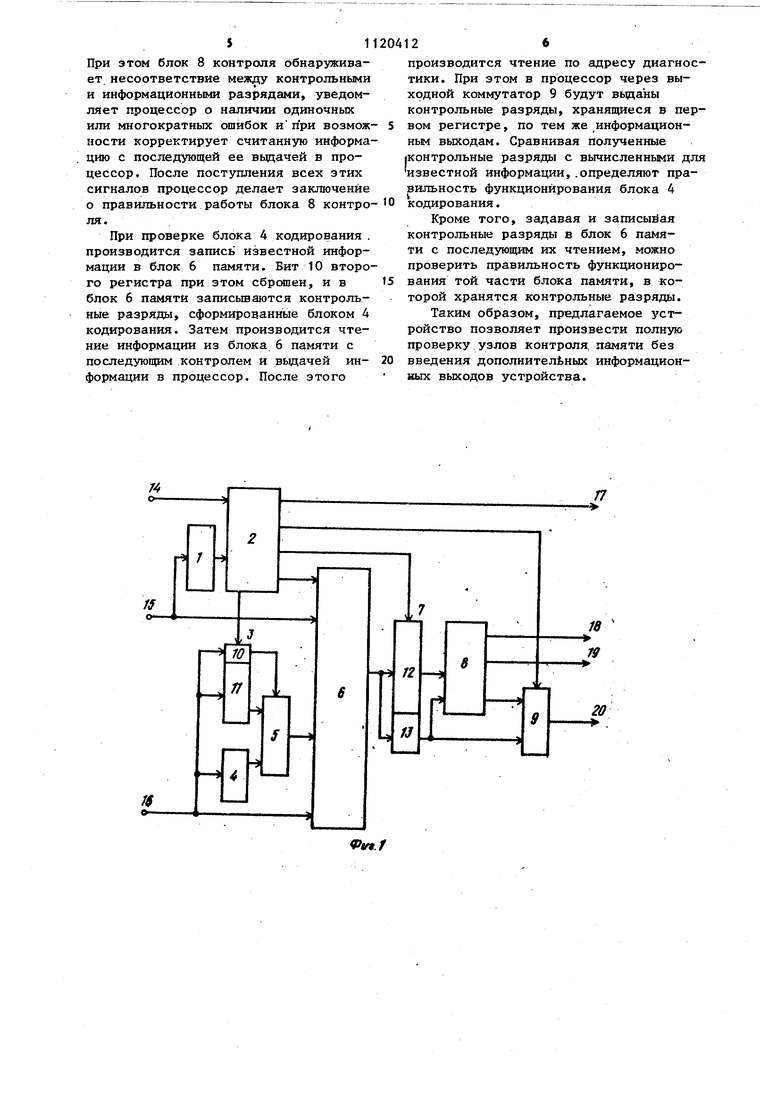

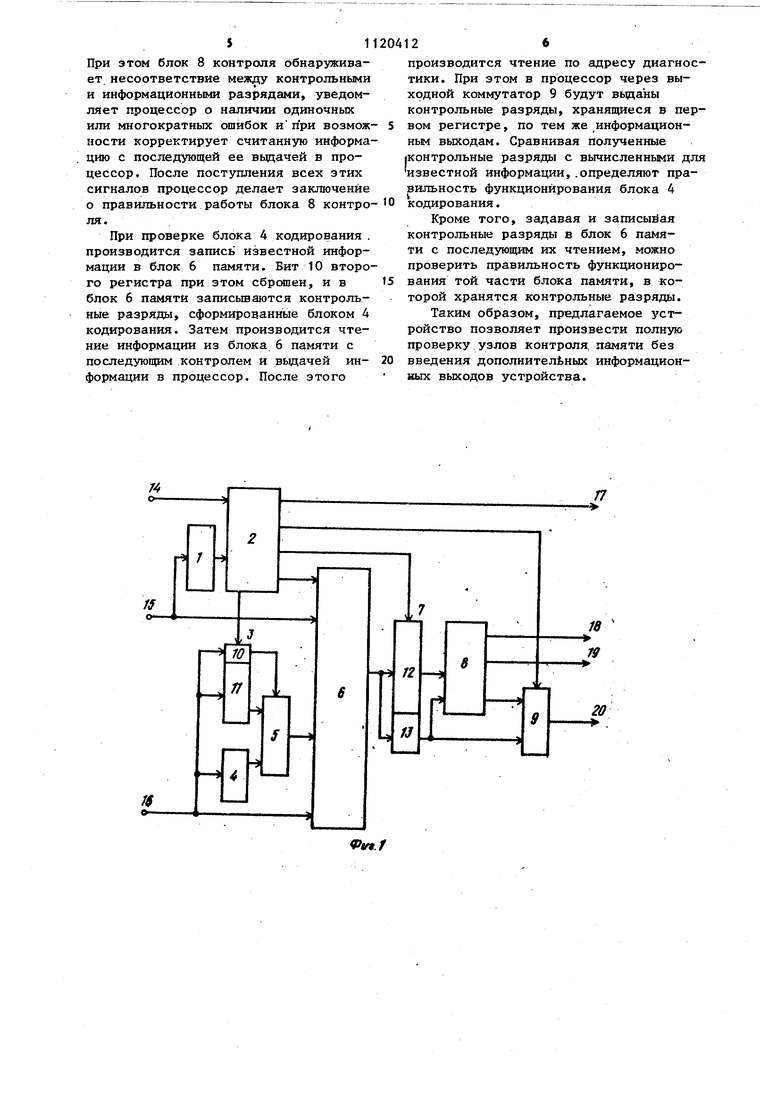

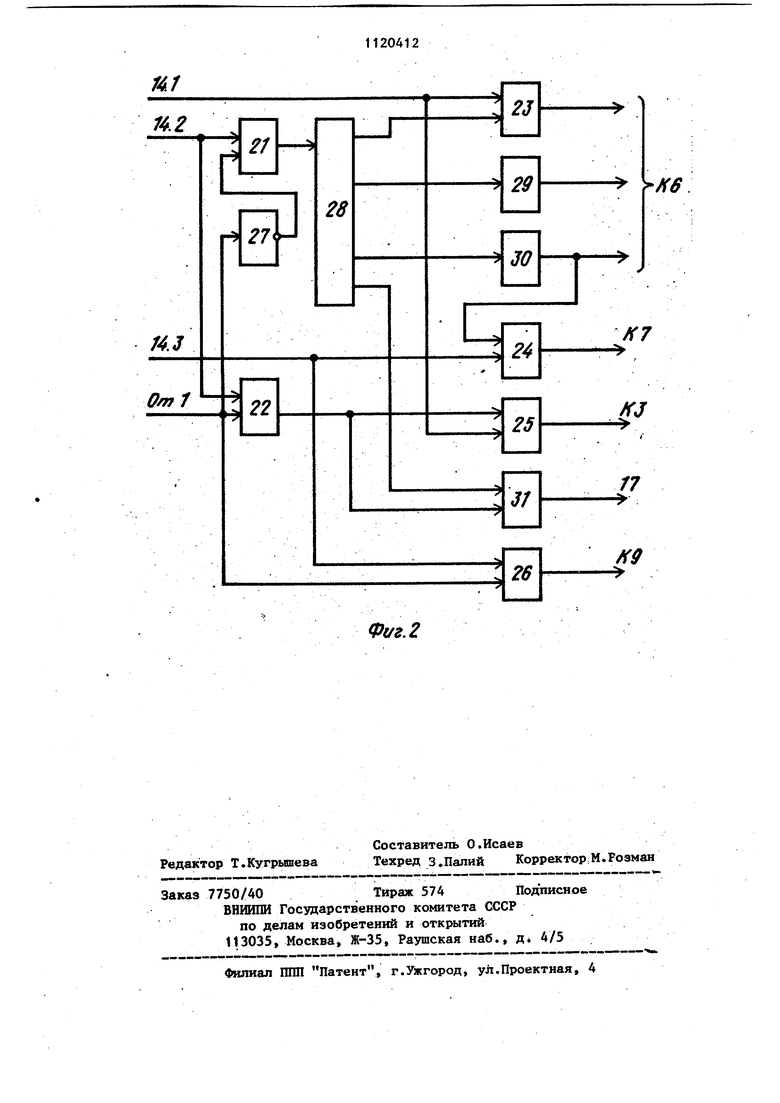

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 схема блока управления.

Устройство содержит дешифратор 1, блок 2 управления, второй регистр 3, ю блок 4 кодирования, входной коммута|Тор 5, блок 6 памяти, первый регистр 7, блок 8 контроля, выходной коммутатор 9. Второй регистр 3 содержит бит 10 управления входньм комму- 15 атором 5 и группу бит 11 для записи задаваемых контрольных разрядов. Первый регистр 7 содержит группу 12 информационных разрядов и группу 13 контрольных разрядов. Устройство 20 такде содержит входы 14 управления, адресные входа 1 15, информационные входы 16, выходы 17 управления (шина ответа, шина 18 многократной ошибки, шина 19 одиночной ошибки) 25 и информационные выходы 20.

Блок 2 управления (фиг. 2) содержит группу элементов И 21-26, элемент НЕ 27, линию 28 задержки, формирователи 29 и 30 сигналов и эле- зо мент ИЛИ 31.

Блок управления работает следующим образом.

На вход 14,1. поступает код операции записи, на вход 14.2 - сигнал ,с обращения, на вход 14.3- код операции чтения.

При обращении к адресу памяти по сигналу обращения, доступающему на первый вход элемента И 21, произво- 0 дится запуск линии 28 задержки. Формирователи 29 и 30 вырабаытвают сигналы синхронизации памяти. При выполнении операции затшси элемента И 23, на вход которого поступает код one- 45 рации записи 14,1, формируется способ записи, поступающий в блок 6 памяти а элемент И 25 вьфабатывает строб занесения данных в регистр 3 с щины 16 входных данных. При выпрл- 50 нении операции чтения элемент И 24 формирует строб регистра 7 выходной информа-ции, а элемент И 26 вырабатывает сигнал управления коммутатором 9, переключая его на передачу 55 информации с регистра 7 При выполнении операций чтения и записи на выод 17 через элемент ИЛИ 31 с линии 28 задержки вьщается сигнал ответа. При обращении к диагностике элемент И 21 блокируется элементом НЕ 27 по сигналу, поступающему от дешифратора 1, и запуск линии задержки не происходит. Элемент И 22 разрешает при этом работу цепей управления диагностикой. Дешифратор неисправного разряда выполняется, например, на ИМС К155ИДЗ.

Устройство работает следующим образом. .

При выполнении операции записи информационные разряды с информационных входов 16 и контрольные разряды, поступающие через входной коммутатор 5 от блока 4 кодирования, записываются в блок 6 памяти по адресу, задаваемому по адресным входам 15, при помощи сигналов синхронизации, которые вырабатывает блок 2 управления.

При выполнении операции чтения информационные и контрольные разярды, считанные из. блока 6 памяти, по стробу, вырабатываемому блоком 2 управления, заносятся в первый ре- гистр 7. Блок контроля, на первые входы которого поступают информационные разряды с первого регистра 7, а на вторые входы - контрольные разряды с того же регистра, производит контроль считанной информации. В .слу чае необходимости корректирует ее, и через выходной коммутатор 9 по информационным выходам выдает ее в процессор, а также у1ведомляе т процессор о наличии одиночньк или многократных ошибок в считанной информации путем выработки сигналов на выходах 19 и 18 управления соответственно.

При проверке узлов контроля памяти по адресу второго регистра производится занесение бита 10 упр ления входньм коммутаторе 5 и, кроме того, заг писываются задаваемые контрольные разряды 11. Затем осуществляется запись информации по какому-либо адресу в память. При этом вместо.контрольных разрядов, выработанных блоком 8 контроля, в память записываются контрольные разряды, которые хранятся во втором регистре 3.

Таким образом, можно задать любую комбинацию информационных и контрольных разрядов и записать ее в блок .6 памяти. После записи производится чтение информации из блока 6 памяти $ 11 при этом блок 8 контроля обнаруживает несоответствие между контрольньми и информационными разрядами, уведомляет процессор о наличии одиночных или многократных ошибок и при возможности корректирует считанную информацию с последующей ее вьщачей в процессор. После поступления всех зтих сигналов процессор делает заключение о правильности работы блока 8 контро При проверке блока 4 кодирования . производится запись известной информации в блок 6 памяти. Бит 10 второ го регистра при этом сбрсяпен, и в блок 6 памяти записьшаются контрольные разряды, сформированные блоком 4 кодирования. Затем производится чтение информации из блока 6 памяти с последующим контролем и вьщачей информации в процессор. После этого 2 производится чтение по адресу диагностики. При этом в процессор через выходной коммутатор 9 будут вьщаны контрольные разряды, хранящиеся в первом регистре, по тем же информационных выходам. Сравнивая полученные (Контрольные разряды с вычисленньми для известной информации,.определяют правильность функционирования блока 4 кодирования. Кроме того, задавая и записыйая контрольные разряды в блок 6 памяти с последующим их чтением, можно проверить правильность функционирования той части блока памяти, в которой хранятся контрольные разряды. Таким образом, предлагаемое устройство позволяет произвести полную проверку узлов контроля, памяти без введения дополнительных информационных выходов устройства.

Ф(/г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| Устройство для проверки узлов контроля памяти | 1981 |

|

SU1003089A1 |

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| Запоминающее устройство | 1985 |

|

SU1298800A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для сопряжения основной памяти с процессором | 1982 |

|

SU1037236A1 |

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОНТРОЛЕМ, содержащее блок памяти, выходы которого подключены к входам первого регистра, а входы управленияк выходам группы блока зшравления, пе-рвьй вых,РД которого соединен с управляющим входом первого регистра, второй выход - с управляющим входом выходного коммутатора, а третий выход и входы первой групйы блока управления являются соответственно первым выходом и входами управления устройства, выходы первой группь первого регистра подключены к входам первой группы блока контроля, а вторые выходы первого регистра - к входам второй группыблока контроля и выходного коммутатора, входы первой группы которого соединены с выходами группы блока контроля, выходы выходного коммутатора являются информационными выходами устройства, адресные и информационные входы первой группы блока памяти являются соответственно адресными и информационными входами устройства, информационные входы второй группы подключены к выходам входного коммутатора, входы первой группы которого соединены с выходами блока кодирования, входы которого подключены к информационным входам первой группы блока памяти, первый и второй выходы блока контроля являются соответственно вторым и третьим выходами управления.устройства, отличающе еся тем, что, с целью упрощения устройства, в него введены дешифратор и второй регистр, -причем входы дешифратора соединены | с адресньми входами блока памяти, ND а выходы - с входами второй группы э блока управления, входы второго ; 42 регистра подключены к информационным входам первой группь блока памяти, | .управляниций вход - к четвертому в|.коto 1ду блока управления, выход второго ; регистра - к управляющему входу, а выходы группы - к входам второй группы входного коммутатора соответственно

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-02-22—Подача