Изобретение относится к вычислительной технике и может найти применение в вычислительных системах, осуществляющих программный контроль запоминающих устройств.

Известны устройства содержащие регистры входной, управляющей и выходной информации, узел управления памятью, формирователи контрольных разрядов, узлы контроля входной и выходной информаЦии 1.

Недостатком этого устройства является ограниченность функциональных возможностей.

Наиболее близким по технической сущности к предлагаемому является устройство для .тестового контроля памяти, содержащее регистр управляющей информации, регистр входных данных, регистр чтения данных, регистр выходных данных, узлы контроля управляющей информации, входных и выходных данных, узел управления памятью, первый узел формирования ко11трольных разрядов, второй узел формирования контрольных разрядов, память, входной коммутатор и выходной коммутатор, причем информационные входы входного комм.утатора, подключенного своим выходом к второму информационному входу памяти, соединены соответственно с выходом первого уела формирования контрольных разрядов и третьим выходом регистра управляющей информации, информационные входы выходного коммутатора, соединенного выходом с входом контрольных разрядов выходного регистра данных, соединены соответственно с выходом второго узла формирования контрольных разрядов и выходом контрольных разрядов регистра чтения данных, управляющие входы входного и выходного коммутаторов подключены соответственно к второму и третьему выходам узла управления памятью 2.

Недостатком прототипа является то, что для задания кода контрольных разрядов при проверке используется часть адресных разрядов, что делает невозможным проверку памяти с ограниченным объемом из-за малого количества адресных щин, и требуется дополнительное приемопередающее оборудование, поскольку для передачи контрольных разрядов и специального признака диагностических операций необходимо наличие дополнительных щин интерфейса, а выбор комбинации контрольных разрядов ограничен областью свободных адресов памяти, не занятых программой, так как код контрольных разрядов соответствует отдельным адресам, что усложняет устройство и ограничивает область его применения.

Цель изобретения - упрощение устройства-.

Поставленная цель достигается тем, что в устройство для тестового контроля памяти, содержащее формирователь контрольных сигналов, коммутаторы, регистр считанной информации, входы которого являются информационными входами устройства, одни из выходов соединены с одними из входов блока контроля считанной информации, а другие выходы - с другими входами блока контроля считанной информации и одними из входов блока коррекции, другие входы которого подключены к одним из выходов блока контроля Считанной информации, а выходы - к информационным входам первого коммутатора, управляющие входы которого являются входами обращения устройства, выход первого коммутатора и другой выход блока контроля считанной информации являются одними из выходов устройства, другими выходами которого являются выходы второго коммутатора, одни из входов которого подключены к выходам формирователя контрольных сигналов, входы которого являются управляющими входами устройства, введены блоки местного управления, третий коммутатор, регистр контрольной информации и регистры управляющих сигналов, причем одни из входов третьего коммутатора и первого блока местного управления объединены и являются адресными входами устройства, другие входы третьего коммутатора соединены соответственно с одними из входов блока контроля считанной информации, с входами формирователя контрольных сигналов и входами регистров управляющих сигналов, с управляющими входами первого коммутатора, регистра контрольной информации, второго блока местного управления и регистров управляющих сигналов и с выходами второго блока местного управления, входы которого подключены соответственно к одним из выходов первого блока местного управления и к другим выходам блока контроля считанной информации, управляющие входы которого соединены с другими выходами первого блока местного управления, другие входы второго коммутатора подключены соответственно к одним из выходов первого блока местного управления и к контрольным входам первого коммутатора и выходам регистра контрольной информации, входы которого соединены с выходами третьего коммутатора.

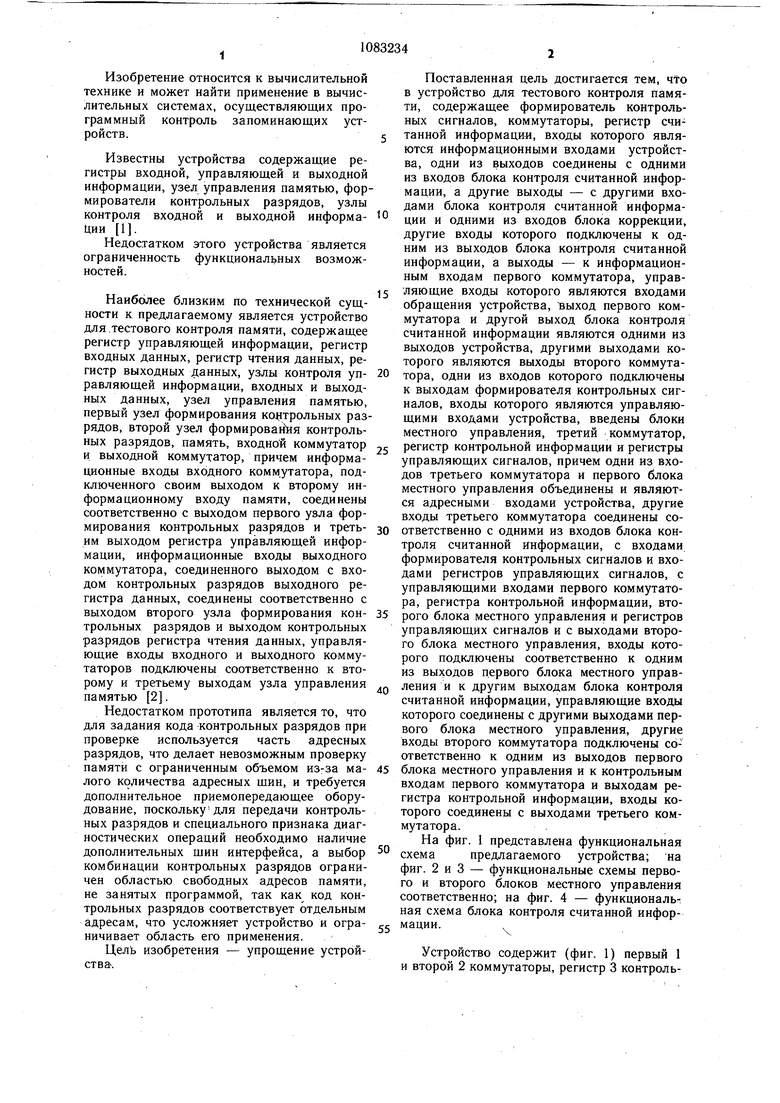

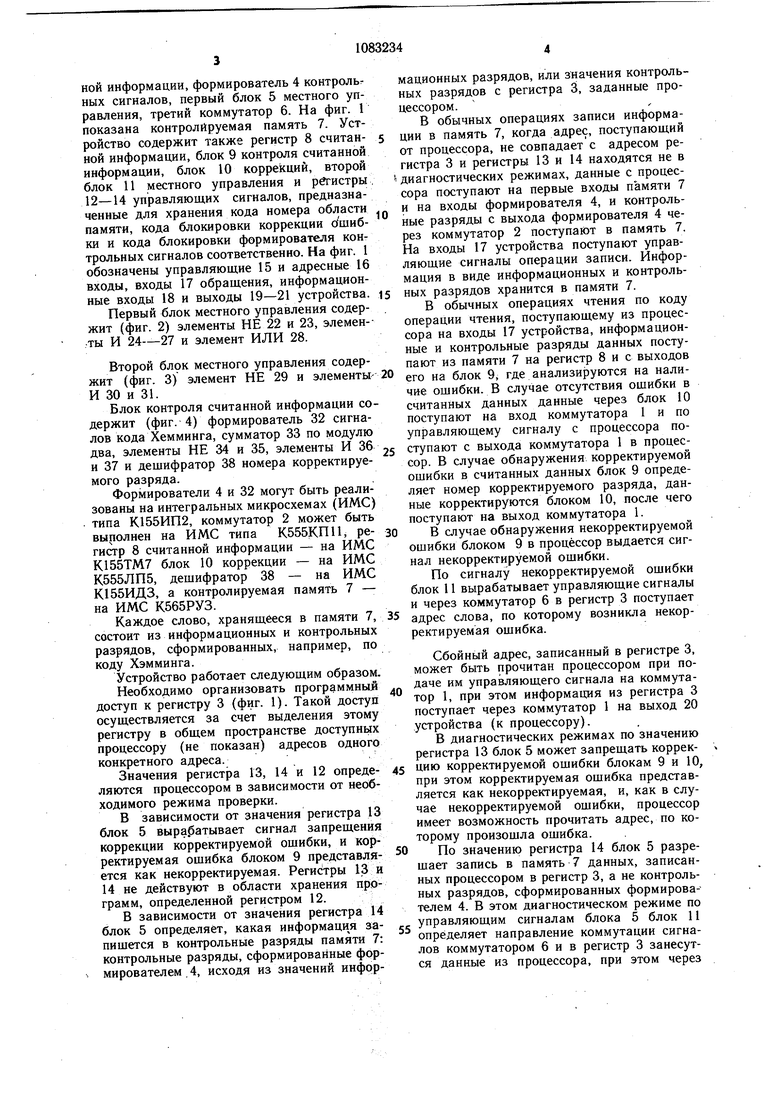

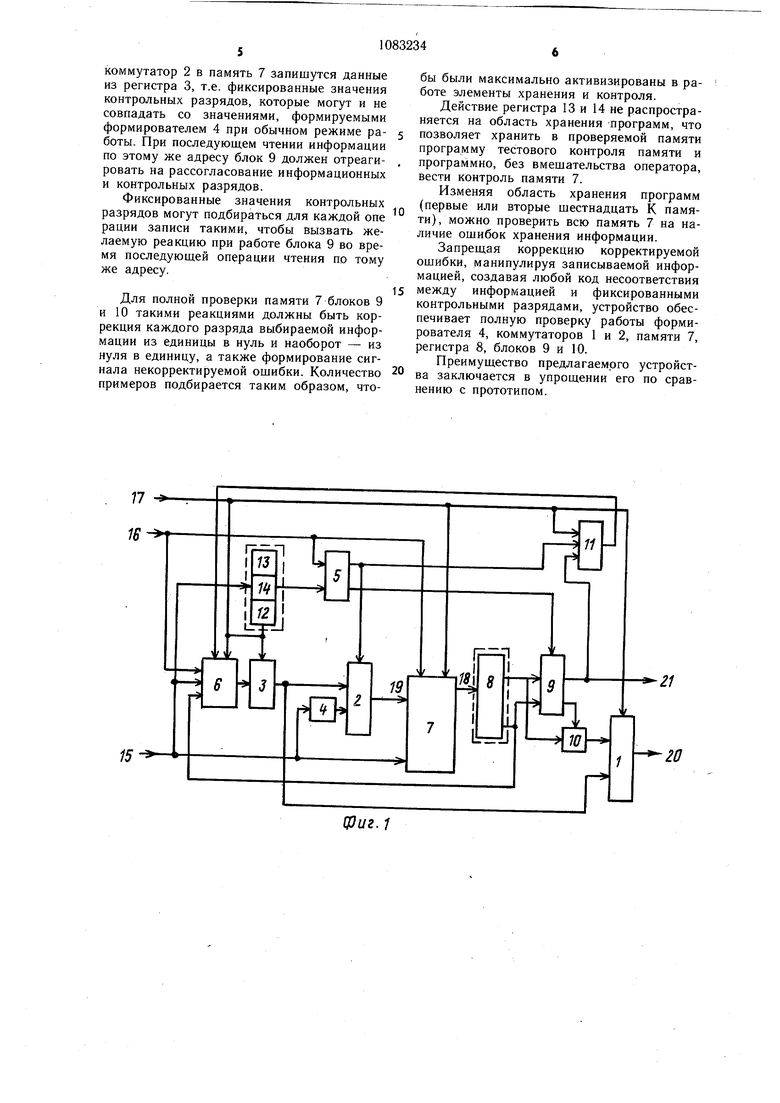

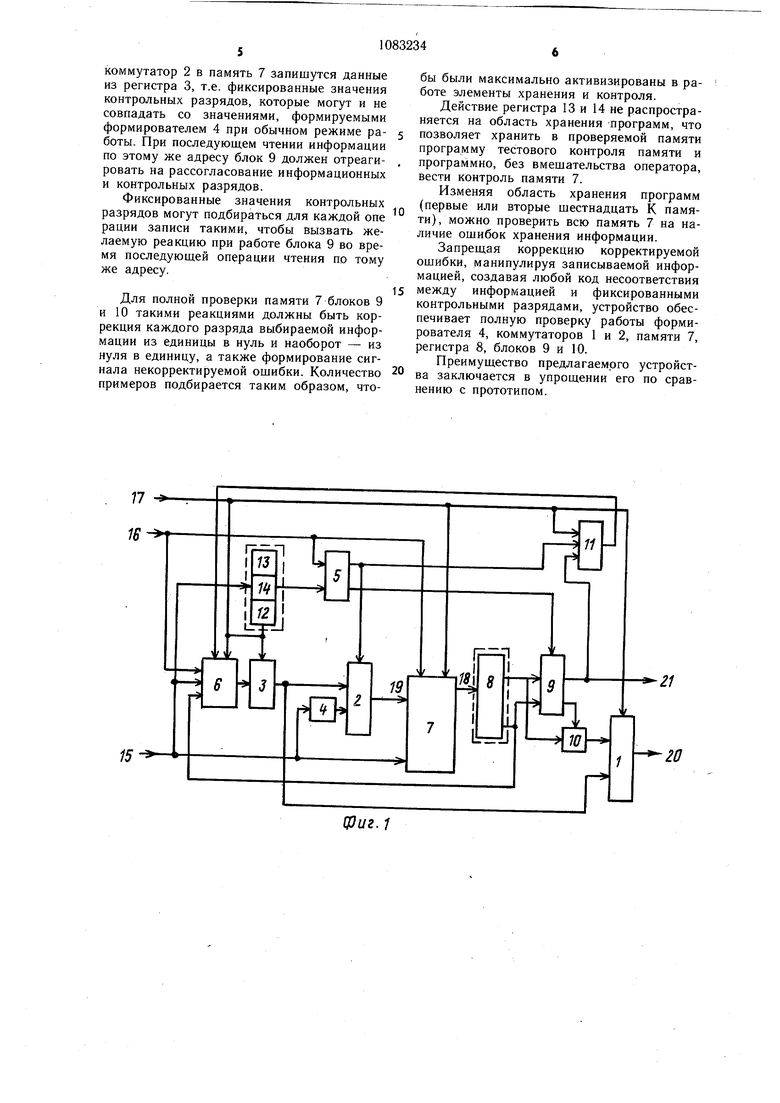

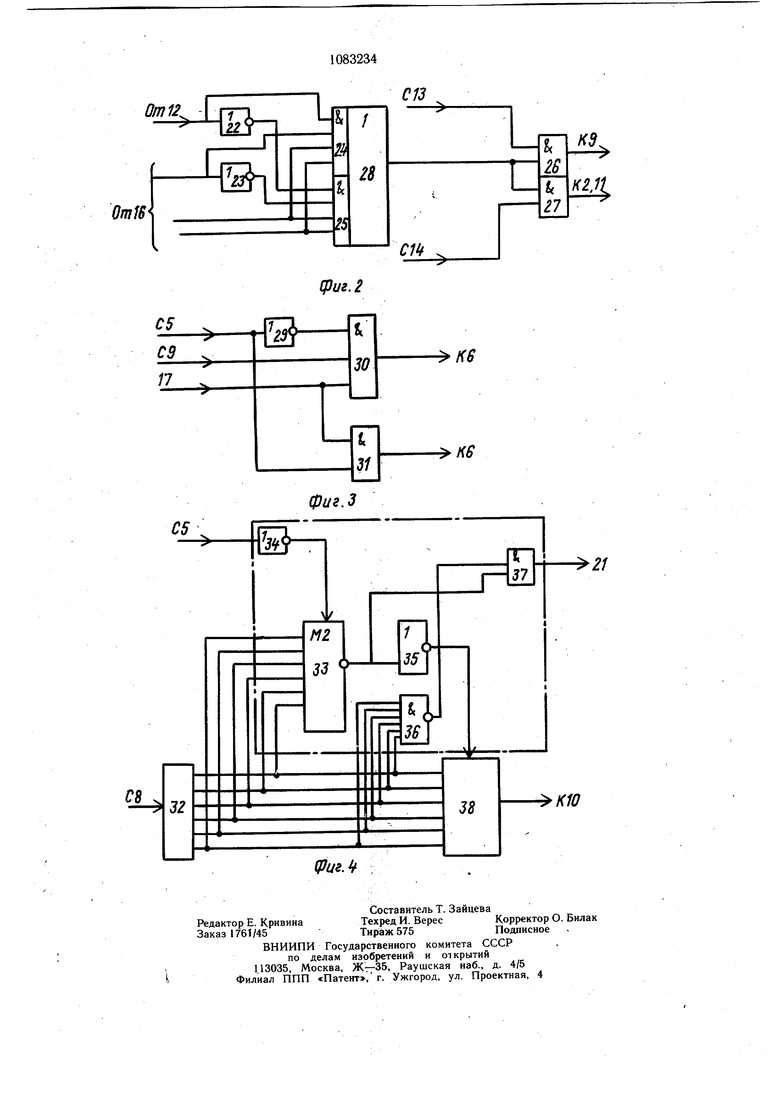

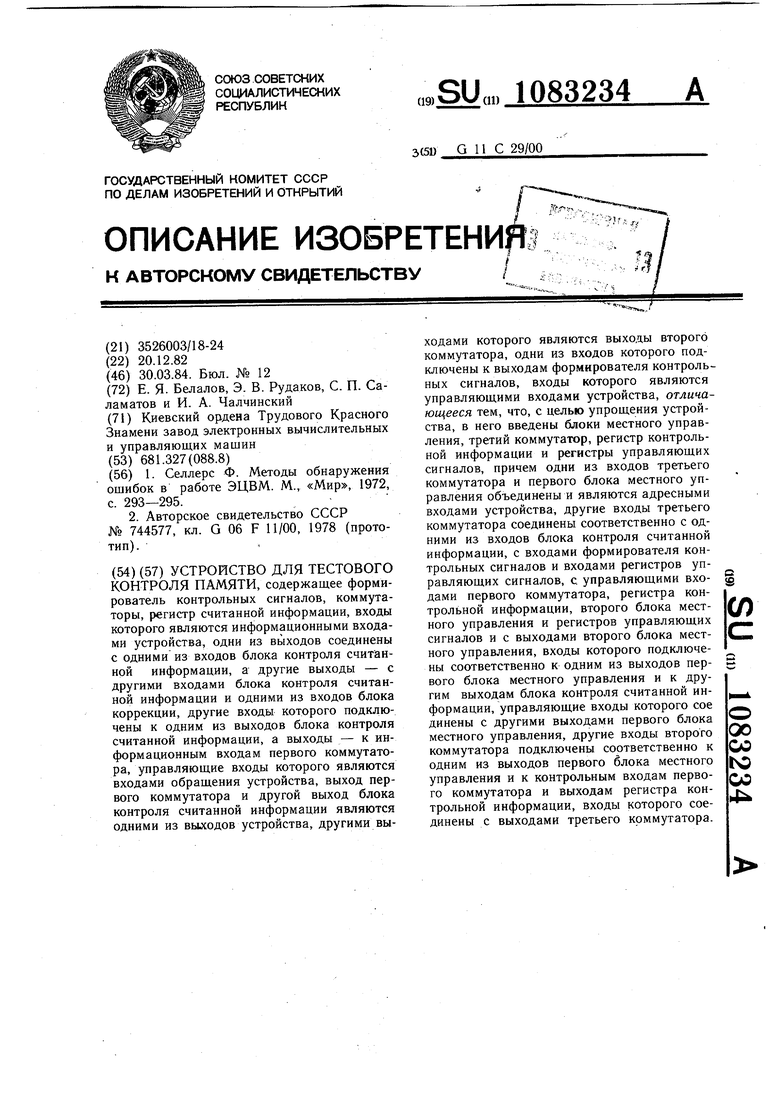

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы первого и второго блоков местного управления соответственно; на фиг. 4 - функциональная схема блока контроля считанной информации.

Устройство содержит (фиг. 1) первый 1 и второй 2 коммутаторы, регистр 3 контрольной информации, формирователь 4 контрольг ных сигналов, первый блок 5 местного управления, третий коммутатор 6. На фиг. 1 показана контролируемая память 7. Устройство содержит также регистр 8 считанной информации, блок 9 контроля считанной информации, блок 10 коррекций, второй блок 11 местного управления и рй-истры 12-14 управляющих сигналов, предназначенные для хранения кода номера области памяти, кода блокировки коррекции с/шибки и кода блокировки формирователя контрольных сигналов соответственно. На фиг. 1 обозначены управляющие 15 и адресные 16 входы, входы 17 обращения, информационные входы 18 и выходы 19-21 устройства. Первый блок местного управления содержит (фиг. 2) элементы НЕ 22 и 23, элемен-ты И 24-27 и элемент ИЛИ 28.

Второй блок местного управления содержит (фиг. 3) элемент НЕ 29 и элементыИ 30 и 31.

Блок контроля считанной информации содержит (фиг. 4) формирователь 32 сигналов кода Хемминга, сумматор 33 по модулю два, элементы НЕ 34 и 35, элементы И 36 и 37 и дешифратор 38 номера корректируемого разряда.

Формирователи 4 и 32 могут быть реализованы на интегральных микросхемах (ИМС) типа К155ИП2, коммутатор 2 может быть выполнен на ИМС типа К555КП11, регистр 8 считанной информации - на ИМС К155ТМ7 блок 10 коррекции - на ИМС К555ЛП5, дешифратор 38 - на ИМС К155ИДЗ, а контролируемая память 7 - иа ИМС К565РУЗ.

Каждое слово, хранящееся в памяти 7, состоит из информационных и контрольных разрядов, сформированных, например, по коду Хэмминга.

Устройство работает следующим образом.

Необходимо организовать программный доступ к регистру 3 (фиг. 1). Такой доступ осуществляется за счет выделения этому регистру в общем пространстве доступных процессору (не показан) адресов одного конкретного адреса.

Значения регистра 13, 14 и 12 определяются процессором в зависимости от необходимого режима проверки.

В зависимости от значения регистра 13 блок 5 вырабатывает сигнал запрещения коррекции корректируемой ошибки, и корректируемая ошибка блоком 9 представляется как некорректируемая. Регистры 13 и 14 не действуют в области хранения программ, определенной регистром 12.

В зависимости от значения регистра 14 блок 5 определяет, какая информаци я запишется в контрольные разряды памяти 7: контрольные разряды, сформированные формирователем .4, исходя из значений информационных разрядов, или значения контрольных разрядов с регистра 3, заданные процессором.

В обычных операциях записи информации в память 7, когда адрес, поступающий от процессора, не совпадает с адресом регистра 3 и регистры 13 и 14 находятся не в диагностических режимах, данные с процессора поступают на первые входы памяти 7

и на входы формирователя 4, и контрольные разряды с выхода формирователя 4 через коммутатор 2 поступают в память 7. На входы 17 устройства поступают управляющие сигналы операции записи. Информация в виде информационных и контрольных разрядов хранится в памяти 7.

В обычных операциях чтения по коду операции чтения, поступающему из процессора на входы 17 устройства, информационные и контрольные разряды данных поступают из памяти 7 на регистр 8 и с выходов

0 его на блок 9, где анализируются на наличие ошибки. В случае отсутствия ошибки в считанных данных данные через блок 10 поступают на вход коммутатора 1 и по управляющему сигналу с процессора по5 ступают с выхода коммутатора 1 в процессор. В случае обнаружения корректируемой ошибки в считанных данных блок 9 определяет номер корректируемого разряда, данные корректируются блоком 10, после чего поступают на выход коммутатора 1.

0 В случае обнаружения некорректируемой ошибки блоком 9 в процессор выдается сигнал некорректируемой ошибки.

По сигналу некорректируемой ошибки блок 11 вырабатывает управляющие сигналы и через коммутатор 6 в регистр 3 поступает

5 адрес слова, по которому возникла некорректируемая ощибка.

Сбойный адрес, записанный в регистре 3, может быть прочитан процессором при подаче им управляющего сигнала на коммута0тор 1, при этом информация из регистра 3 поступает через коммутатор 1 на выход 20 устройства (к процессору).

В диагностических режимах по значению регистра 13 блок 5 может запрещать коррек5 цию корректируемой ошибки блокам 9 и 10, при этом корректируемая ошибка представляется как некорректируемая, и, как в случае некорректируемой ошибки, процессор имеет возможность прочитать адрес, по которому произошла ошибка. 0 По значению регистра 14 блок 5 разрешает запись в память 7 данных, записанных процессором в регистр 3, а не контрольных разрядов, сформированных формирователем 4. В этом диагностическом режиме по управляющим сигналам блока 5 блок 11

5

определяет направление коммутации сигналов коммутатором бив регистр 3 занесутся данные из процессора, при этом через коммутатор 2 в память 7 запишутся данные из регистра 3, т.е. фиксированные значения контрольных разрядов, которые могут и не совпадать со значениями, формируемыми формирователем 4 при обычном режиме работы. При последующем чтении информации по этому же адресу блок 9 должен отреагировать на рассогласование информационных и контрольных разрядов. Фиксированные значения контрольных разрядов могут подбираться для каждой one рации записи такими, чтобы вызвать желаемую реакцию при работе блока 9 во время последующей операции чтения по тому же адресу. Для полной проверки памяти 7 блоков 9 и 10 такими реакциями должны быть коррекция каждого разряда выбираемой информации из единицы в нуль и наоборот - из нуля в единицу, а также формирование сигнала некорректируемой ощибки. Количество примеров подбирается таким образом, чтобы были максимально активизированы в работе элементы хранения и контроля. Действие регистра 13 и 14 не распространяется на область хранения программ, что позволяет хранить в проверяемой памяти программу тестового контроля памяти и программно, без вмещательства оператора, вести контроль памяти 7. Изменяя область хранения программ (первые или вторые шестнадцать К памяти), можно проверить всю память 7 на наличие ошибок хранения информации. Запрещая коррекцию корректируемой ошибки, манипулируя записываемой информацией, создавая любой код несоответствия между информацией и фиксированными контрольными разрядами, устройство обеспечивает полную проверку работы формирователя 4, коммутаторов 1 и 2, памяти 7, регистра 8, блоков 9 и 10. Преимущество предлагаемого устройства заключается в упрощении его по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для проверки узлов контроля памяти | 1981 |

|

SU1003089A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для проверки схем контроля памяти | 1981 |

|

SU1015386A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ПАМЯТИ, содержащее формирователь контрольных сигналов, коммутаторы, регистр считанной информации, входы которого являются информационными входами устройства, одни из вь1ходов соединены с одними из входов блока контроля считанной информации, а другие выходы - с другими входами блока контроля считанной информации и одними из входов блока коррекции, другие входы которого подключены к одним из выходов блока контроля считанной информации, а выходы - к информационным входам первого коммутатора, управляющие входы которого являются входами обращения устройства, выход первого коммутатора и другой выход блока контроля считанной информации являются одними из выходов устройства, другими ходами которого являются выходы второго коммутатора, одни из входов которого подключены к выходам формирователя контрольных сигналов, входы которого являются управляющими входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены блоки местного управления, третий коммутатор, регистр контрольной информации и регистры управляющих сигналов, причем одни из входов третьего коммутатора и первого блока местного управления объединены и являются адресными входами устройства, другие входы третьего коммутатора соединены соответственно с одними из входов блока контроля считанной информации, с входами формирователя контрольных сигналов и входами регистров упi равляющих сигналов, с управляющими входами первого коммутатора, регистра конСЯ трольной информации, второго блока местного управления и регистров управляющих сигналов и с выходами второго блока местного управления, входы которого подключены соответственно к одним из выходов первого блока местного управления и к другим выходам блока контроля считанной информации, управляющие входы которого сое динены с другими выходами первого блока ОС местного управления, другие входы второго оо ю коммутатора подключены соответственно к одним из выходов первого блока местного управления и к контрольным входам первоСАЭ го коммутатора и выходам регистра кон4 трольной информации, входы которого соединены с выходами третьего коммутатора.

иг.1

OmJS

(риг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., «Мир, 1972, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПОДАЧИ УГЛЯ В ТЕНДЕР ПАРОВОЗА | 1920 |

|

SU293A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для тестовой проверки памяти | 1978 |

|

SU744577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-20—Подача