Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля цифровых блоков радиоэлектронной аппаратуры.

Известно устройство контроля многовыходных цифровых узлов, содержащее генератор тестовых наборов, свертку по модулю два, регистр сдвига, сумматор по модулю два, лндикатор и по числу выходнцос кангшов регистры сдвига с сумматором по моду- лю два в цепи обратной связи С 3

Недостатком такого устройства является аппаратурная .сложность и связанная с этим низкая надежность его работы.

Наиболее близким к изобретению техническим решением является сигнатурный анализатор для контроля цифровых блоков, содержсцций блок управления, соединенный своим первым выхвдом через задатчик тедтов с входами контролируемого блока, вторым и .третьим выходами соответственно с первым и вторым входами блока сжатия информации, блок питания, контактный зонд и индикатор сигнатуры С 23.

Недостатком известного сигнатурного анализатора является, низкая достоверность контроля вследсдвие того, что в момент получения сигратуры может иметь место нарушение контакта между зондом и контрр шруемой точкой блока. Это приводит к искажению значения снимаемой сигнатуры в данной точке и принятию неправильного ре10шения о годности блока.

Цель изобретения - повьгиение достоверности контроля.

Поставленная цель достигается тем, что в сигнатурный анализатор для

15 контроля цифровых блоков, содержащий блок управления, соединенный первым входом через задатчик тестов с входами контролируемого блока, вторым и третьим выходами соответст20венно с первым и BTOEftjM входами блока сжатия информации, блок питания, контактный зонд, соединенный входом с выходом контролируемого блока, и первый индикатор, введены первый и вто25рой резисторы, первый и второй дифференциальные усилители, первый и второй элементы И,второй индикатор, .триггер и буферный регистр, соединенный выходом с входом первого индикатора, первым входом - с выходом

блока сжатия информации, вторым входом - с выходом первого элемента И, первый вход которого соединен с четвертым выходом блока управления, второй вход - с выходом триггера, соединенного первым входом с вторым входом блока сжатия информации, вторым входом - с входом второго индикатора и выходом второго элемента И, первый.вход которого соединен с выходом первого дифференциального усилителя, второй вход - с третьим входом блока сжатия информации и выходом . второго дифференциального усилителя, соединенного первым входом с первым выходом блока питания, вторым входом с первым входом второго дифференциального усилителя, выходом зонда и первыми выводами первого и второго резисторов, второй вход первого дифференциального усилителя соединен с вторым выходом блока питания, третий и четвертый выходы которого соединены соответственно с вторыми выводами первого и второго резисторов.

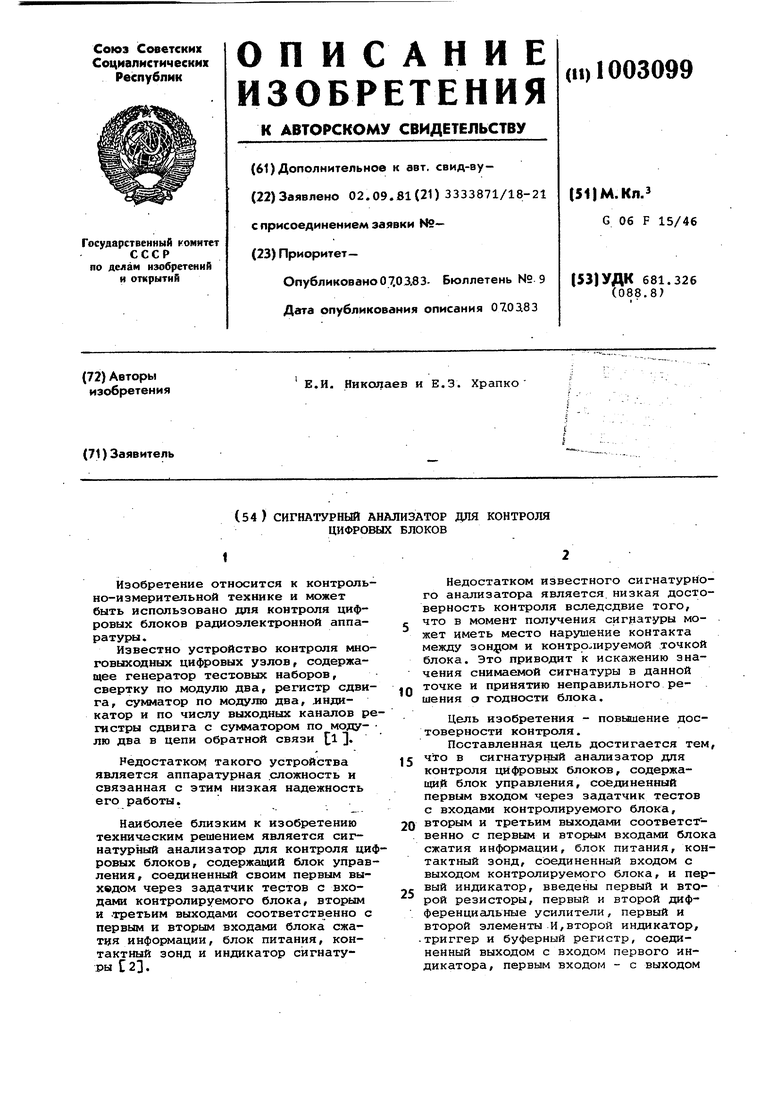

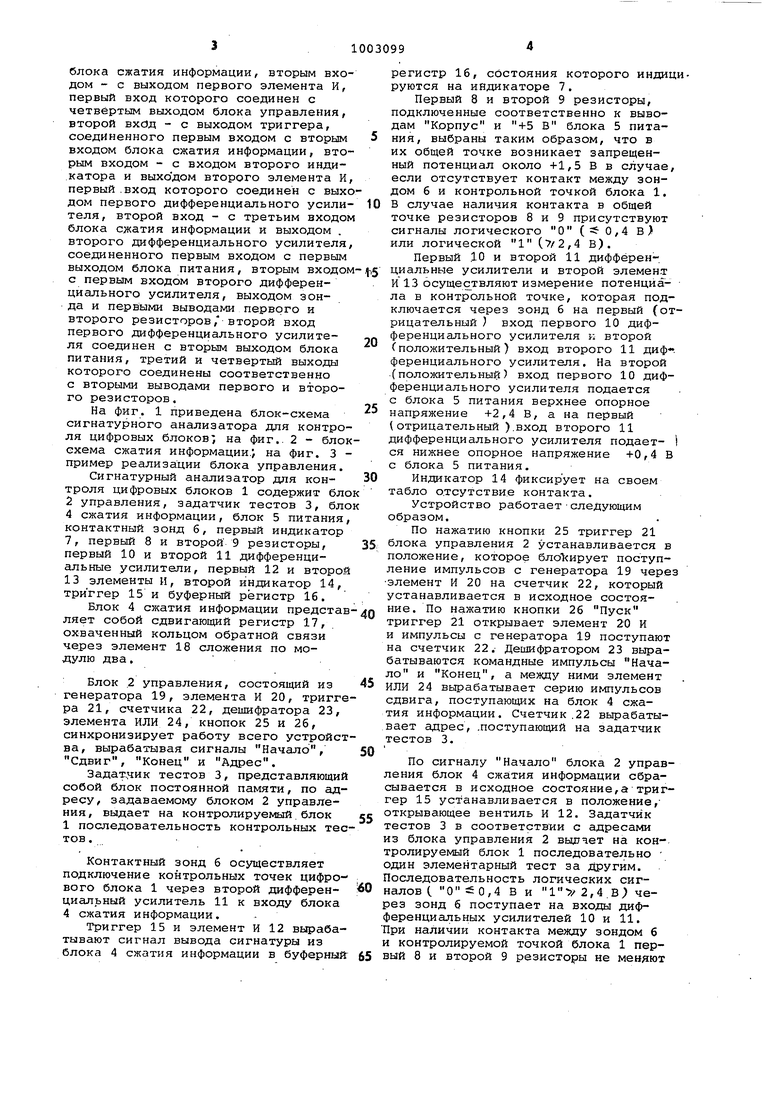

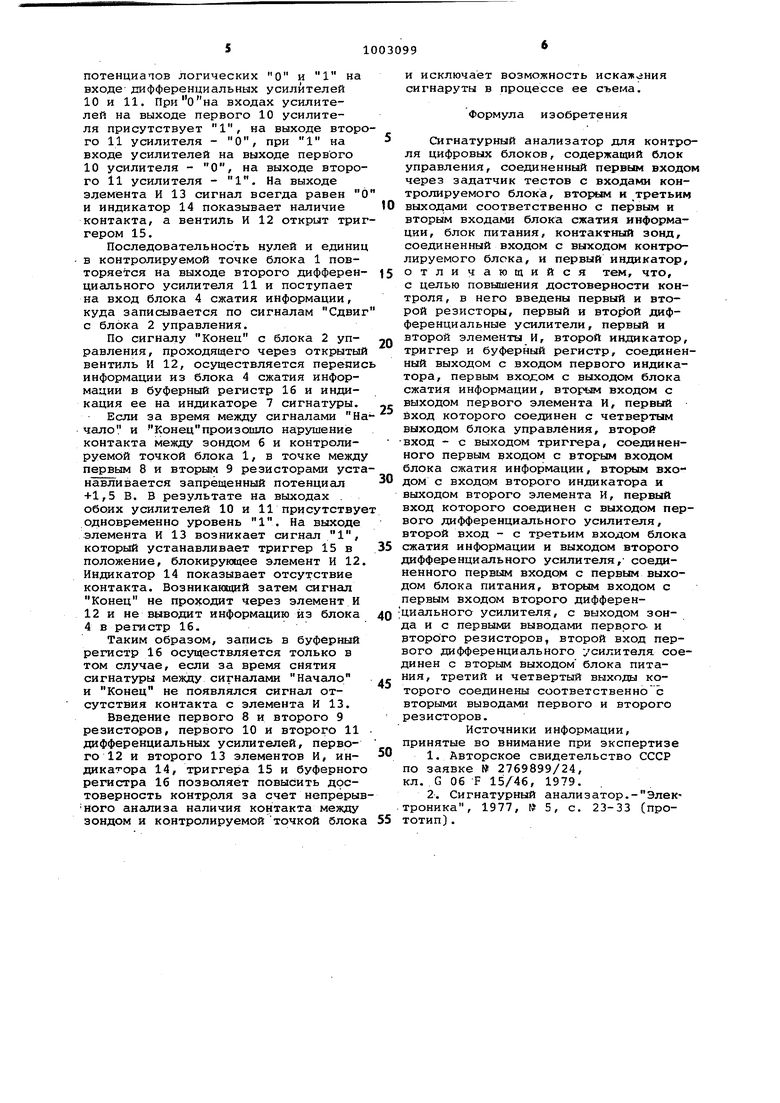

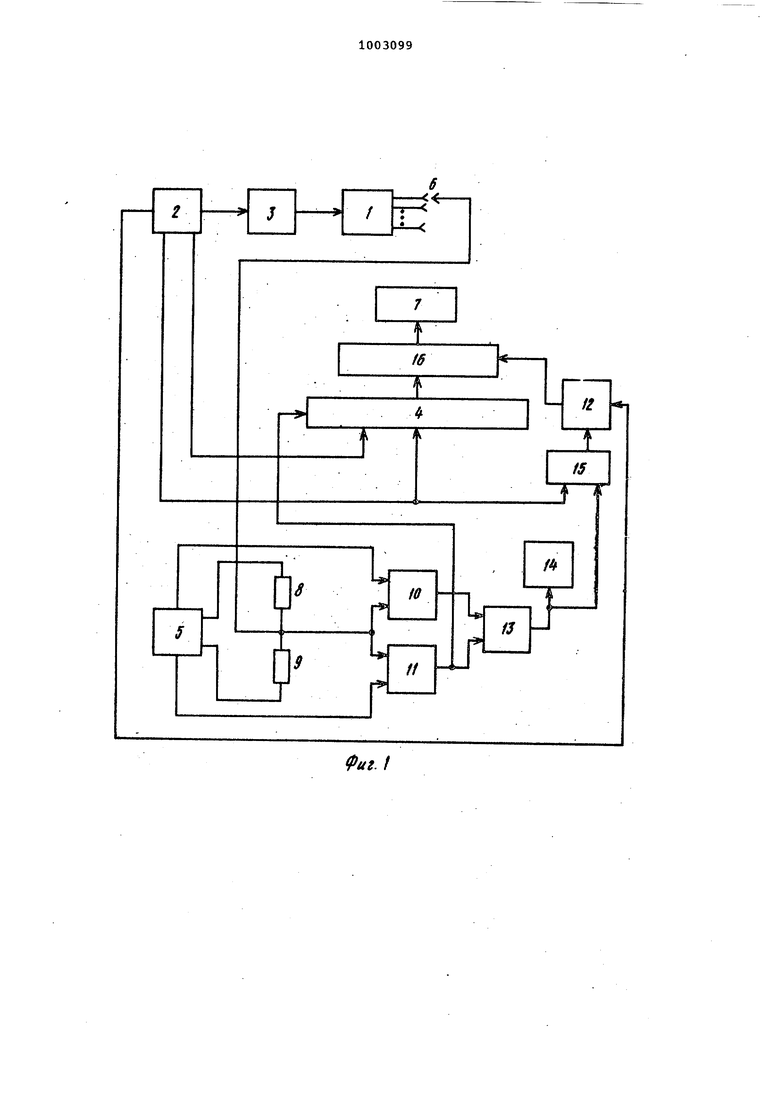

На фиг. 1 приведена блок-схема сигнатурного анализатора для контроля цифровых блоков на фиг.. 2 - блоксхема сжатия информации.; на фиг. 3 пример реализации блока управления.

Сигнатурный анализатор для контроля цифровых блоков 1 содержит бло 2 управления, задатчик тестов 3, бло 4 сжатия информации, блок 5 питания, контактный зонд 6, первый индикатор 7, первый 8 и второй 9 резисторы, первый 10 и второй 11 дифференциальные усилители, первый 12 и второй 13 элементы н, второй индикатор 14, триггер 15 и буферный регистр 16.

Блок 4 сжатия информации представ ляет собой сдвигающий регистр 17, охваченный кольцом обратной связи через элемент 18 сложения по модулю два.

Блок 2 управления, состоящий из генератора 19, элемента И 20, триггера 21, счетчика 22, дешифратора 23/ элемента ИЛИ 24, кнопок 25 и 26, синхронизирует работу всего устройства, вырабатывая сигналы Начало, Сдвиг, Конец и Адрес.

Задат чик тестов 3, представляющий собой блок постоянной памяти, по адресу, задаваемому блоком 2 управления, выдает на контролируемый.блок 1 последовательность контрольных тестов .

Контактный зонд 6 осуществляет подключение контрольных точек цифрового блока 1 через второй дифференциальный усилитель 11 к входу блока 4 сжатия информации.

Триггер 15 и элемент И 12 вырабатывают сигнал вывода сигнатуры из блока 4 сжатия информации в буферный

регистр 16, состояния которого индицруются на индикаторе 7.

Первый 8 и второй 9 резисторы, подключенные соответственно к выводам Корпус и +5 В блока 5 питания, выбраны таким образом, что в их общей точке возникает запрещенный потенциал около +1,5 В в случае, если отсутствует контакт между зондом 6 и контрольной точкой блока 1. В случае наличия контакта в общей точке резисторов 8 и 9 присутствуют сигналы логического О ( 0,4 В или логической 1 (7/2,4 В).

Первый 10 и второй 11 дифференциальные усилители и второй элемент И 13 осущес твляют измерение потенциала в контрольной точке, которая подключается через зонд 6 на первый (отрицательный ) вход первого 10 дифференциального усилителя к второй f положительный ) вход второго 11 диф ференциального усилителя. На второй (положительный) вход первого 10 дифференциального усилителя подается с блока 5 питания верхнее опорное напряжение +2,4 В, а на первый (отрицательный ).вход второго 11 дифференциального усилителя подается нижнее опорное напряжение +0,4 В с блока 5 питания.

Индикатор 14 фиксирует на своем табло о.тсутствие контакта.

Устройство работаетследующим образом.

По нажатию кнопки 25 триггер 21 блока управления 2 устанавливается в положение, которое бло1 ирует поступление импульсов с генератора 19 чере элемент И 20 на счетчик 22, который устанавливается в исходное состояние. По нажатию кнопки 26 Пуск триггер 21 открывает элемент 20 И и импульсы с генератора 19 поступают на счетчик 22. Дешифратором 23 вырабатываются командные импульсы Начало и Конец, а между ними элемент ИЛИ 24 вырабатывает серию импульсов сдвига, поступающих на блок 4 сжатия информации. Счетчик .22 вырабатывает адрес, .поступающий на задатчик тестов 3.

По сигналу Начало блока 2 управления блок 4 информации сбрасывается в исходное состояние,а триггер 15 устанавливается в положение, открывающее вентиль И 12. Задатчик тестов 3 в соответствии с адресами из блока управления 2 на контролируемый блок 1 последовательно один элементарный тест за другим. Последовательность логических сигналов ( О 0,4 В и 1 2,4.в; через зонд б поступает на входы дифференциальных усилителей 10 и 11. При наличии контакта между зондом 6 и контролируемой точкой блока 1 первый 8 и второй 9 резисторы не меняют

потенциапов логических О и 1 на входе дифференциальных усилителей 10 и 11, входах усилителей на выходе первого 10 усилителя присутствует 1, на выходе второго 11 усилителя - О, при 1 на входе усилителей на выходе первого 10 усилителя - О, на выходе второго 11 усилителя - 1, На выходе элемента И 13 сигнал всегда равен 6 и индикатор 14 показывает наличие контакта, а вентиль И 12 открыт триггером 15.

Последовательность нулей и единиц в контролируемой точке блока 1 повторяется на выходе второго дифференциального усилителя 11 и поступает на вход блока 4 сжатия информации, куда записывается по сигналам Сдвиг с блока 2 управления.

По сигналу Конец с блока 2 управления, проходящего через открытый вентиль И 12, осуществляется перепис информации из блока 4 сжатия информации в буферный регистр 16 и индикация ее на индикаторе 7 сигнатуры. Если за время между сигналами Начало и Конец произошло нарушение контакта между зондом б и контролируемой точкой блока 1, в точке между первым 8 и вторым 9 резисторами устанавливается запрещенный потенциал +1,5 В. В результате на выходах . обоих усилителей 10 и 11 присутствуе одновременно уровень 1. На выходе элемента И 13 возникает сигнал 1, который устанавливает триггер 15 в положение, блокирующее элемент И 12. Индикатор 14 показывает отсутствие контакта. Возникающий затем сигнал Конец не проходит через элемент И 12 и не ВЦВОДИТ информацию из блока 4 в регистр 16.

Таким образом, запись в буферный регистр 16 осуществляется только в том случае, если за время снятия сигнатуры между сигналами Начало и Конец не появлялся сигнал отсутствия контакта с элемента И 13.

Введение первого 8 и второго 9 резисторов, первого 10 и второго 11 дифференциальных усилителей, первого 12 и второго 13 элементов И, индикатора 14, триггера 15 и буферного регистра 16 позволяет повысить достоверность контроля за счет непрерывного анализа наличия контакта между зондом и контролируемой точкой блока

и исключает возможность искаж«зния сигнаруты в процессе ее съема.

Формула изобретения

Сигнатурный анализатор для контроля цифровых блоков, содержащий блок управления, соединенный первым входо через задатчик тестов с входами контролируемого блока, вторым и третьим выходами соответственно с первым и вторым входами блока сжатия информации, блок питания, контактный зонд, соединенный входом с выходом контролируемого блока, и первый индикатор отличающийся тем, что, с целью повышения достоверности контроля , в него введены первый и второй резисторы, первый и второй дифференциальные усилители, первый и второй элементы И, второй индикатор триггер и буферный регистр, соединенный выходом с входом первого индикатора, первым входном с выходом блока сжатия информации, вторым входом с выходом первого элемента И, первый вход которого соединен с четвертым выходом блока управления, второй вход - с выходом триггера, соединенного первым входом с вторым входом блока сжатия информации, вторым входом с входом второго индикатора и выходом второго элемента И, первый вход которого соединен с выходом первого дифференциального усилителя, второй вход - с третьим входом блока сжатия информации и выходом второго дифференциального усилителя,- соединенного первым входом с первым выходом блока питания, вторым входом с первым входом второго дифференциального усилителя, с выходом зонда и с первыми выводами первого, и второго резисторов, второй вход первого дифференциального усилителя соединен с вторым выходом блока питания, третий и четвертый выходы которого соединены соответственно с вторыми выводами первого и второго резисторов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР по заявке № 2769899/24,

кл. G 06 F 15/46, 1979.

2.Сигнатурный анализатор.- Элек троника, 1977, № 5, с. 23-33 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1267422A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1070562A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

Авторы

Даты

1983-03-07—Публикация

1981-09-02—Подача