Изобретение относится к контрольно-измерительной технике и может быт использовано для контроля и диагностики неисправностей в многоканальной цифровой аппаратуре.

Цель изобретения - увеличение производительности контроля за счет уменьшения количества циклоз сравнения сигнатуры проверяемого узла, оп- ределяющей его работоспособность, и контрольной сигнатуры.

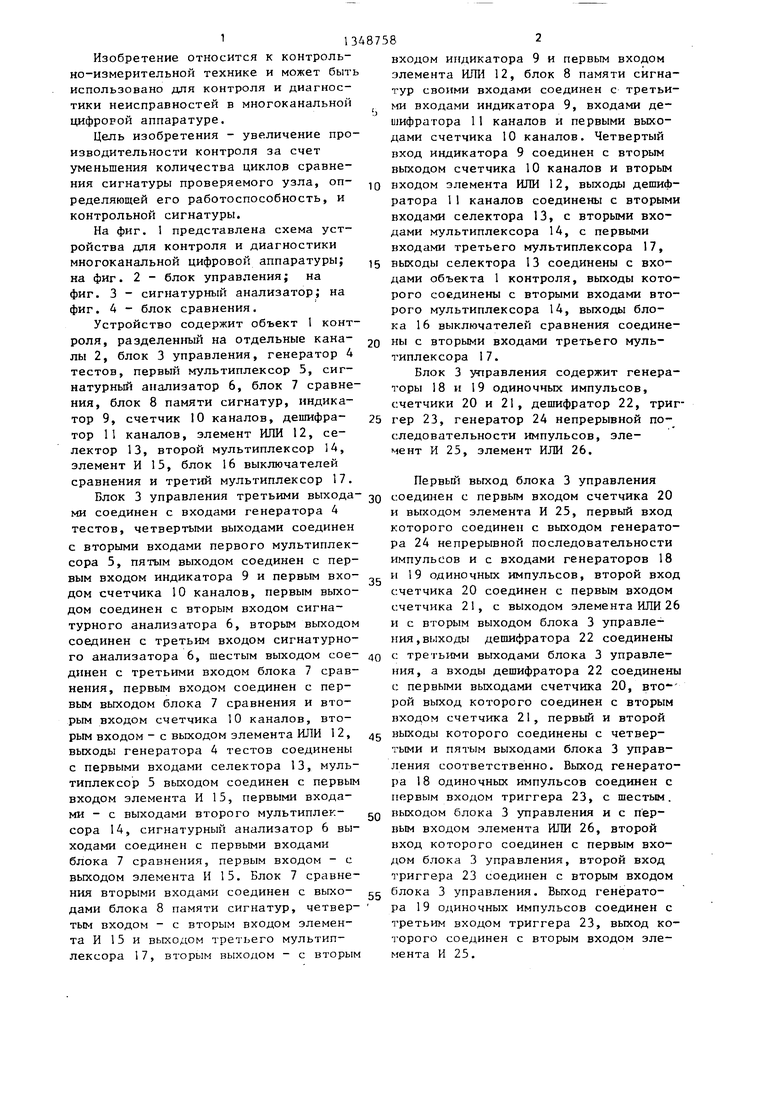

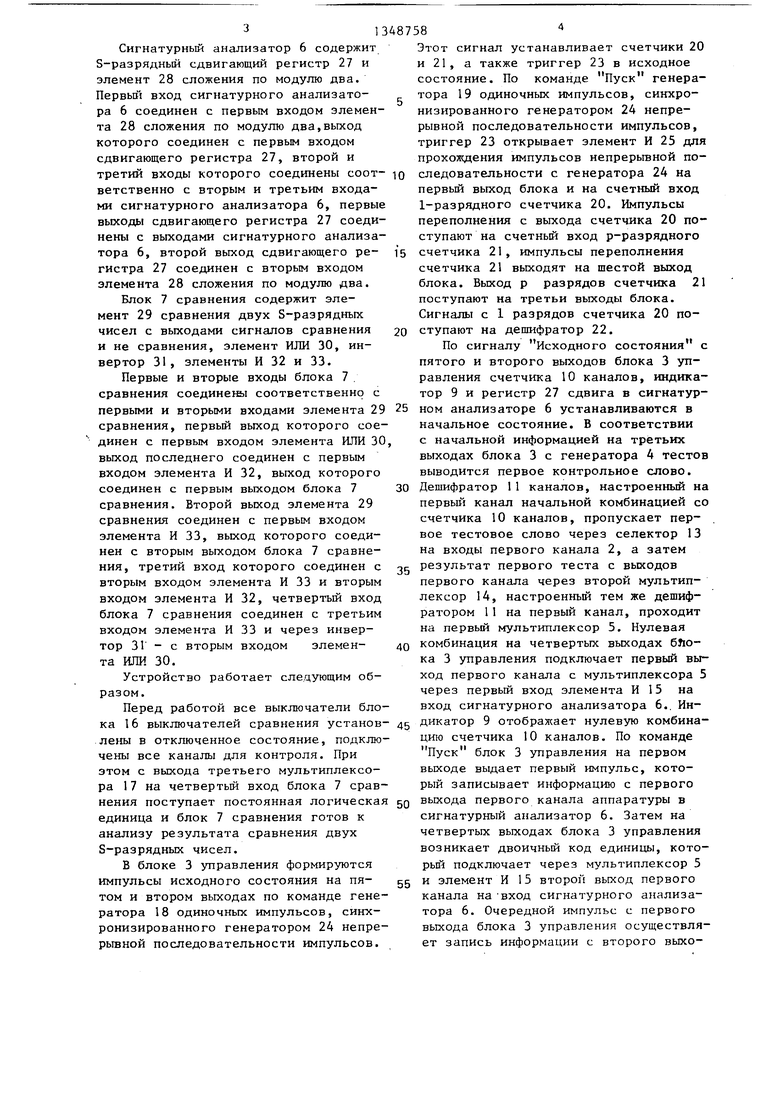

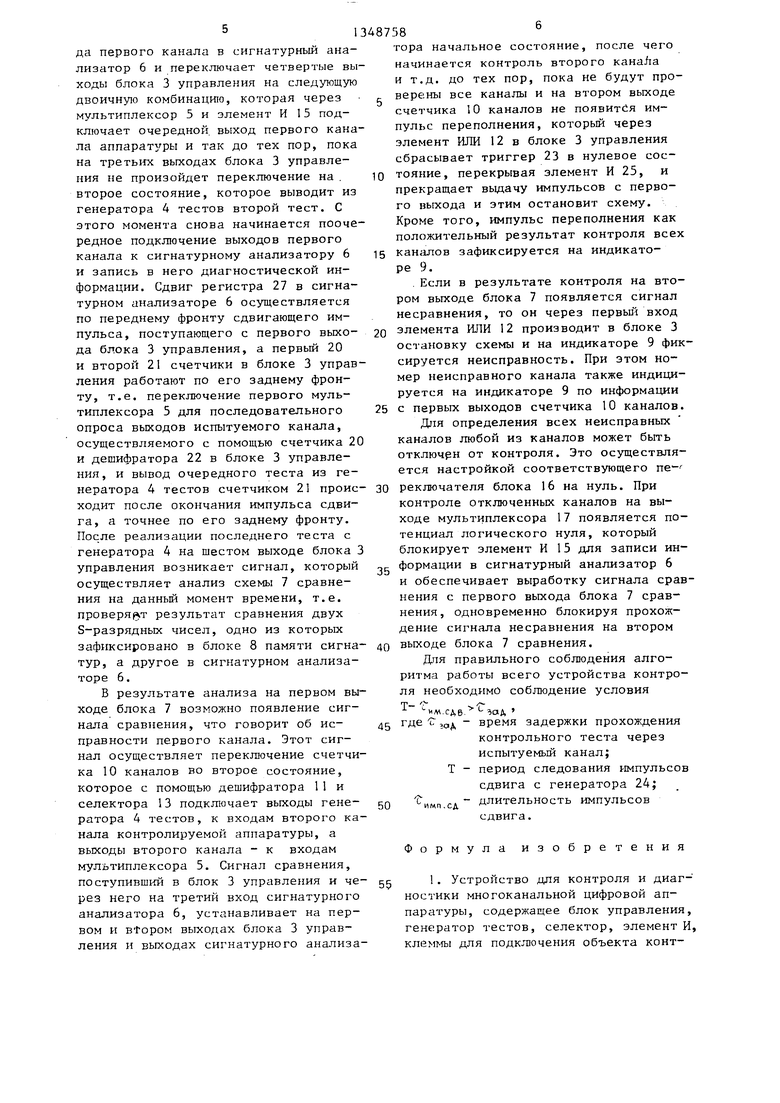

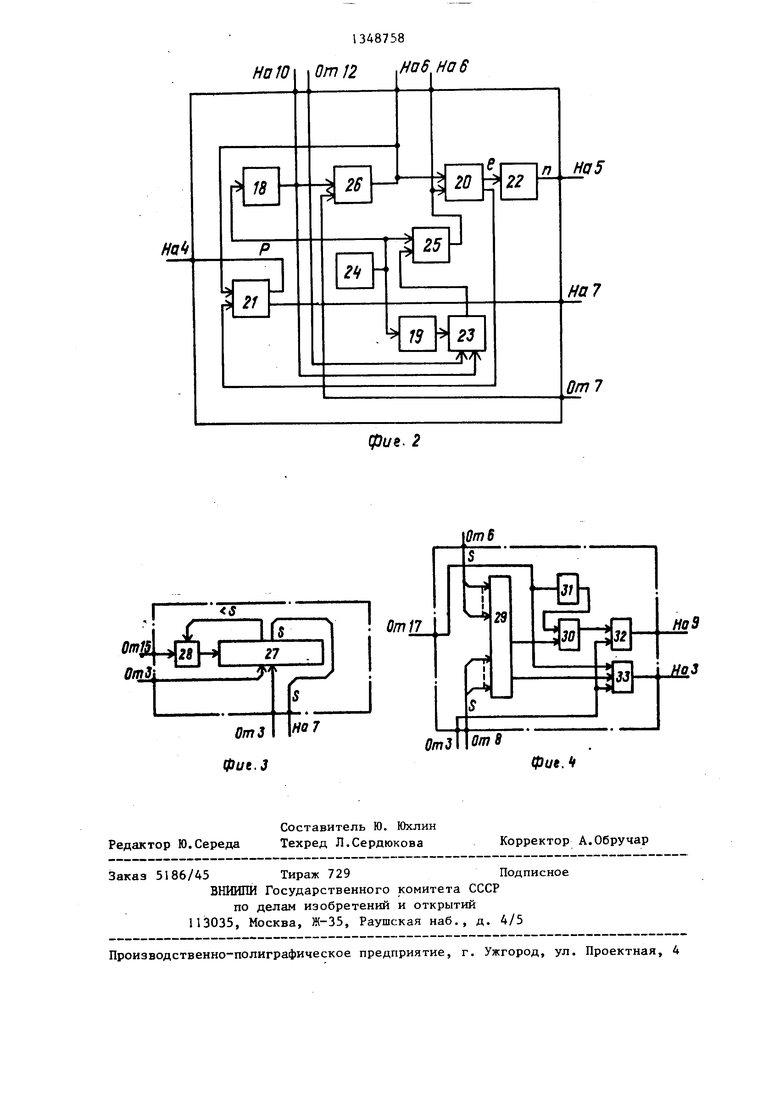

На фиг. 1 представлена схема устройства для контроля и диагностики многоканальной цифровой аппаратуры; на фиг. 2 - блок управления; на фиг. 3 - сигнатурный анализатор; на фиг. А - блок сравнения.

Устройство содержит объект 1 контроля, разделенный на отдельные кана- лы 2, блок 3 управления, генератор 4 тестов, первый мультиплексор 5, сигнатурный анализатор 6, блок 7 сравнения, блок 8 памяти сигнатур, индикатор 9, счетчик 10 каналов, дешифра- тор 11 каналов, элемент ИЛИ 12, селектор 13, второй мультиплексор 14, элемент И 15, блок 16 выключателей сравнения и третий мультиплексор 17.

Блок 3 управления третьими выхода ми соединен с входами генератора 4 тестов, четвертыми выходами соединен с вторыми входами первого мультиплексора 5, пятым выходом соединен с первым входом индикатора 9 и первым вхо- дом счетчика 10 каналов, первым выходом соединен с вторым входом сигнатурного анализатора 6, вторым выходом соединен с третьим входом сигнатурного анализатора 6, шестым выходом сое- динен с третьими входом блока 7 сравнения, первым входом соединен с первым выходом блока 7 сравнения и вторым входом счетчика 10 каналов, вторым входом - с выходом элемента ИЛИ 12, выходы генератора 4 тестов соединены с первыми входами селектора 13, мультиплексор 5 выходом соединен с первым входом элемента И 15, первыми входами - с выходами второго мультиплек- сора 14, сигнатурный анализатор 6 выходами соединен с первыми входами блока 7 сравнения, первым входом - с выходом элемента И 15. Блок 7 сравнения вторыми входами соединен с выхо- дами блока 8 памяти сигнатур, четвер- тым входом - с вторым входом элемента И 15 и выходом третьего мультиплексора 17, вторым выходом - с вторым

входом индикатора 9 и первым входом элемента ИЛИ 12, блок 8 памяти сигнатур своими входами соединен с третьими входами индикатора 9, входами дешифратора 11 каналов и первыми выходами счетчика 10 каналов. Четвертый вход индикатора 9 соединен с вторым выходом счетчика 10 каналов и вторым входом элемента ИЛИ 12, выходы дешифратора 11 каналов соединены с вторыми входами селектора 13, с вторыми входами мультиплексора 14, с первыми входами третьего мультиплексора 17, выходы селектора 13 соединены с входами объекта 1 контроля, вькоды которого соединены с вторыми входами второго мультиплексора 14, выходы бло- fca 16 выключателей сравнения соединены с вторыми входами третьего мультиплексора 17.

Блок 3 управления содержит генераторы 18 и 19 одиночных импульсов, счетчики 20 и 21, дешифратор 22, триггер 23, генератор 24 непрерывной последовательности импульсов, элемент И 25, элемент ИЛИ 26.

Первьв выход блока 3 управления соединен с первым входом счетчика 20 и выходом элемента И 25, первый вход которого соединен с выходом генератора 24 непрерывной последовательности импульсов и с входами генераторов 18 и 19 одиночных импульсов, второй вход счетчика 20 соединен с первым входом счетчика 21, с выходом элемента ИЛИ 26 и с вторым выходом блока 3 управления, выходы дешифратора 22 соединены с третьими выходами блока 3 управления, а входы дешифратора 22 соединены с первыми выходами счетчика 20, вто- рой выход которого соединен с вторым входом счетчика 21, первый и второй выходы которого соединены с четвертыми и пятым выходами блока 3 управления соответственно. Выход генератора 18 одиночных импульсов соединен с первым входом триггера 23, с шестым, выходом блока 3 управления и с первым входом элемента ИЛИ 26, второй вход которого соединен с первым входом блока 3 управления, второй вход триггера 23 соединен с вторым входом блока 3 управления. Выход генератора 19 одиночных Импульсов соединен с третьим входом триггера 23, выход которого соединен с вторым входом элемента И 25.

Сигнатурный анализатор 6 содержит S-разрядный сдвигающий регистр 27 и элемент 28 сложения по модулю два. Первьш вход сигнатурного анализатора 6 соединен с первым входом элемента 28 сложения по модулю два,выход которого соединен с первым входом сдвигающего регистра 27, второй и третий входы которого соединены соот- ветственно с вторым и третьим входами сигнатурного анализатора 6, первые выходы сдвигающего регистра 27 соединены с выходами сигнатурного анализатора 6, второй выход сдвигающего ре- гистра 27 соединен с вторым входом элемента 28 сложения по модулю два.

Блок 7 сравнения содержит элемент 29 сравнения двух S-разрядных чисел с выходами сигналов сравнения и не сравнения, элемент ИЛИ 30, инвертор 31, элементы И 32 и 33.

Первые и вторые входы блока 7 . сравнения соединены соответственно с первыми и вторыми входами элемента 29 сравнения, первый выход которого соединен с первым входом элемента ИЛИ 30 выход последнего соединен с первым входом элемента И 32, выход которого соединен с первым выходом блока 7 сравнения. Второй выход элемента 29 сравнения соединен с первым входом элемента И 33, выход которого соединен с вторым выходом блока 7 сравнения, третий вход которого соединен с вторым входом элемента И 33 и вторым входом элемента И 32, четвертый вход блока 7 сравнения соединен с третьим входом элемента И 33 и через инвертор 31 - с вторым входом элемен- та ИЛИ 30.

Устройство работает следующим образом.

Перед работой все выключатели блока 16 выключателей сравнения установ лены в отключенное состояние, подключены все каналы для контроля. При этом с выхода третьего мультиплексора 17 на четвертьй вход блока 7 сравнения поступает постоянная логическая единица и блок 7 сравнения готов к анализу результата сравнения двух S-разрядных чисел.

В блоке 3 управления формируются импульсы исходного состояния на пя- том и втором выходах по команде генератора 18 одиночных импульсов, синхронизированного генератором 24 непре- рьшной последовательности импульсов.

Этот сигнал устанавливает счетчики 20 и 21, а также триггер 23 в исходное состояние. По команде Пуск генератора 19 одиночных импульсов, синхронизированного генератором 24 непрерывной последовательности импульсов, триггер 23 открывает элемент И 25 для прохождения импульсов непрерьгеной последовательности с генератора 24 на первый выход блока и на счетный вход 1-разрядного счетчика 20. Импульсы переполнения с выхода счетчика 20 поступают на счетный вход р-разрядного счетчика 21, импульсы переполнения счетчика 21 выходят на шестой выход блока. Выход р разрядов счетчика 21 поступают на третьи выходы блока. Сигналы с 1 разрядов счетчика 20 поступают на дешифратор 22.

По сигналу Исходного состояния с пятого и второго выходов блока 3 управления счетчика 10 каналов, индикатор 9 и регистр 27 сдвига в сигнатурном анализаторе 6 устанавливаются в начальное состояние. В соответствии с начальной информацией на третьих выходах блока 3 с генератора 4 тестов выводится первое контрольное слово. Дешифратор 11 каналов, настроенный на первый канал начальной комбинацией со счетчика 10 каналов, пропускает первое тестовое слово через селектор 13 на входы первого канала 2, а затем результат первого теста с выходов первого канала через второй мультиплексор 14, настроенный тем же дешифратором 11 на первый канал, проходит на первый мультиплексор 5. Нулевая комбинация на четвертых вьгходах бйо- ка 3 управления подключает первый выход первого канала с мультиплексора 5 через первый вход элемента И 15 на вход сигнатурного анализатора 6.. Индикатор 9 отображает нулевую комбинацию счетчика 10 каналов. По команде Пуск блок 3 управления на первом выходе выдает первый импульс, который записывает информацию с первого выхода первого канала аппаратуры в сигнатурный анализатор 6. Затем на четвертых выходах блока 3 управления возникает двоичный код единицы, кото- рьш подключает через мультиплексор 5 и элемент И 15 второй выход первого канала на вход сигнатурного анализатора 6. Очередной импульс с первого выхода блока 3 управления осуществляет запись информации с второго выхода первого канала в сигнатурный анализатор 6 и переключает четвертые выходы блока 3 управления на следующую двоичную комбинацию, которая через мультиплексор 5 и элемент И 15 подключает Очередной выход первого канала аппаратуры и так до тех пор, пока на третьих выходах блока 3 управления не произойдет переключение на. второе состояние, которое выводит из генератора 4 тестов второй тест. С этого момента снова начинается поочередное подключение выходов первого канала к сигнатурному анализатору 6 и запись в него диагностической информации. Сдвиг регистра 27 в сигнатурном анализаторе 6 осуществляется по переднему фронту сдвигающего импульса, поступающего с первого выхода блока 3 управления, а первый 20 и второй 21 счетчики в блоке 3 управления работают по его заднему фронту, т.е. переключение первого мультиплексора 5 для последовательного опроса выходов испытуемого канала, осуществляемого с помощью счетчика 20 и дешифратора 22 в блоке 3 управления, и вывод очередного теста из генератора 4 тестов счетчиком 21 происходит после окончания импульса сдвига, а точнее по его заднему фронту. После реализации последнего теста с генератора 4 на шестом выходе блока 3 управления возникает сигнал, который осуществляет анализ схемы 7 сравнения на данный момент времени, т.е. проверяр.т результат сравнения двух S-разрядных чисел, одно из которых зафиксировано в блоке 8 памяти сигнатур, а другое в сигнатурном анализаторе 6.

В результате анализа на первом выходе блока 7 возможно появление сигнала сравнения, что говорит об исправности первого канала. Этот сигнал осуществляет переключение счетчика 10 каналов во второе состояние, которое с помощью дешифратора 1I и селектора 13 подключает выходы генератора 4 тестов, к входам второго канала контролируемой аппаратуры, а выходы второго канала - к входам мультиплексора 5. Сигнал сравнения, поступивший в блок 3 управления и через него на третий вход сигнатурного анализатора 6, устанавливает на первом и BtopoM выходах блока 3 управления и выходах сигнатурного анализатора начальное состояние, после чего начинается контроль второго канаЛа и т.д. до тех пор, пока не будут проверены все каналы и на втором выходе счетчика 10 каналов не появится импульс переполнения, который через элемент ИЛИ 12 в блоке 3 управления сбрасывает триггер 23 в нулевое состояние, перекрывая элемент И 25, и прекращает выдачу импульсов с первого выхода и этим остановит схему. Кроме того, импульс переполнения как положительный результат контроля всех

кан«1лов зафиксируется на индикаторе 9.

. Если в результате контроля на втором выходе блока 7 появляется сигнал несравнения, то он через первьш вход

элемента ИЛИ 12 производит в блоке 3 остановку схемы и на индикаторе 9 фиксируется неисправность. При этом номер неисправного канала также индицируется на индикаторе 9 по информации

с первых выходов счетчика 10 каналов.

Для определения всех неисправных каналов любой из каналов может быть отключен от контроля. Это осуществляется настройкой соответствующего пе

реключателя блока 16 иа нуль. При контроле отключенных каналов на выходе мультиплексора 17 появляется потенциал логического нуля, который блокирует элемент И 15 для записи информации в сигнатурный анализатор 6 и обеспечивает выработку сигнала сравнения с первого выхода блока 7 сравнения, одновременно блокируя прохождение сигнала несравнения на втором

выходе блока 7 сравнения.

Для правильного соблюдения алгоритма работы всего устройства контроля необходимо соблюдение условия

чм.сАб.

где - ад время задержки прохождения контрольного теста через испытуемый канал; Т - период следования импульсов сдвига с генератора 24; длительность импульсов сдвига.

имп .сд

Формула изобретения

1. Устройство для контроля и диаг- ностики многоканальной цифровой аппаратуры, содержащее блок управления, генератор тестов, селектор, элемент И, клеммы для подключения объекта контроля, индикатор, сигнатурньй анализатор, выходы которого соединены с первыми входами блока сравнения, блок памяти сигнатур, выходы которого соединены с вторыми входами блока сравнения, отличающееся тем что, с целью увеличения производительности контроля, в него введены счетчик каналов, дешифратор каналов, элемент ИЛИ, первый, второй и третий мультиплексоры, блок вьжлючателей сравнения, причем выходы генератора тестов соединены с первыми входами селектора, выходы которого соединены с клеммами для подключения входов объекта контроля, клеммы для подключения выходов объекта контроля соединены с первыми входами второго мультиплексора, выходы которого соединены с первыми входами первого мультиплексора, выход которого соединен с первым входом элемента И, выход которого соединен с первым входом сигнатурного анализатора, второй и третий входы которого соединены соответственно с первым и вторым выходами блока управления, третьи выходы блока управления соединены с входами генератора тестов, четвертые выходы соединены с вторыми входами первого мультиплексора, пятый выход соединен с первым входом индикатора и первым входом счетчика каналов, шестой выход соединен с третьим входом блока сравнения, первый выход которого соединен с первым входом блока управления и вторым входом счетчика каналов второй выход блока сравнения соединен с вторым входом индикатора и первым входом элемента ИЛИ, выход которого соединен с вторым входом блока управления, первые выходы счетчика каналов соединены с входами дешифратора каналов, с третьими входами индикатора и с входами блока памяти сигнатур, второй выход счетчика каналов соединен с вторым входом элемента ИЛИ и четвертым входом индика

тора, выходы дешифратора каналов соединены с вторыми входами селектора, с вторыми входами второго мультиплексора и с первыми входами третьего мультиплексора, выход выключателя каналов соединен с вторым входом третьего мультиплексора, выход которого соединен с четвертым входом блока сравнения и вторым входом элемента И.

2. Устройство по п. 1 , о т J и чающееся тем, чтс- блок управления содержит первьй и л горой генераторы одиночных импульсов, первый и второй счетчики, дешифратор, триггер, генератор непрерьшной последовательности импульсов, элементы И и ИЛИ, причем выход генератора непрерывной последовательности импульсов соединен с входами первого и второго генераторов одиночных импульсов и первьм входом элемента И, выход которого соединен с первым входом первого счетчика и первым выходом блока управления, второй вход первого счетчика соединен с первым входом второго счетчика, с выходом элемента ИЛИ и с вторым выходом блока управления, выходы дешифратора соединены с третьими выходами блока управления, входы дешифратора соединены с первыми выходами первого счетчика, второй выход которого соединен с вторым входом второго счетчика, первые и второй выходы которого соединены с четвертыми и пятым выходами блока управления соответственно, выход второго генератора одиночных импульсов соединен с первым входом триггера, с шес1Ъ1м выходом блока управления и с первым входом элемента ИЛИ, второй вход которого соединен с первым входом блока управления, второй вход триггера соединен с вторым входом блока управления, выход первого генератора одиночных импульсов соединен с третьим входом триггера, выход которого соединен с вторым входом элемента И.

фие. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканальной цифровой аппаратуры | 1986 |

|

SU1397860A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля монтажа | 1984 |

|

SU1211672A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение позволяет увеличить производительность контроля. Устройство содержит блок 3 управления, генератор 4 тестов, сигнатурный анализатор 6, блок 7 сравнения, блок 8 памяти сигнатур, индикатор 9 и селектор 13. Введение счетчика 10 каналов, дешифратора 11 каналов, элемента ИЛИ 12, блока 16 выключателей сравнения и мультиплексоров 5, 14 и 17 уменьшает количество циклов сравнения сигнатуры проверяемого узла, опреде- ляюш;ей его работоспособность, и контрольной сигнатуры. В описании приведен пример реализации блока 3 управления. 1 з.п. ф-лы, 4 ил. С « (Л с 00 СП 00 дзие. 1

ОтП

ОтЗ

фие,3

Редактор Ю.Середа

Составитель Ю. Юхлин Техред Л.Сердюкова

Заказ 5186/45 Тираж 729Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Ф(/в.«

Корректор А.Обручар

| Устройство для контроля многовыходных цифровых узлов | 1980 |

|

SU928367A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-03-03—Подача