(Л

со оо оо

00

ел

00

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых блоков радиоэлектронной аппаратуры.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля ждущих мультивибраторов.

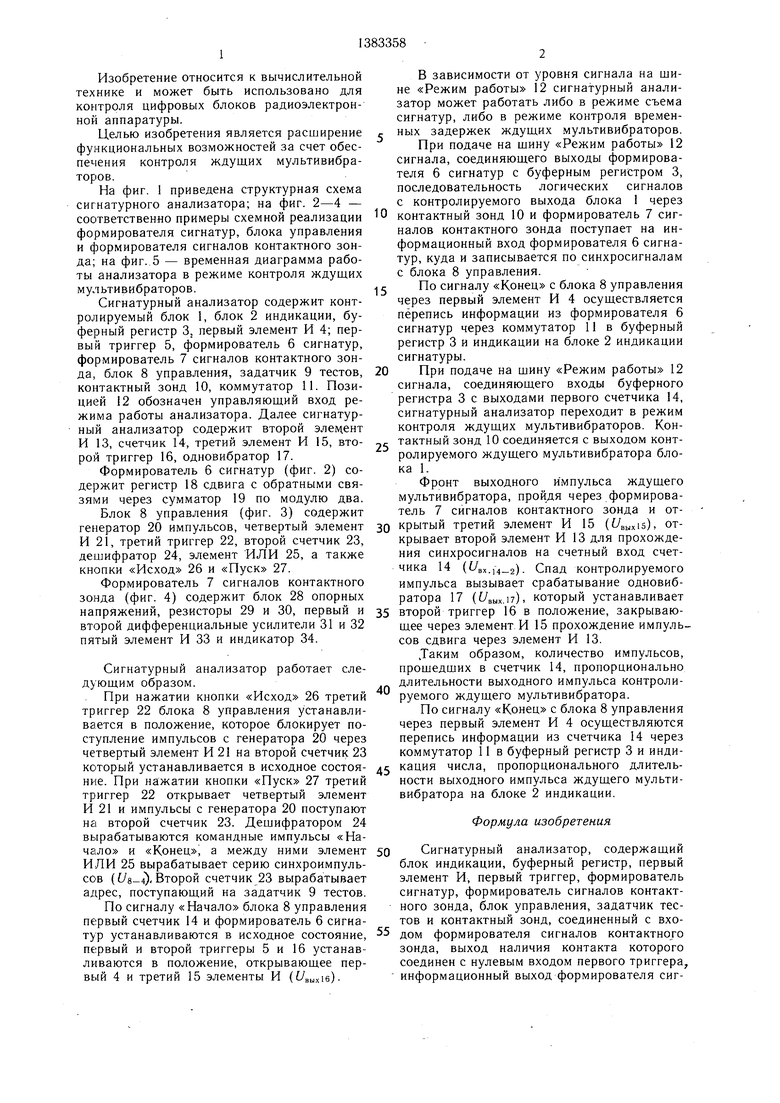

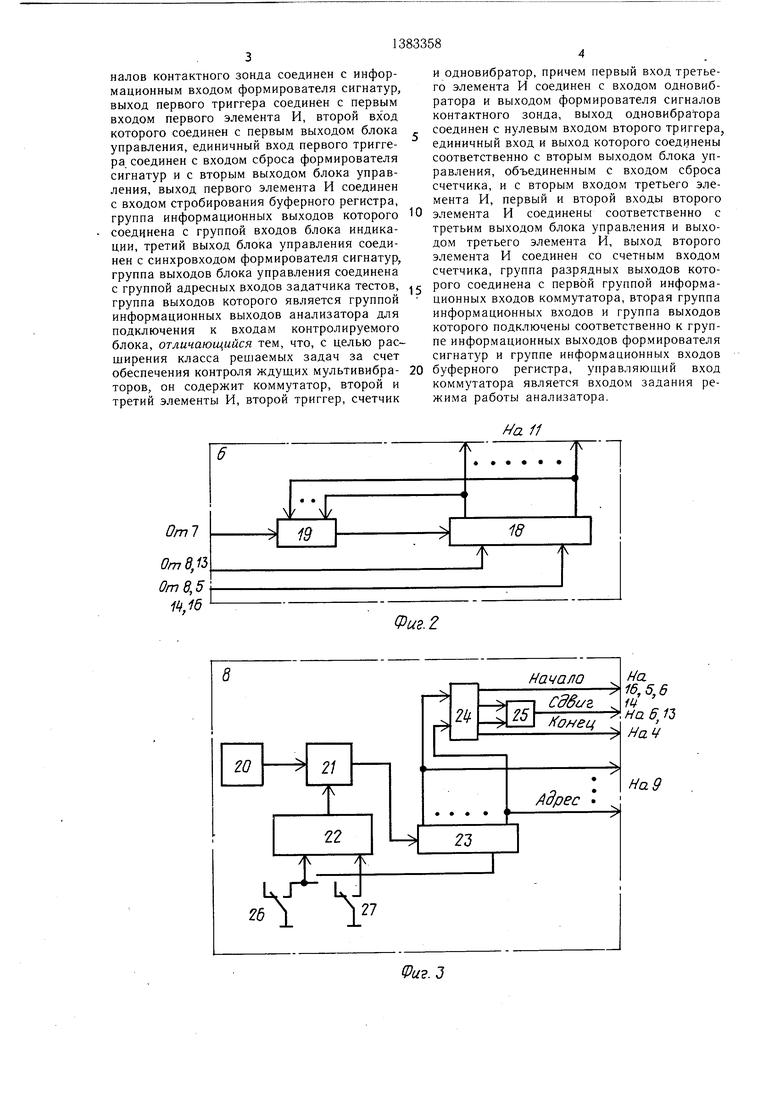

На фиг. 1 приведена структурная схема сигнатурного анализатора; на фиг. 2-4 - соответственно примеры схемной реализации формирователя сигнатур, блока управления и формирователя сигналов контактного зонда; на фиг. 5 - временная диаграмма работы анализатора в режиме контроля ждущих мультивибраторов.

Сигнатурный анализатор содержит контролируемый блок 1, блок 2 индикации, буферный регистр 3, первый элемент И 4; первый триггер 5, формирователь 6 сигнатур, формирователь 7 сигналов контактного зонда, блок 8 управления, задатчик 9 тестов, контактный зонд 10, коммутатор 11. Позицией 12 обозначен управляющий вход режима работы анализатора. Далее сигнатурный анализатор содержит второй элемент И 13, счетчик 14, третий элемент И 15, второй триггер 16, одновибратор 17.

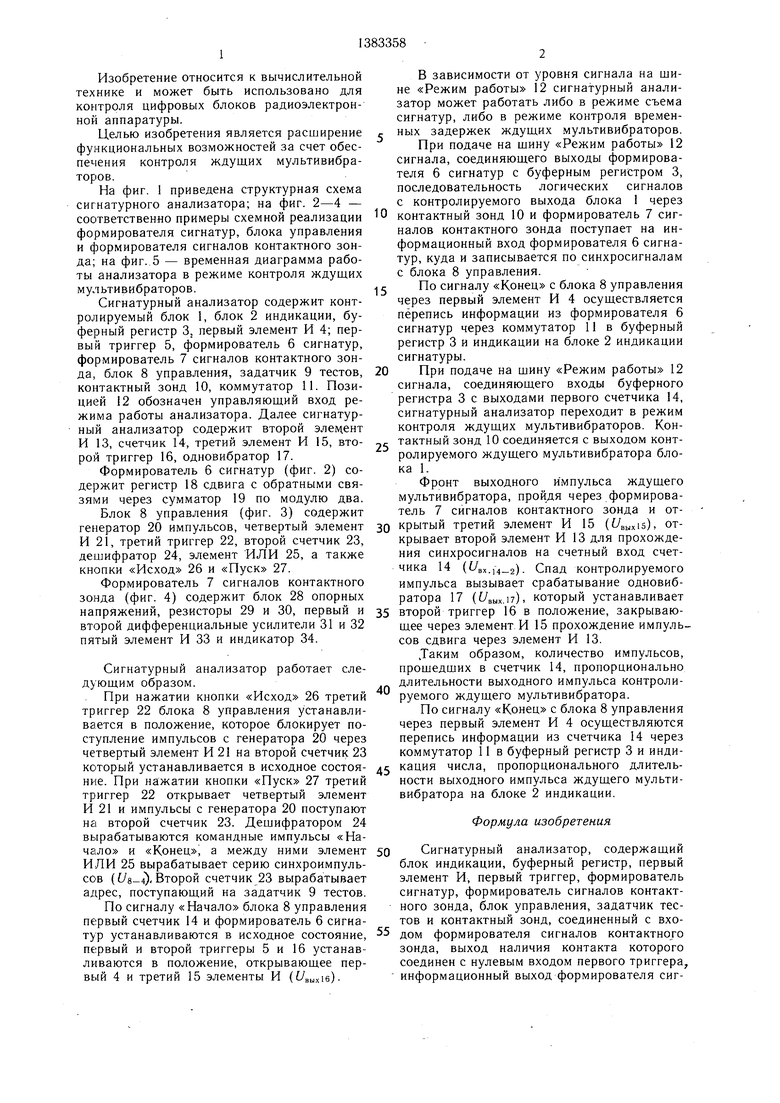

Формирователь 6 сигнатур (фиг. 2) содержит регистр 18 сдвига с обратными связями через сумматор 19 по модулю два.

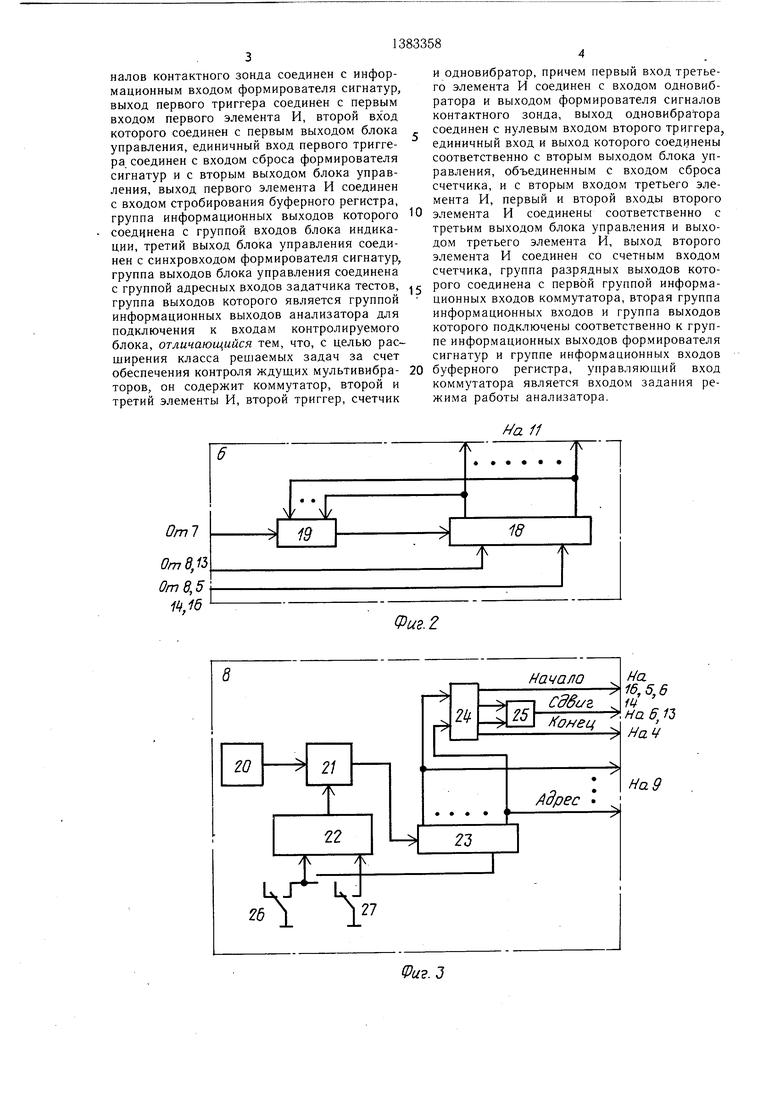

Блок 8 управления (фиг. 3) содержит генератор 20 импульсов, четвертый элемент И 21, третий триггер 22, второй счетчик 23, дешифратор 24, элемент ИЛИ 25, а также кнопки «Исход 26 и «Пуск 27.

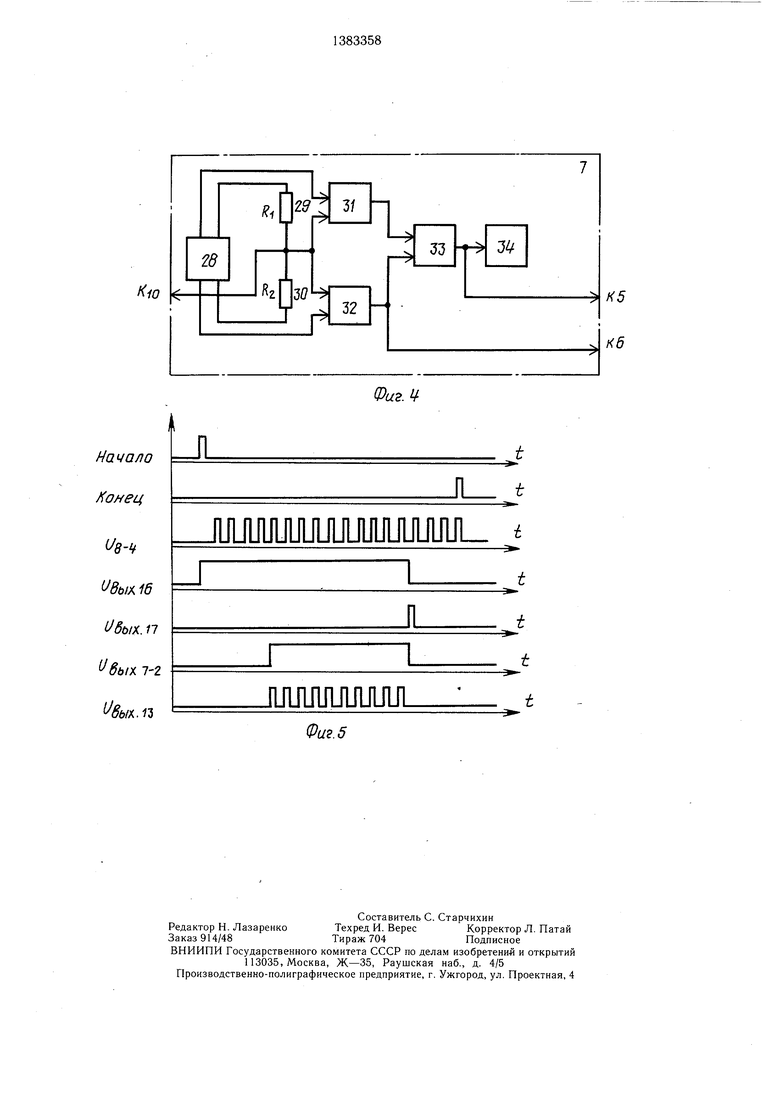

Формирователь 7 сигналов контактного зонда (фиг. 4) содержит блок 28 опорных напряжений, резисторы 29 и 30, первый и второй дифференциальные усилители 31 и 32 пятый элемент И 33 и индикатор 34.

Сигнатурный анализатор работает следующим образом.

При нажатии кнопки «Исход 26 третий триггер 22 блока 8 управления устанавливается в положение, которое блокирует поступление импульсов с генератора 20 через четвертый элемент И 21 на второй счетчик 23 который устанавливается в исходное состояние. При нажатии кнопки «Пуск 27 третий триггер 22 открывает четвертый элемент И 21 и импульсы с генератора 20 поступают на второй счетчик 23. Дешифратором 24 вырабатываются командные импульсы «Начало и «Конец, а между ними элемент ИЛИ 25 вырабатывает серию синхроимпульсов (б в-Д Второй счетчик 23 вырабатывает адрес, поступающий на задатчик 9 тестов.

По сигналу «Начало блока 8 управления первый счетчик 14 и формирователь 6 сигнатур устанавливаются в исходное состояние, первый и второй триггеры 5 и 16 устанавливаются в положение, открывающее пер- вь,й 4 и третий 15 элементы И ().

5

В зависимости от уровня сигнала на щи- не «Режим работы 12 сигнатурный анализатор может работать либо в режиме съема сигнатур, либо в режиме контроля временных задержек ждущих мультивибраторов. При подаче на щину «Режим работы 12 сигнала, соединяющего выходы формирователя 6 сигнатур с буферным регистром 3, последовательность логических сигналов с контролируемого выхода блока 1 через

0 контактный зонд 10 и формирователь 7 сигналов контактного зонда поступает на информационный вход формирователя 6 сигнатур, куда и записывается по синхросигналам с блока 8 управления.

5 По сигналу «Конец с блока 8 управления через первый элемент И 4 осуществляется перепись информации из формирователя 6 сигнатур через коммутатор 11 в буферный регистр 3 и индикации на блоке 2 индикации сигнатуры.

0 При подаче на шину «Режим работы 12 сигнала, соединяющего входы буферного регистра 3 с выходами первого счетчика 14, сигнатурный анализатор переходит в режим контроля ждущих мультивибраторов. Контактный зонд 10 соединяется с выходом контролируемого ждущего мультивибратора блока 1.

Фронт выходного и мпульса ждущего мультивибратора, пройдя через формирователь 7 сигналов контактного зонда и от0 крытый третий элемент И 15 (i/Buxis), открывает второй элемент И 13 для прохождения синхросигналов на счетный вход счетчика 14 (t/Bx.f4-2). Спад контролируемого импульса вызывает срабатывание одновиб- ратора 17 (.п), который устанавливает

5 второй триггер 16 в положение, закрывающее через элемент И 15 прохождение импульсов сдвига через элемент И 13.

.Таким образом, количество импульсов, прощедших в счетчик 14, пропорционально длительности выходного импульса контролируемого ждущего мультивибратора.

По сигналу «Конец с блока 8 управления через первый элемент И 4 осуществляются перепись информации из счетчика 14 через коммутатор 11 в буферный регистр 3 и инди5 кация числа, пропорционального длительности выходного импульса ждущего мультивибратора на блоке 2 индикации.

Формула изобретения

0 Сигнатурный анализатор, содержащий блок индикации, буферный регистр, первый элемент И, первый триггер, формирователь сигнатур, формирователь сигналов контактного зонда, блок управления, задатчик тестов и контактный зонд, соединенный с вхо5 дом формирователя сигналов контактного зонда, выход наличия контакта которого соединен с нулевым входом первого триггера, информационный выход формирователя сиг0

налов контактного зонда соединен с информационным входом формирователя сигнатур, выход первого триггера соединен с первым входом первого элемента И, второй вх од которого соединен с первым выходом блока управления, единичный вход первого триггера соединен с входом сброса формирователя сигнатур и с вторым выходом блока управления, выход первого элемента И соединен с входом стробирования буферного регистра, группа информационных выходов которого соединена с группой входов блока индикации, третий выход блока управления соединен с синхровходом формирователя сигнатур, группа выходов блока управления соединена с группой адресных входов задатчика тестов, группа выходов которого является группой информационных выходов анализатора для подключения к входам контролируемого блока, отличающийся тем, что, с целью расширения класса решаемых задач за счет обеспечения контроля ждущих мультивибра- торов, он содержит коммутатор, второй и третий элементы И, второй триггер, счетчик

j

10

20

15

и одновибратор, причем первый вход третьего элемента И соединен с входом одновиб- ратора и выходом формирователя сигналов контактного зонда, выход одновибратора соединен с нулевым входом второго триггера, единичный вход и выход которого соединены соответственно с вторым выходом блока управления, объединенным с входом сброса счетчика, и с вторым входом третьего элемента И, первый и второй входы второго элемента И соединены соответственно с третьим выходом блока управления и выходом третьего элемента И, выход второго элемента И соединен со счетным входом счетчика, группа разрядных выходов которого соединена с первой группой информационных входов коммутатора, вторая группа информационных входов и группа выходов которого подключены соответственно к группе информационных выходов формирователя сигнатур и группе информационных входов буферного регистра, управляющий вход коммутатора является входом задания режима работы анализатора.

//Д //

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1985 |

|

SU1267422A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Сигнатурный анализатор | 1985 |

|

SU1367016A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля цифровых блоков радиоэлектронной аппаратуры. Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля ждущих мультивибраторов. Сигнатурный анализатор содержит цепь формирования сигнатур и цепь измерения длительности импульсов ждущих мультивибраторов, содержащую элементы И 13 и 15, счетчик 14, триггер 16, одновибратор 17, коммутатор П. Анализатор работает в двух режимах: формирования сигнатур и измерения длительности импульсов, причем обеспечивается выделение первого импульса из последовательности. Результаты измерения в первом и втором режимах с помощью коммутатора 11 записываются в буферный регистр 3 и индицируются блоком 2 индикации. 5 ил.

Фиг. 2

(Ри.3

KiO

л1ииишииии1шиш1лл i

л.

А

п

JUlJinmiUlM

fe.J

Кб

А

t

| Патент Великобритании № 1547574, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1981 |

|

SU1003099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-01-02—Подача