2. Устройство по п. 1, о т л ичающееся тем, что блок управления содержит кнопку пуска, соединенную первым вьгеодом с общей шиной устройства, вторым выводом с первым установочным входом RS триггера, соединенного вторым установочным входом с вторым выходом блока и с выходом второго счетчика, третьим установочным входбм - с установочными входами счетного триггера, второго счетчика, с первым выходом блока и с первым выводом кнопки исходной установки, соединенной вторым

выводом с общей шиной устройсг а, выход РЭ-триггера соединен с первым входом второго элемента И, соединенного вторым входом с выходом генератора импульсов, вькодом - со счетным входом счетного триггера, соединенного первым вьрсодом с четвертым выходом блока, вторым выходом - со счетным входом второго счетчика и с третьим выходом блока, переключатель вывода контролируемого цифрового уз;ла, соединенный первыми вьшодами с общей шиной устройства, вторыми выводами - с пятыми выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля многоканальной цифровой аппаратуры | 1986 |

|

SU1397860A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1981 |

|

SU1003099A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1458841A1 |

| Устройство для контроля монтажа | 1984 |

|

SU1211672A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее мультиплексор, соединенньй информационным входами с клеммами для подключения выходов контролируемого цифрового блока,выходом - с информационные вх дом сигнатурного анализатора, задат чик тестов, соединенный выходами с клеммами для подключения входов контролируемого цифрового блока, и первый счетчик, отличающее с и тем, что, с целью повышения быстродействия устройства, в него введены блок управления, индикатор блок памяти сигнатур, триггер прайнпьности сигнатуры, генератор пачк -импульсов, первый элемент И, блок ИЗхО сравнения, причем первый выход блока управления соединен с установочными входами сигнатурного анализатора, первого счетчика и триггера правильности сигнатуры, второй выход блока управления соединен через генератор пачки импульсов с первым входом первого элемента И, соединенного вторьм входом с первым выходом триггера правильности сигнат уры, выходом со счетным входом первого счетчика и стробирующим входом блока сравнения, соединенного первыми входами через блок памяти сигнатур с выходами первого счетчика, выходом - с информационным входом триггера правиль ности сигнатуры, соединенного вторым выходом с первым входом индикатора, вторые входы которого соединены с вторьпчи входами блока сравнения и с выходами сигнатзфного анализатора, соединенного синхровходом с третьим выходом блока управления, соеди ненного четвертым и пятым выходами с управляющими входами задатчика тестов и мультиплексора соответствен но.

Изобретение относится к вычислительной технике и может быть испопьзовано для контроля логических блоков средств ЦВТ.

Известно устройство для контроля хщфровых блоков, содержащее задатчиктестов, блок управления, сигнатурньй анализатор и блок индикации Ij .

Недостатком известного устройства является низкая достоверность контроля. Так как в нем отсутствует возможность снятия диагностических сигнатур с вьтодов контролируемой схемы а получаемая общая сигнатура цифровой схемы несет информацию только о ее работоспособности и не указывает на место неисправности, если таковая имеется.

Наиболее близким по техническому решению к предлагаемому является устройство для контроля цифровых блоков, содержащее мультиплексор, соединенный информационными входами с клеммами для подключения выходов контролируемого цифрового блока, выходом информационным входом сигнатурного анализатора,, задатчик тестов, соединенный выходами с клеммами для подключения входов контролируемого цифрового блока, первьй и второй счетчики, второй мультиплексор, дешифратор, блок злементов задержки, блок питания 2 .

Недостатком известного устройства является низкое быстродействие в режиме контроля цифровых блоков вследствие необходимости визуального сравнения многоцифровьк сигнатур, полученных на выходах контролируемого блока, с эталонными сигнатураМИл записанными в технической документации на блок.

Цель изобретения повьш1ение быстродействия устройства.

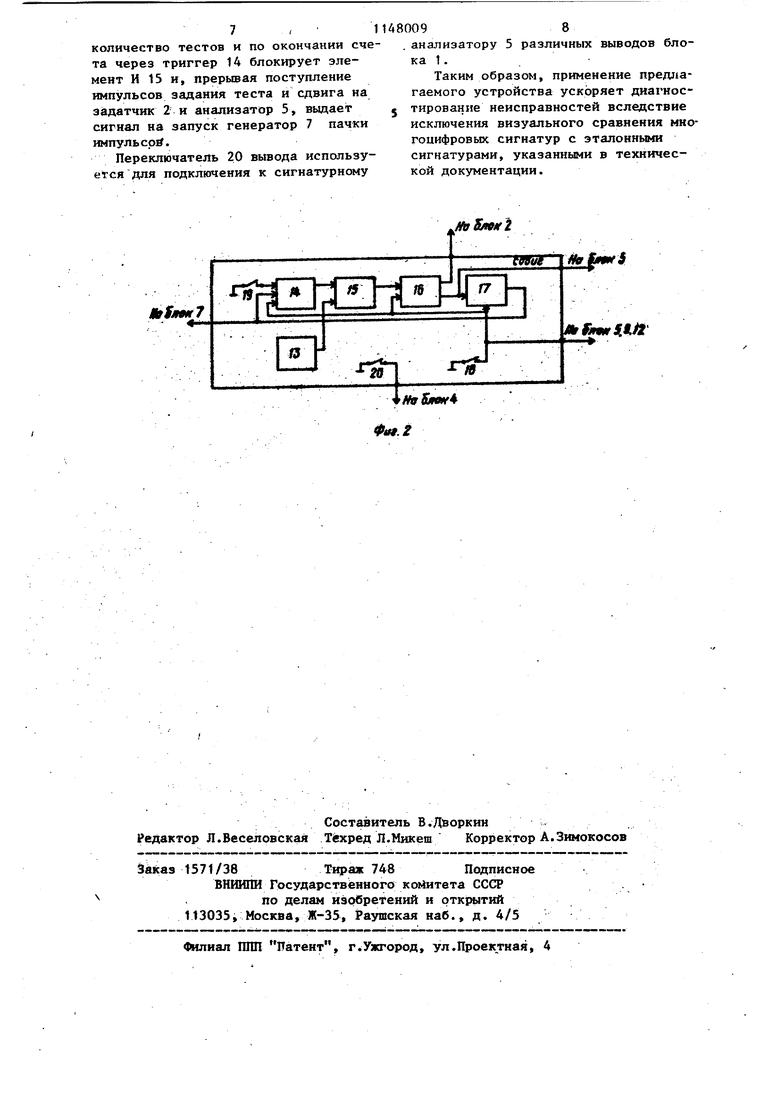

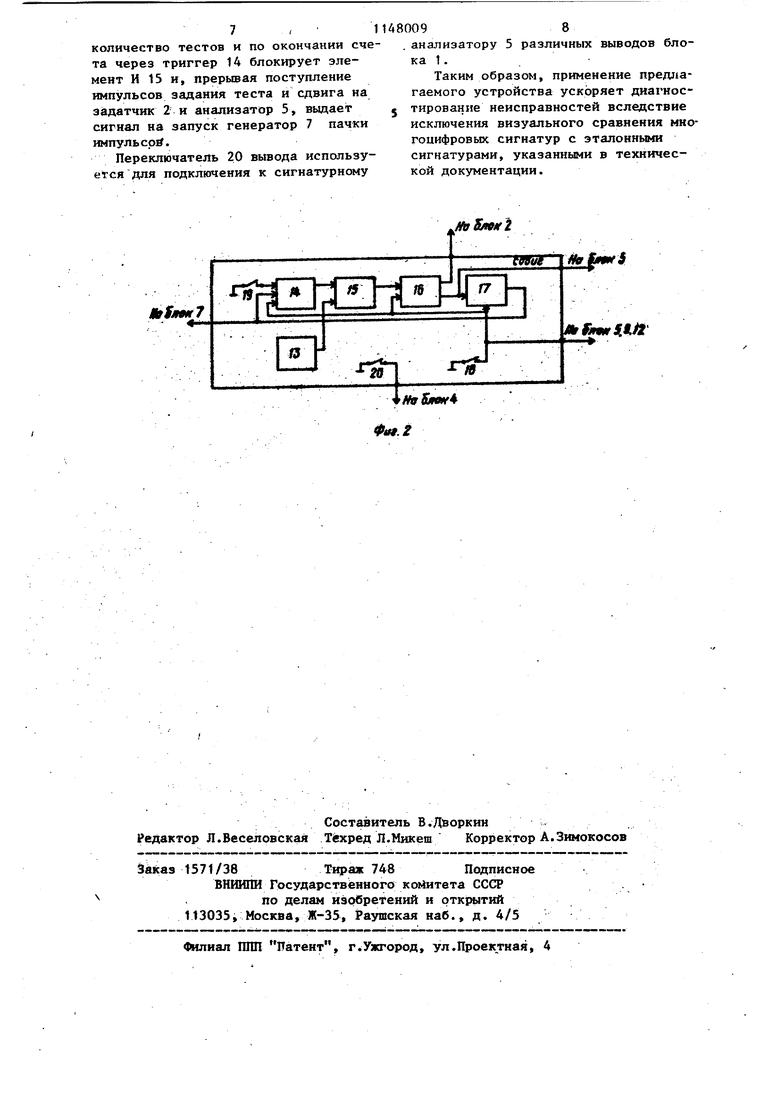

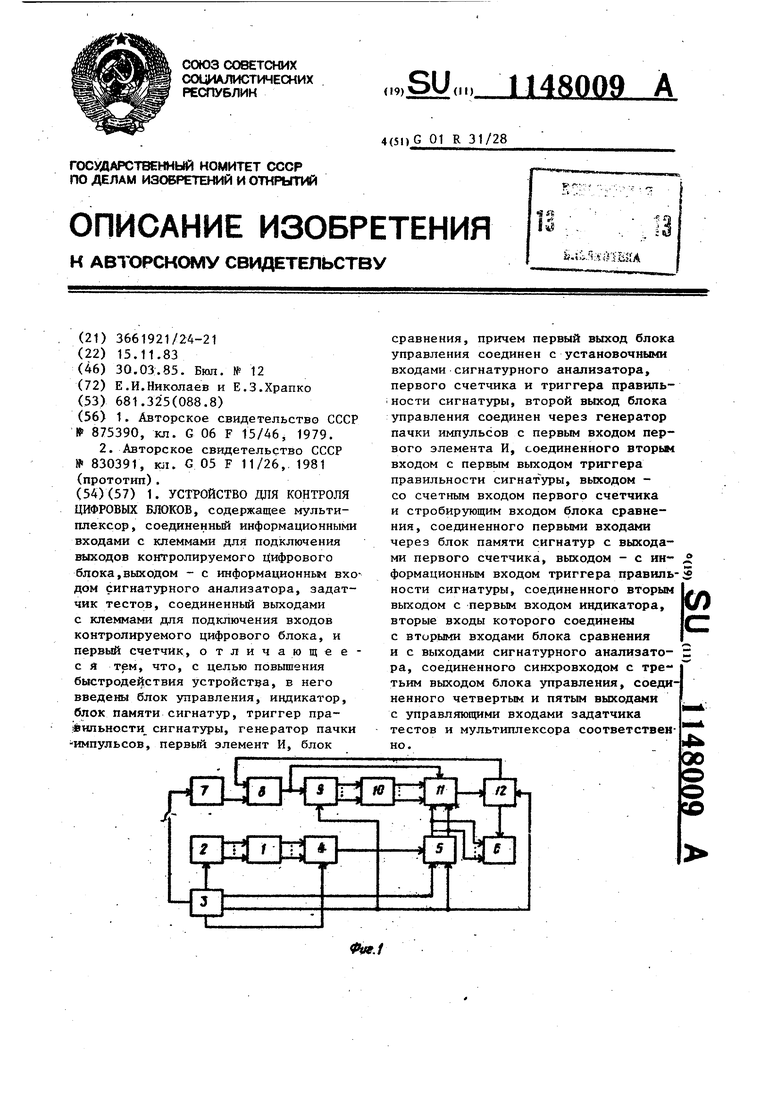

Поставленная цель достигается тем, что в устройство для контроля цифровых блоков, содержащее мультиплексор, соединенный информационными входами с клеммами для подключения выходов . контролируемого цифрового блока, выходом - с информационным входом сигнатурного анализатора, задатчик тестов, соединенный выходами с клеммами для подключения входов контролируемого цифрового блока, и первый счетчик, введены блок управления, индикатор, блок памяти сигнатур, триггер правильности сигнатуры, генератор пачки импульсов, первый элемент И, блок сравнения, причем первый выход блока управления соединен с установочными входами сигнатурного анализатора, первого счетчика и триггера правильности сигнатуры, второй выход блока управления соединен через генератор пачки импульсов с первым входом первого элемента И, соединенного BTopbiM входом с первым выходом триггера правильности сигнатуры, выг ХОДОМ - со счетным входом первого счетчика и стробирующим входом блока сравнения, соединенного первыми вхоI I дами через блок памяти сигнатур с вы ходами первого счетчика, выходом с информационным входом триггера пра вильности сигнатуры, соединенного вторым выходом с первым входом индикатора, вторые входы которого соединены с вторыми входами блока сравнения и с выходами сигнатурного анализатора, соединенного синхровходом с третьим выходом блока управления, соединенного четвертым и пятыми выхо дами с управляющими входами задатчика тестов и мультиплексора соответст венно. Блок управления содержит кнопку пуска, соединенную первым выводом с общей шиной устройства, вторым выводом - с первым установочным входом RS-триггера, соединенного- вторым установочным входом с вторым выходом блока и с выходом второго счетчика, третьим установочным входом - с уста новочными входами счетного триггера, второго счетчика, с первым выходом блока и с первым выводом кнопки исходной установки, соединенной вторым выводом с общей шиной устройст ва, выход RS-триггера соединен с первым входом второго элемента И, соединенного вторым входом свыходом генератора импульсов, выходом со счетным входом счетного триггера, соединенного первым выходом с четвер тым выходом блока, вторым выходом со счетным входом второго счетчика и с третьим выходом блока, переключатель вывода контролируемого цифрового узла, соединенный первыми вьшодами с общей шиной устройства, вторыми вьшодами - с пятыми выходами блока. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональная схема блока управления. Устройство дпя контроля цифровых .блоков содержит контролируемый цифровой блок 1, задатчик 2 тестов, блок 3 управления, мультиплексор 4, сигнатурный анализатор 5, индикатор 6, генератор 7 пачки импульсов, первый элемент 8 И, первый счетчик 9, блок ТО памяти сигна ур, блок 11 сравнения, триггер 12 правильности сигнатуры. Блок 3 управления содержит генера тор 13 импульсов, RS -триггер 14, второй элемент И 15, счетный триггер 16, второй счетчик 17, кнопку 18 094 исходной установки, кнопку 19 пуска, переключатель 20 вывода.-; Информационные входы мультиплексора 4 соединены с клеммами для подключения выходов контролируемого цифрового блока 1, выход - с информационным входом сигнатурного анализатора 5. Выходы задатчика 2 тестов соединены с клеммами для подключения входов контролируемого цифрового блока 1. Первый выход блока 3 управления соединен с установочными входами сигнатурного анализатора 5, первого счетчика 9 и триггера 12 правильности сигнатуры, второй выход блока 3 управления соединен через генератор 7 пачки импульсов с первым входом первого элемента И 8, соединенного вторым входом с первым выходом триггера 12 правильности сигнатуры, выходом - со счетным входом первого счетчика 9 и стробирующим входом блока 11 сравнения, соединенного первыми.входами через блок 10 памяти сигнатур с выходами первого счетчика 9, выходом - с информационным входом триггера 12 правильности сигнатуры, соединенного вторым выходом с первым входом индика-. тора 6, вторые входы которого соединены с вторыми входами блока 11 сравнения и с выходами сигнатурного анализатора 5, соединенного синхровкодом с третьим выходом блока 3 управления, соединенного четвертым и пятым выходами с управляющими входами задатчика 2 тестов и мультиплексора 4 соответственно. В блоке 3 управления кнопка 19 пуска соединена первым выводом с общей шиной устройства, вторым выводом - с перBbjM установочным входом RS -триггера 14, соединенного вторьм установочным входом с вторым выходом блока 3 и с выходом второго счетчика 17, третьим установочным входом - с установочными входами счетного триггера 16, второго счетчика 17, с первьы выходом блока 3 и с первым выводом кнопки 18 исходной установки, соединенной вторым выводом с общей шиной устройства, вькод RS-триггера 14 соединен с первым входом второго элемента И 15, соединенного вторым входом с выходом генератора 13 импульсов, выходом -. со счетньи входом счетного триггера 16, соединенного первым выходом с четвертьм вы5 11 ходом блока 3, вторым выходом - со счетным входом второго счетчика 17 и с третьим выходом блока 3, переключатель 20 вывода контролируемого цифрового узла соединен первыми выводами с общей шиной устройства, вторыми выводами - с пятыми выходами блока 3. Устройство работает следзпощим образом. Блок 3 управления вьщает сигнал начальной установки, который устанавливает сигнатурный анализатор 5, счетчик 9 и триггер 12 правильности сигнатуры в исходные состояния. С блока 3 управления в з&датчик 2 тестов поступает сигнал, по которому осуществляется вывод с задатчика 2 тестов первого теста на входы контролируемого блока 1. ,С одного из выходов блока 1 информация через мультиплексор А поступает на первый вход сигнатурного анализатора 5, представляющего собой сдвигающий регистр, охваченный обратными связями через схему сложения по модулю два. По первому сигналу сдвига с блока 3 управления эта информация записывается в первый разряд анализатора По второму сигналу с блока 3 управления задатчик 2 тестов выдает второй тест на блок 1, ас выхода блока 1 через мультиплексор 4 второй бит информации поступает на вход анализатора 5 и по второму сигналу сдвига с блока 3 записывается в ана лизатор 5 и т.д. до тех пор, пока вся тестовая программа не будет выведена из задатчика 2 тестов и вс последовательность кодов с одного из выходов контролируемого блока 1 не окажется свернутой в сигнатурном анализаторе 5. Свертка этой информа ции поступает в параллельном коде на входы блока 11 сравнения, на пер вые входы индикатора 6 и индицирует ся на нем в десятичном коде. После этого блок 3 управления вьщает сигнал на запуск генератора 7 пачки им лульсов, с выхода которого импульсы через открытый элемент И 8 поступаю на счетный вход счетчика 9. В соответствии с адресом, заданным счетчи ком 9, блок 10 памяти сигнатур с вы ходов выдает коды (сигнатуры), кото рые поступают на другие входы блока 11 сравнения. Блок 10 памяти сиг натур хранит набор эталонных сигнатур, соответствующих всем выходам контролируемого блока 1. Импульсы, прощедшие через элемент И 8 на блок 11, стробируют результат сравнения информации, полученной на сигнатурном анализаторе 5 и выводимой из блока 10,памяти сигнатур.В момент сравнения на выходе блока 11 вырабатывается импульс, который устанавливает триггер 12 в единичное состояние. Состояние триггера 12 индицируется на индикаторе 6. Одновременно триггер 12 блокирует элемент И 8 по второму входу, запирая поступление импульсов с генератора 7 на счетчик 9. В результате, если в блоке 10 памяти сигнатур.присутствует сигнатура, равная сигнатуре, снятой с вывода блока 1, то считается что данный вывод блока работает правильно, и переходят к контролю другого вьшода. Для этого блок управления 3- выдает сигнал на мультиплексор 4 и к сигнатурному анализатору 5 подключается другой вывод блока 1, с которого снимается сигнатура, и проверяется наличие этой сигнатуры в блоке 10 памяти этой сигнатуры. Если в составе блока 10 отсутствует сигнатура, записанная на анализаторе 5, то контролируемый блок 1 по проверяемому выводу считается неисправным. Индикация наличия или отсутствия совпадения снятой сигнатуры со списком эталонных сигнатур, хранящихся в блоке 10, ведется по лампе индикатора и не требуется визуально сравнивать многоразрядные сигнатуры с эталонными, записанными в документации. Блок управления 3 работает следующим образом. При нажатии кнопки 18 триггер 14, триггер 1Ь и счетчик 17 устанавливаются в исходные состояния, и на анализатор, 5, счетчик 9 и триггер 12 выдается сигнал начальной установки. При нажатии кнопки 19 триггер 14 открывает элемент И 15, и импульсы с генератора 13 поступают на счетный вход триггера 16. С выходов триггера 16 снимаются две последовательности импульсов, сдвинутые друг относительно друга на половину такта. Одна из последовательностей используется для задания тестов из задатчика 2, другая - для сдвига информации в анализаторе 5. Сетчик 17 подсчитывает 7 , количество тестов и по окончании сче та через триггер 14 блокирует элемент И 15 и, прерывая поступление импульсов задания теста и сдвига на эадатчик 2 и анализатор 5, выдает сигнал на запуск генератор 7 пачки импульсов. Переключатель 20 вывода используется для подключения к сигнатурному

jmSMtei 098 анализатору 5 различных выводов блока 1. Таким образом, применение предлагаемого устройства ускоряет диа1ностирование неисправностей вследствие исключения визуального сравнения многоцифровых сигнатур с эталонными сигнатурами, указанными в технической документации. AtfMft iJi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков | 1979 |

|

SU875390A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1985-03-30—Публикация

1983-11-15—Подача