Изобретение относится к контрольно- измерительной Технике и может быть использовано при регулировке, контроле и диагностике неисправностей цифровых .блоков на интегральных схемах.

Целью изобретения является повышение достоверности контроля.

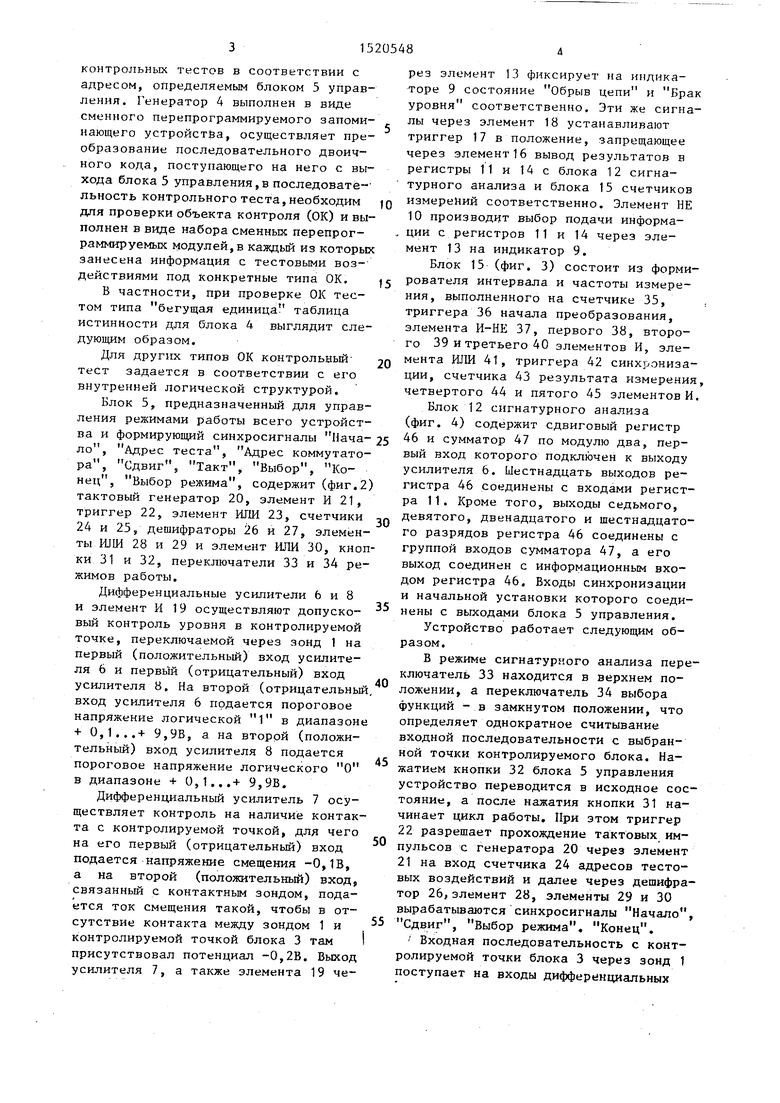

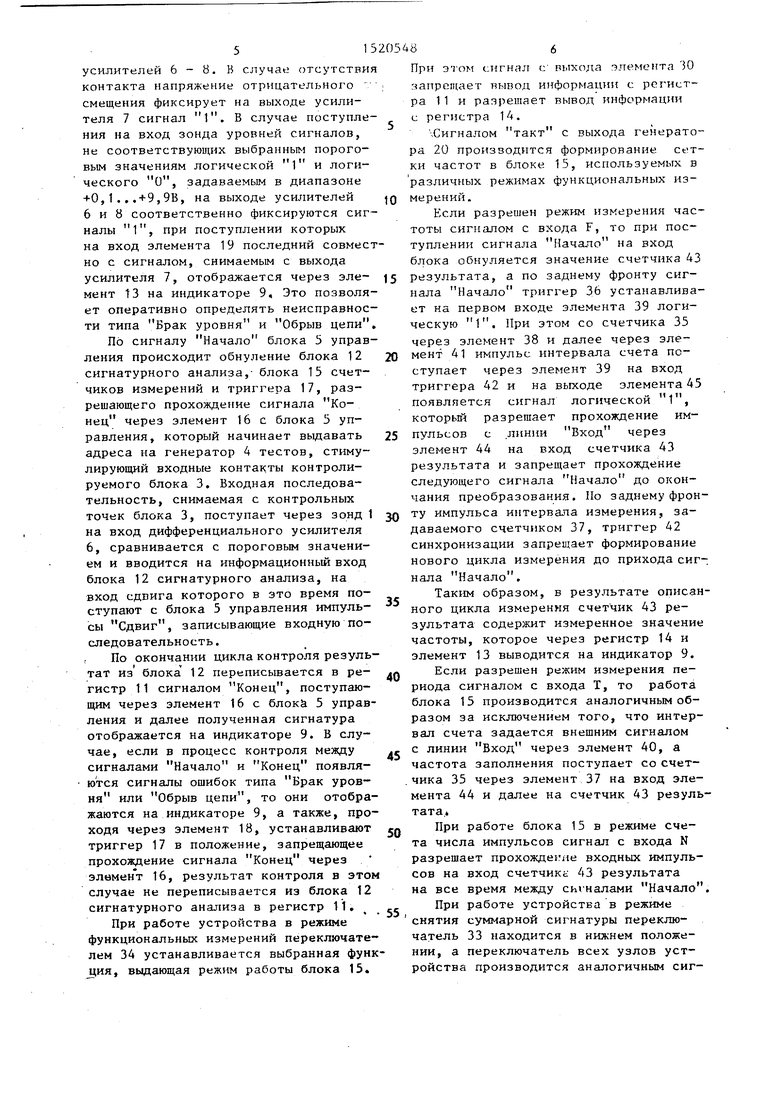

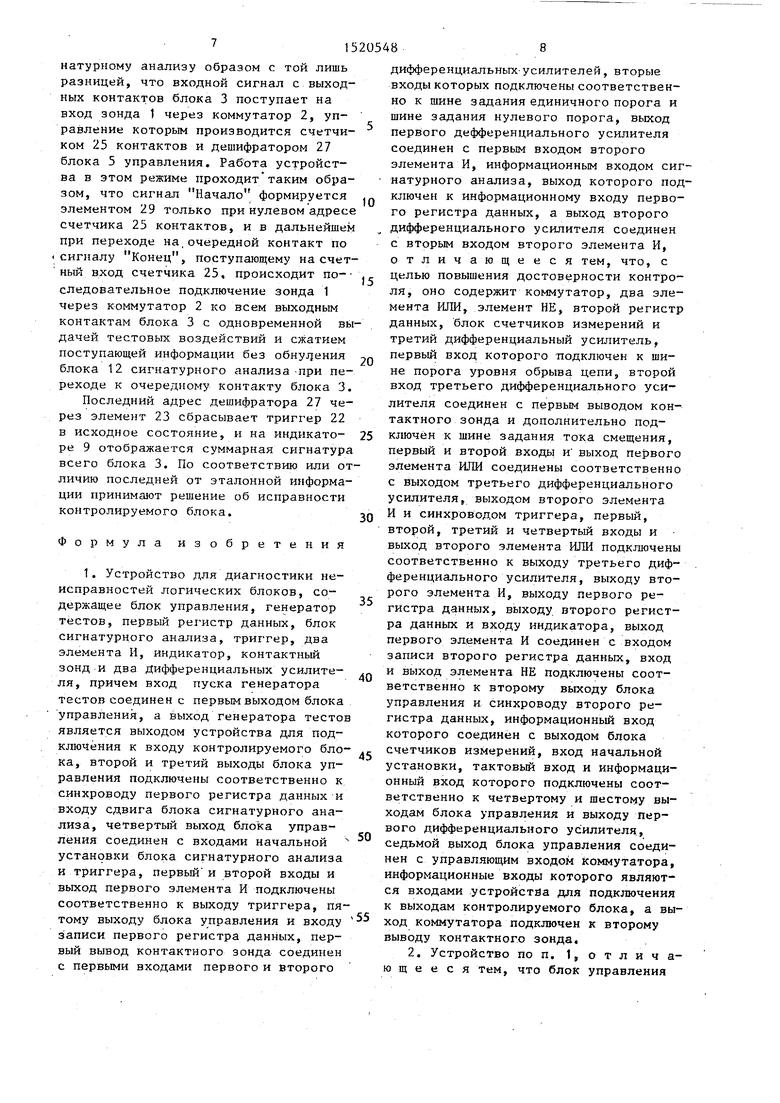

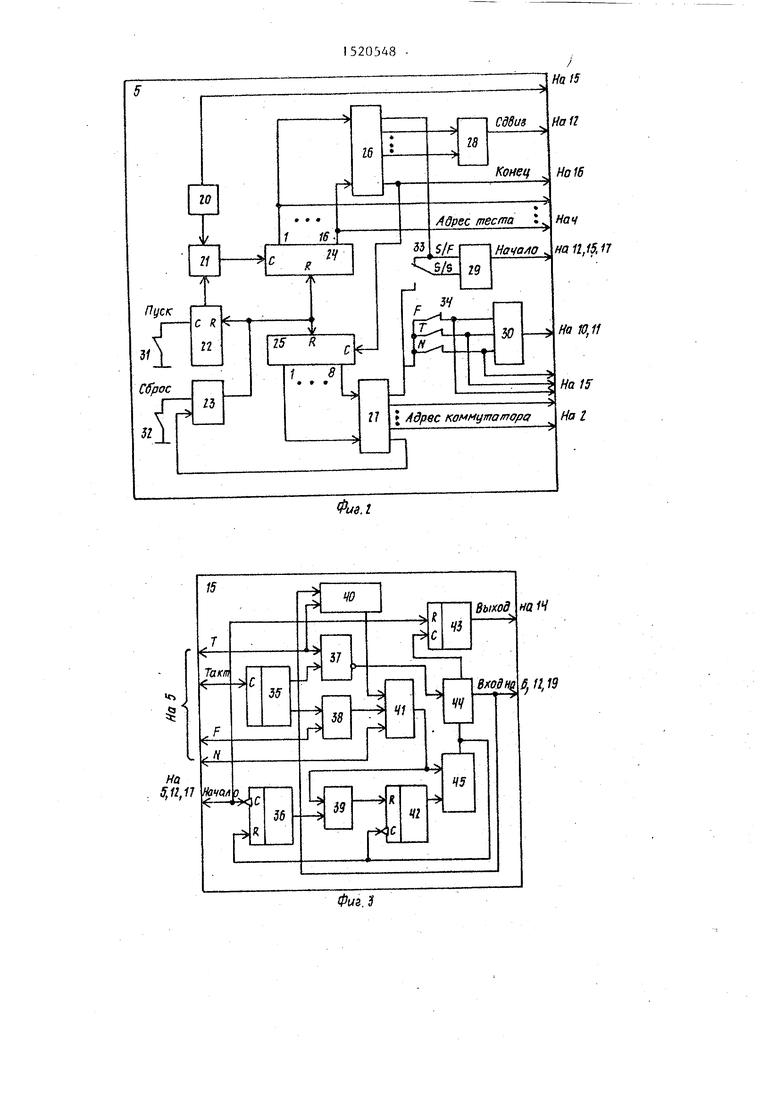

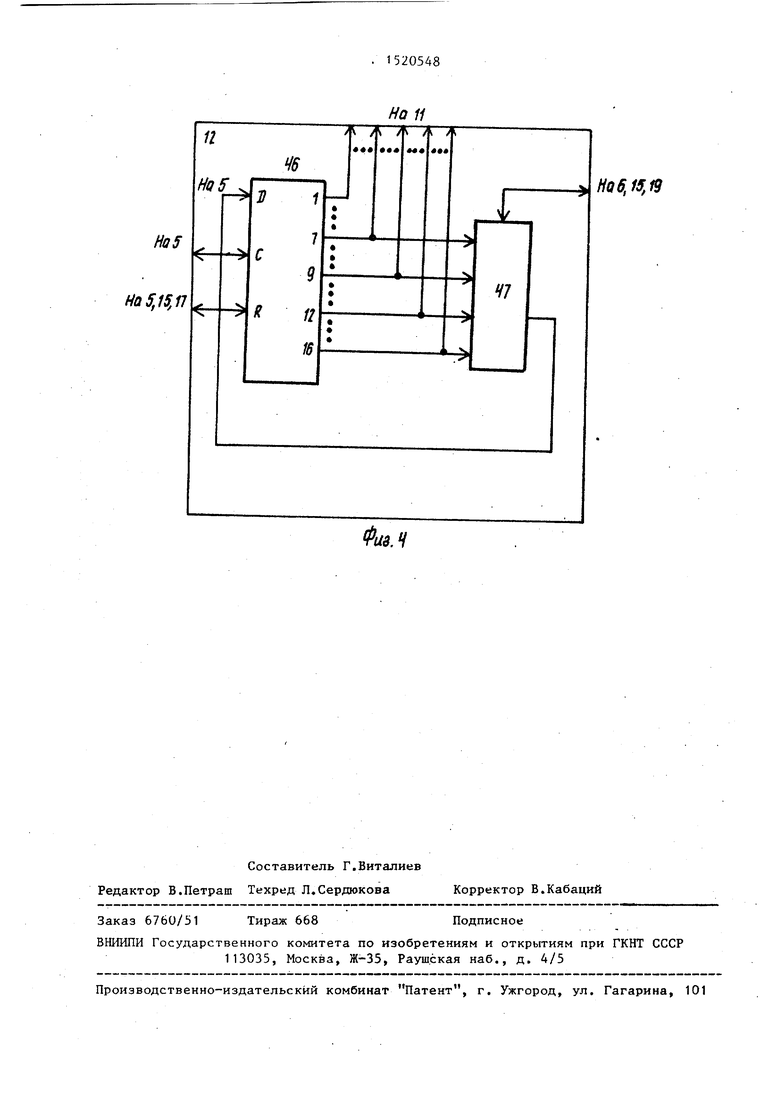

На фиг. 1 приведена структурная схема устройства для диагностики неисправностей логических блоков; на фиг. 2 - функциональная схема блока управления;.на фиг. 3 - функциональная схема блока счетчиков измерений; на фиг. 4 - функциональная схема блока сигнатурного анализа.

Устр ойство для диагностики неис- пра:вностей логических блоков (фиг. 1) содержит контактный зонд 1, коммутатор 2, контролируемый блок 3, генератор 4 тестов, блок 5 управления.

дифференциальные усилители 6-8, ин- S дикатор 9, элемент НЕ 10, первый регистр 11 данных, блок 12 сигнатурного анализа, элемент ИЛИ 13, второй регистр 14 данных, блок 15 счетчиков измерений, элемент И 16, триггер 17, элемент ИЛИ 18, элемент И 19.

Контактный зонд 1 производит подключение контролируемых выводов цифрового блока 3 через дифференциальный усилитель 8 к входам блока 12 сигнатурного анализа и блока 15 счетчиков измерений.

Коммутатор 2 осуществляет автоматическое подключение вьшодов контролируемого блока по адресу, задаваемому блоком 5 управления, к выходу контактного зонда 1.

Генератор 4 тестов выдает на контролируемый блок 3 последовательность

контрольных тестов в соответствии с адресом, определяемым блоком 5 управления. Генератор 4 выполнен в виде сменного Перепрограммируемого запоминающего устройстйа, осуществляет преобразование последовательного двоичного кода, поступающего на него с выхода блока 5 управления,в последовате- льность контрольного теста, необходим для проверки объекта контроля (ОК) и выполнен в виде набора сменных перепрограммируемых модул ей, в каждьм из которых занесена информация с тестовыми воздействиями под конкретные типа ОК.

В частности, при проверке ОК тестом типа бегущая единица таблица истинности для блока 4 выглядит следующим образом.

Для других типов ОК контрольный- тест задается в соответствии с его внутренней логической структурой.

Блок 5, предназначенный для управления режимами работы всего устройстрез элемент 13 фиксирует на индикаторе 9 состояние Обрыв цепи и Брак уровня соответственно. Эти же сигналы через элемент 18 устанавливают триггер 17 в положение, запрещающее через элемент 16 вывод результатов в регистры 11 и 14 с блока 12 сигнатурного анализа и блока 15 счетчиков измерений соответственно. Элемент НЕ 10 производит выбор подачи информации с регистров 11 и 14 через элемент 13 на индикатор 9.

Блок 15 (фиг. 3) состоит из формирователя интервала и частоты измерения, выполненного на счетчике 35, триггера 36 начала преобразования, элемента И-НЕ 37, первого 38, второго 39 и третьего 40 элементов И, элемента ИЛИ 41, триггера 42 синхронизации, счетчика 43 результата измерения четвертого 44 и пятого 45 элементов И

Блок 12 сигнатурного анализа (фиг. 4) содержит сдвиговый регистр

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1981 |

|

SU1003099A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1267422A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

Изобретение относится к области контрольно-измерительной техники и может быть использовано при регулировке, контроле и диагностике неисправностей цифровых блоков на интегральных схемах. Целью изобретения является повышение достоверности контроля. С этой целью в устройство , содержащее блок управления, генератор тестов, первый регистр данных, блок сигнатурного анализа, триггер, два элемента И, индикатор, контактный зонд и два дифференциальных усилителя, введены коммутатор, два элемента ИЛИ, элемент НЕ, второй регистр данных, блок счетчиков измерений и третий дифференциальный усилитель. 1 з.п.ф -лы, 4 ил.

ва и формирующий синхросигналы Нача- 25 сумматор 47 по модулю два, перло , ра, нец.

Адрес теста , Адрес коммутато- Сдвиг, Такт, Выбор, Ко Выбор режима, содержит (фиг.2 тактовый генератор 20, элемент И 21, триггер 22, элемент И1Ш 23, счетчики 24 и 25, дещифраторы 26 и 27, элементы ШШ 28 и 29 и элемент ИЛИ 30, кнопки 31 и 32, переключатели 33 и 34 режимов работы.

Дифференциальные усилители 6 и 8 и элемент И 19 осуществляют допуско- вый контроль уровня в контролируемой точке, переключаемой через зонд 1 на Первый (положительный) вход усилителя 6 и первый (отрицательный) вход усилителя 8, На второй (отрицательный вход усилителя 6 подается пороговое напряжение логической 1 в диапазоне + 0,1...+ 9,9Б, а на вторрй (положительный) вход усилителя 8 подается пороговое напряжение логического О в диапазоне + 0,1... 9,9В.

Дифференциальный усилитель 7 осуществляет контроль на наличие контакта с контролируемой точкой, для чего на его первый (отрицательный) вход подается напряжение смещения -0,1В, а на второй (положительный) вход, связанный с контактным зондом, подается ток смещения такой, чтобы в отсутствие контакта между зондом 1 и контролируемой точкой блока 3 там присутствовал потенциал -0,2В. Выход усилителя 7, а также элемента 19 че

5

0

Q

5

0

5

вый вход которого подключен к выходу усилителя 6. Шестнадцать выходов регистра 46 соединены с входами регистра 11. Кроме того, выходы седьмого, девятого, двенадцатого и шестнадцатого разрядов регистра 46 соединены с группой входов сумматора 47, а его выход соединен с информационным входом регистра 46, Входы синхронизации и начальной установки которого соединены с выходами блока 5 управления.

Устройство работает следующим образом.

В режиме сигнатурного анализа переключатель 33 находится в верхнем положении, а переключатель 34 выбора функций - в замкнутом положении, что определяет однократное считывание входной последовательности с выбранной точки контролируемого блока. Нажатием кнопки 32 блока 5 управления устройство переводится в исходное сос- тояни ;, а после нажатия кнопки 31 начинает цикл работы. При этом триггер 22 разрешает прохождение тактовых импульсов с генератора 20 через элемент 21 на вход счетчика 24 адресов тестовых воздействий и далее через дешифратор 26, элемент 28, элементы 29 и 30 вырабатываются синхросигналы Начало, Сдвиг, Выбор режима. Конец.

- Входная последовательность с контролируемой точки блока 3 через зонд 1 поступает на входы дифференциальных

51

усилителей 6 - 8. В случае отсутстви контакта напряжение отрицательного смещения фиксирует на выходе усилителя 7 сигнал 1. В случае поступления на вход зонда уровней сигналов, не соответствующих выбранным пороговым значениям логической 1 и логического О, задаваемым в диапазоне +0,1 .,, 9,9В, на выходе усилителей 6 и 8 соответственно фиксируются сигналы 1, при поступлении которых на вход элемента 19 последний совмесно с сигналом, снимаемым с выхода усилителя 7, отображается через эле- мент t3 на индикаторе 9, Это позволяет оперативно определять неисправности типа Брак уровня и Обрыв цепи

По сигналу Начало блока 5 управления происходит обнуление блока 12 сигнатурного анализа,- блока 15 счетчиков измерений и триггера 17, разрешающего прохождение сигнала Конец через элемент 16 с блока 5 управления, который начинает выдавать адреса на генератор 4 тестов, стимулирующий входные контакты контролируемого блока 3, Входная последовательность, снимаемая с контрольных точек блока 3, поступает через зонд 1 на вход дифференциального усилителя 6, сравнивается с пороговым значением и вводится на информационный вход блока 12 сигнатурного анализа, на вход сдвига которого в это время поступают с блока 5 управления импуль- сы Сдвиг, записывающие входную последовательность .

; По окончании цикла контроля результат из блока 12 переписывается в ре- гистр 11 сигналом Конец, поступающим через элемент 16 с блока 5 управления и далее полученная сигнатура отображается на индикаторе 9. В случае, если в процесс контроля между сигналами Начало и Конец появляются сигналы ошибок типа Брак уровня или Обрыв цепи, то они отображаются на индикаторе 9, а также, проходя через элемент 18, устанавливают триггер 17 в положение, запрещающее прохождение сигнала Конец через элемент 16, результат контроля в этом случае не переписывается из блока 12 сигнатурного анализа в регистр 11. ,

При работе устройства в режиме функциональных измерений переключателем 34 устанавливается выбранная функция, выдающая режим работы блока 15.

486

При этом сигнал с выхода злe cltтa 30 запрещает вывод информащ и с регистра 11 и разрешает вывод информации с регистра 14.

Сигналом такт с выхода генератора 20 производится формирование сетки частот в блоке 15, используемых в различных режимах функциональных измерений.

Если разрешен режим измерения частоты сигналом с входа F, то при поступлении сигнала Начало на вход блока обнуляется значение счетчика 43 результата, а по заднему фронту сигнала Начало триггер ЗЬ устанавливает на первом входе элемента 39 логическую 1. При этом со счетчика 35 через элемент 38 и далее через элемент 41 импульс интервала счета поступает через элемент 39 на вход триггера 42 и на выходе элемента 45 появляется сигнал логической 1, который разрешает прохождение импульсов с .линии Вход через элемент 44 на вход счетчика 43 результата и запрещает прохождение следующего сигнала Начало до окончания преобразования. По заднему фронту импульса интервала измерения, задаваемого счетчиком 37, триггер 42 синхронизации запрещает формирование нового цикла измерения до прихода сигнала Начало.

Таким образом, в результате описанного цикла измерения счетчик 43 результата содержит измеренное значение частоты, которое через регистр 14 и элемент 13 выводится на индикатор 9,

Если разрешен режим измерения периода сигналом с входа Т, то работа блока 15 производится аналогичным образом за исключением того, что интервал счета задается внешним сигналом с линии Вход через элемент 40, а частота заполнения поступает со счетчика 35 через элемент 37 на вход элемента 44 и далее на счетчик 43 результата

При работе блока 15 в режиме счета числа импульсов сигнал с входа N разрешает прохождение входных импульсов на вход счетчикс 43 результата на все время между сы налами Начало

При работе устройства в режиме снятия суммарной сигнатуры переключатель 33 находится в нижнем положении, а переключатель всех узлов устройства производится аналогичным сигнатурному анализу образом с той лишь разницей, что входной сигнал с выходных контактов блока 3 поступает на вход зонда 1 через коммутатор 2, управление которым производится счетчиком 25 контактов и дешифратором 27 блока 5 управления. Работа устройства в этом режиме проходит таким образом, что сигнал Начало формируется элементом 29 только при нулевом адресе счетчика 25 контактов, и в дальнейшем при переходе на,очередной контакт по сигналу Конец, поступающему на счетный вход счетчика 25, происходит по- следовательное подключение зонда 1 через коммутатор 2 ко всем выходным контактам блока 3 с одновременной выдачей тестовьпх: воздействий и сжатием поступающей информации без обну1|ения блока 12 сигнатурного анализа-при переходе к очередному контакту блока 3, Последний адрес дешифратора 27 через элемент 23 сбрасывает триггер 22 в исходное состояние, и на индикаторе 9 отображается суммарная сигнатура всего блока 3. По соответствию или отличию последней от эталонной информации принимают решение об исправности контролируемого блока.

Формула изобретения

дифференциальных- усилителей, вторые входы которых подключены соответственно к шине задания единичного порога и шине задания нулевого порога, выход первого дефференциального усилителя соединен с первым входом второго элемента И, информационным входом сигнатурного анализа, выход которого подключен к информационному входу первого регистра данных, а выход второго дифференциального усилителя соединен с вторым входом второго элемента И,

10

15

20

25

30

35

40

45

50

55

целью повышения достоверности контроля, оно содержит коммутатор, два элемента ШШ, элемент НЕ, второй регистр данных, блок счетчиков измерений и третий дифференциальный усилитель, первый вход которого подключен к шине порога уровня обрыва цепи, второй вход третьего дифференциального усилителя соединен с первым выводом контактного зонда и дополнительно подключён к шине задания тока смещения, первый и второй входь и выход первого элемента ИЛИ соединены соответственно с выходом третьего дифференциального усилителя, выходом второго элемента И и синкроводом триггера, первый, второй, третий и четвертый входы и выход второго элемента ИЛИ подключены соответственно к выходу третьего дифференциального усилителя, выходу второго элемента И, выходу первого регистра данных, выходу второго регистра данных и входу индикатора, выход первого эдемента И соединен с входом записи второго регистра данных, вход и выход элемента НЕ подключены соответственно к второму выходу блока управления и синхроводу второго регистра данных, информационный вход которого соединен с выходом блока счетчиков измерений, вход начальной установки, тактовый вход и информационный вход которого подключены соответственно к четвертому и шестому выходам блока управления и выходу первого дифференциального усилителя., седьмой выход блока управления соединен с управляющим входом коммутатора, информационные входы которого являются входами .устройства для подключения к выходам контролируемого блока, а выход коммутатора подключен к второму выводу контактного зонда,

целью повышения достоверности контроля, оно содержит коммутатор, два элемента ШШ, элемент НЕ, второй регистр данных, блок счетчиков измерений и третий дифференциальный усилитель, первый вход которого подключен к шине порога уровня обрыва цепи, второй вход третьего дифференциального усилителя соединен с первым выводом контактного зонда и дополнительно подключён к шине задания тока смещения, первый и второй входь и выход первого элемента ИЛИ соединены соответственно с выходом третьего дифференциального усилителя, выходом второго элемента И и синкроводом триггера, первый, второй, третий и четвертый входы и выход второго элемента ИЛИ подключены соответственно к выходу третьего дифференциального усилителя, выходу второго элемента И, выходу первого регистра данных, выходу второго регистра данных и входу индикатора, выход первого эдемента И соединен с входом записи второго регистра данных, вход и выход элемента НЕ подключены соответственно к второму выходу блока управления и синхроводу второго регистра данных, информационный вход которого соединен с выходом блока счетчиков измерений, вход начальной установки, тактовый вход и информационный вход которого подключены соответственно к четвертому и шестому выходам блока управления и выходу первого дифференциального усилителя., седьмой выход блока управления соединен с управляющим входом коммутатора, информационные входы которого являются входами .устройства для подключения к выходам контролируемого блока, а выход коммутатора подключен к второму выводу контактного зонда,

содержит тактовьгй, генератор, элемент И. триггер, четыре элемента Ш1И, два счетчика, два дешифратора, кнопку пуска, кнопку сброса и два переключателя, при этом первый и второй выходы тактового генератора соединены соответственно с шестым выходом блока и первым входом элемента И, второй вход и выход которого подключены соответственно к выходу триггера и счетному входу первого счетчика, синхровод триггера соединен с выходом кнопки пуска, первый вход и выход первого элемента ШТИ подключены соответственно к выходу кнопки сброса и входам начальной установки триггера и первого и второго счетчиков, выходы первого и второго счетчиков соединены с входами соответственно первого и второго дешифраторов, кроме того, выход первого счетчика подключен к первому выходу блока, первые выходы первого и второго дешифраторов соединены соУ(Н

/

10

2054810

ответственно с первым и вторым контактами первого переключателя, вход и выход второго элeмeнfa Ш1И подключены соответственно к второму выходу первого дешифратора и третьему выходу блока, третий выход первого дешифратора соединен с тактовым входом

второго счетчика и пятым вЫходом блока, первьй и второй входы и выход третьего элемента ШШ подключены соответственно к первому выходу первого дешифратора, третьему контакту первого переключателя и четвертому выходу блока, первые контакты второго переключателя соединены с шиной кулевого потенциала, а вторые контакты подключены к шестому выходу блока и входам четвертого элемента ИЛИ, выход которого соединен с вторым выходом блока, а второй и третий выходы второго дешифратора подключены соответственно к седьмому выходу блока и второму входу первого элемента ШШ.

15

20

Ф1Я.1

f

На 5,11,11

Сдвиз

-

Конец

/песта

Нача/JO

/ На 15

НаП

Но 16

Нач

на 11,15, П

J

5У

Т

30

На Ю, 11

J /f фес коммутатора

Half Наг

HQf,15,n

Н06,1У.19

Фаз. Ч

| Электроника | |||

| Иерев | |||

| с англ., 1977, № 5, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1981 |

|

SU1003099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1987-04-24—Подача