(54) УСТГОЙСТВО ДЛЯ КОНТЮЛЯ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1070562A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для контроля монтажа | 1984 |

|

SU1211672A1 |

| Сигнатурный анализатор для контроля цифровых блоков | 1981 |

|

SU1003099A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Устройство для контроля и диагностики многоканальной цифровой аппаратуры | 1986 |

|

SU1348758A1 |

| Устройство для контроля многоканальной цифровой аппаратуры | 1986 |

|

SU1397860A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1160417A1 |

I

Изобретение относится к вычислительной технике и. может быть использовано для контроля логических блоков средств ЦВТ.

Известно устройство для контроля и диагностики логических блоков, содержащее задатчик . тестов, соединенный выходами со входами контролируемого логического блока, выходы которого соединены со входамиЧигнатурного анализатора 1.

Недостатком устройства является низкое быстродействие в режиме контроля логически с блоков, вслед ствие необходимости последовательного во времени опроса логических состояний всех выходов контролируемого блока для получения сигнатур по каждому из них, и неавтоматизированного процесса сравнения большого числа полученных сигнатур «с заданными в технической документации на контролируемый логический блок.

Наиболее близким техническим решением к предлагаемому является устройство для локализации неисправностей электронного оборудования, содержащее сигнатурный анализатор, соединенный выходом со входом блока индика,ции, Генератор импульсов, соединенный вводом с первым выходом блока управления, второй выход которого соединен с первым входом сигнатурного анализатора, третий выход - со входом задатчика тестов, соединенного выходами со входами контролируемого логического блока, регистры сдвига, первые и вторые выходы которых соединены с первым и вторым входами сумматоров соответственно 2.

Это устройство обеспечивает получение сигнатурных характеристяк Для п - выходов контролируемого электронного оборудования.

Недостатком уст ройства является низкое быстродействие вследствие последовательного во времени опроса логических состояний каждого выхода контролируемого электроиного оборудования с помощью коммутатора. Количество тактов необходимое для реализации полной тестовой пррграммы из N тестов в известном устройстве равно Nun,

Цель изобретения - повышение быстродействия устройства.

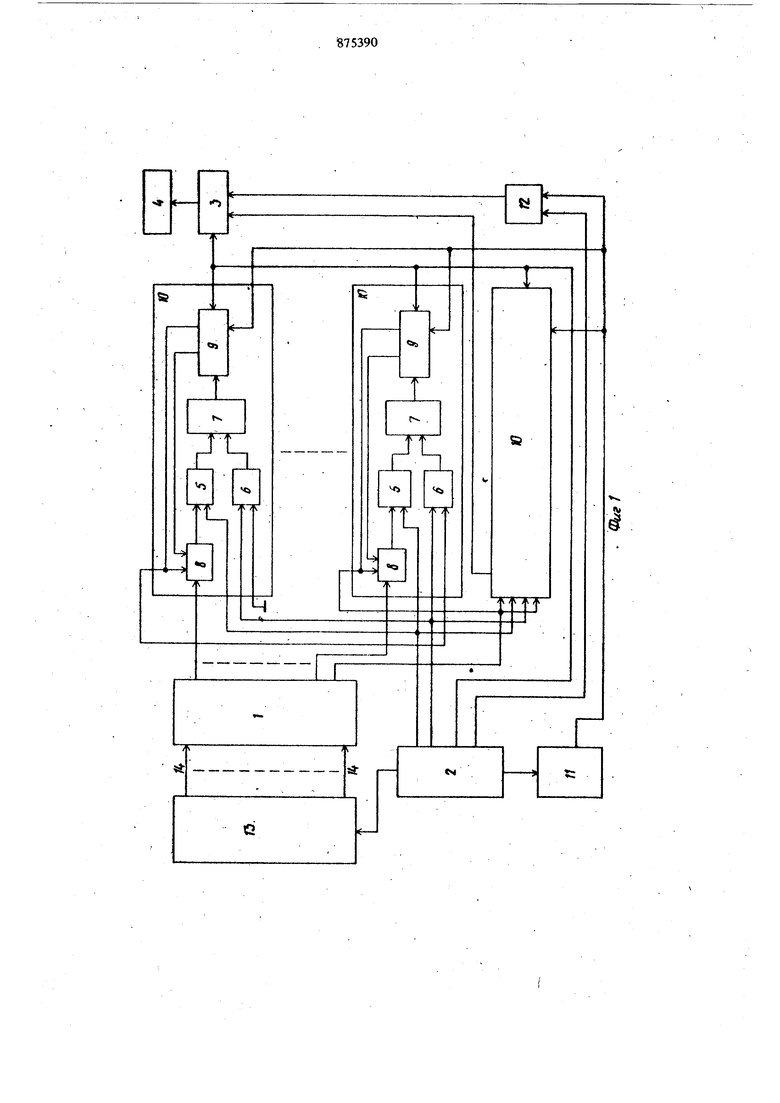

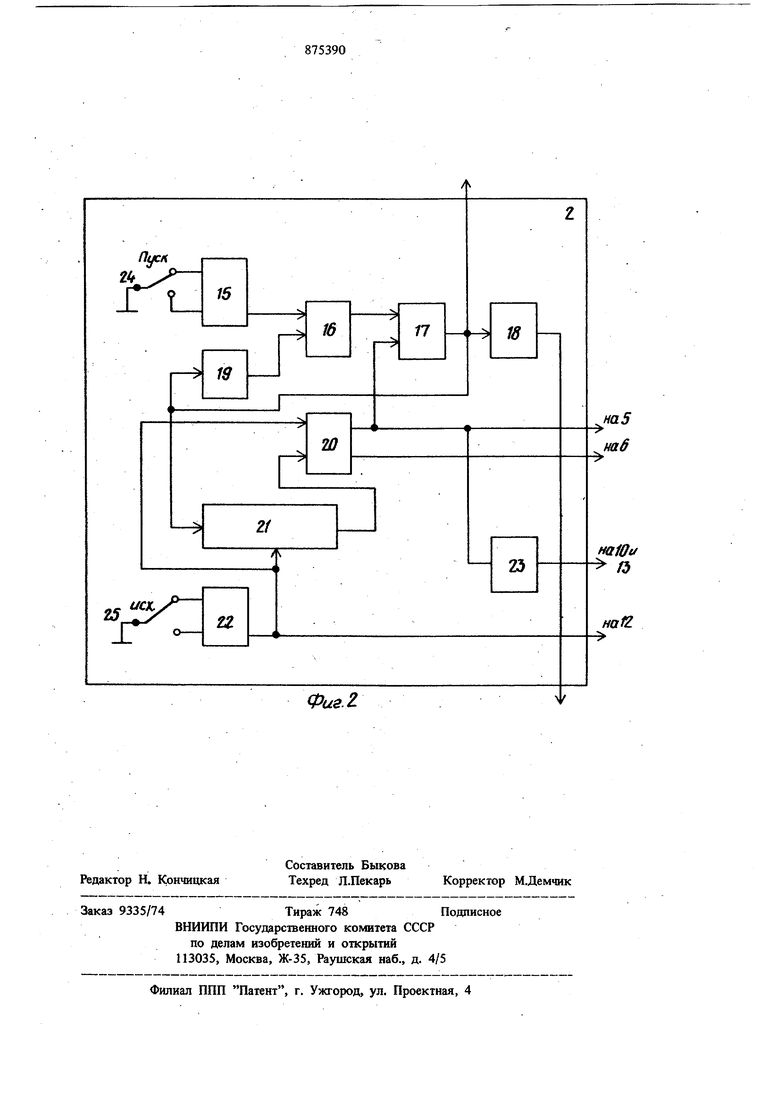

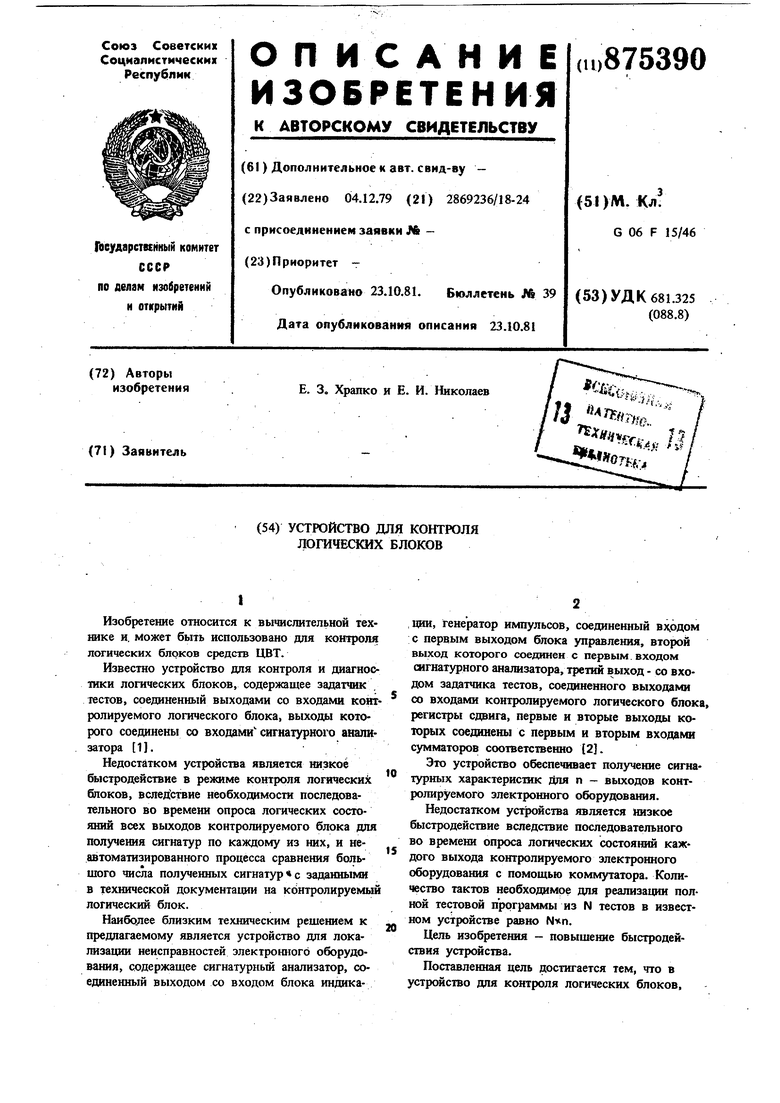

Поставленная цель достигается тем, что в устройство для контроля логических блоков. 38 содержащее сигнатурный анализатор, соединенный выходом со входом блока индикации, генератор импульсов, соединенный входом с первым выходом блока управления, второй выход которого соединен с первым входом сигнатурного анализатора, третий выход - со входом задатчика тестов, соединенного выходами со входами контролируемого логического блока; регистры сдвига, первые и вторые выходы которых соединены с первыми и вторыми выходами сумматоров соответственно, введены первая и вторая группы элементов И по числу вы ходов контролируемого логического блока, элемент И и элементы ИЛИ, первые и вторые входы которых соединены с выходами соответствующих элементов И первой и второй rpynf элементов И, а выходы - с первыми входами регистров сдвига, первые входы элементов И первой и второй групп соединены соответственно с четвертыми и пятым выходами блока управления, второй входы которого соединен с вторыми входами регистров сдвига, а шестой блока управления соединен с первым входом элемента И, соединенного выходом со вторым входом сигнатурного анализатора, второй вход элемента И соединен с выходом генератора импульсов и третьими входами регистров сдвига и сигнатурного анализатора, вторые входы соответствующих элементов И второй группы соединены с вторыми входами соответствующих элементов И первой группы, а третьи выход сумматоров соеданены с соответствукядими выходами контролируемого ;1огического блока, второй вход п-ого сумматора соединен с третьим входом сигнатурного анализатора, а также блок управления содержит элемент ИЛИ, элемент И, первый и второй элементы задержки, счетчик, инвертор, первый и второй переключатели, первый, второй и третий триггеры, причем первый, второй, третий, четвертый и пятый выходы блока управления соединены с выходами первого элемента задержки, инвертора, элемента И, первым и вторым выходами первого триггера, выходом второго триггера соответственно, первый вход счетчика соединен с выходом второго триггера и первым входом первого триггера, выход - со вторым входом первого триггера, второй вход - со входами .первого и второго элементов задержки и выхо дом элемента И, первый вхоД которого соединен с первым выходом первого триггера и выхоДом инвертора, второй вход с выходом элемента ИЛИ, соединенного первым входом с вы ходом второго элемента задержки, вторым вхо дом через третий триггер с выходами первого переключателя, выходы второго переключателя соединены со входами второго триггера. На фиг. 1 приведена блок-схема предлага. емого устройства; на фиг. 2 - функциональная схема блока управления. Устройство для контроля логических блоков 1содержит блок 2 управления, сигнатурный анализатор 3, блок 4 индикации, первые 5 и вторые 6 элементы И, элементы 7 ИЛИ, сумматоры 8 и регистры 9 сдвига, образующие сигнатурные анализаторы 10, генератор 11 импульсов, третий 12 элемент И и задачтик 13 тестов с выходами 14. Блок 2 управления содержит третий триггер 15, элемент 16 ИЛИ, элемент 17 И, первый 18 и второй 19 элементы задержки, первый триггер 20, счетчик 21, второй триггер 22, инвертор 23, первый 24 и второй 25 переключатели. Устройство работает следующим образом. Блок 2 управления выдает сигналы Начальная установка, устанавливает регистры 9 и сиг натурный анализатор 3 в исходное состояние. Задатчик 13 тестов задает на блок 1 информацию первого теста. С выходов блока 1 инфорция через сумматоры 8, выполняющие операцию сложения по модулю два, через элементы 5, которые открыты стробом с блока 2 и элементы 7 поступают на входы регистров 9. В это время блок 2 закрывает элементы 6. Генератор 11 по импульсам сдвига записьшает эту информацию параллельно в первые разряды п сдвигающих регистров 9, каждый из которых имеет m - разрядов. Блок 2 блокирует элемент 12, поэтому импульсы сдвига не поступают на сигнатурный анализатор 3 и не записывают в него информации. Затем задатчик 13 выдает второй тест. Блок 2по второму импульсу сдвига переписывает в регистры 9 с учетом влияния обратных связей через сумматоры 8 информацию с выходов блока 1. В результате реализации всей программы блок 2 записывает в регистры 9 поканально в сжатом (в сигатуры) виде информацию с выходов блока 1. По окончании программы блок 2 закрывает элементы 5 и открывает элементы 6 и 12. Генератор 11 выдает импульсный пакет, с числом импульсов N п, по которым информация из регистров 9 предыдущих каналов через открытые элементы 6 и 7 поступает в регистры последующих каналов, а с последнего канала в анализатор 3. В результате анализатор 3 содержит сжатую информацию, являющуюся выходной реакцией контролируемого блока на входную тестовую программу, которую индицирует блок 4 индикации. Значение этой информации в оцифрованном виде оператор сравнивает с эталонным значением, приведенным в технических условиях на контролируемый блок и делает заключение о его исправности. Количество тактов, необходимое дпя реализации всей программы равно N + m-n. что значительно меньще величины N п, Блок управления 2 работает следующим образом. По нажатию переключателя 25 с выхода триггера 22 выдается импульс, который устанавливает в нулевое состояние счетчик 21 и триггер 20. Сигнал исходного состояния поступает в сигнатурные анализаторы 3 и 10. Сигналы с обоих плеч триггера 20 поступают на элементы 5 и 6, а через инвертор 23 на злемент 12,. Элемент 17 открыт с триггера 20. По нажатию переключателя 24 триггер 15 выдает импульс, проходящий через элемент 16 ИЛИ и элемент 17 И. С элемента 17 И а1гнал поступает на задатчик 13 тестов через элемент 19 задержки, элемент 16 вновь на злемент 17 и т.д., создавая непрерьтную последоватеш1ност импульсов, которые осуществляют вьгаод очередных тестов с заддтчика 13 тестов. Через элемент 18 задержки эти же импульсы поступают в качестве сигналов сдвига на генератор 11. Импульсы запуска с элемента 17 подсчитывает счетчик 21, емкость которого равна числу элементарных тестов программы. По окончании программы сигнал переполнения счетчика 21 переводит триггер 20 в единичное состояние обрьшая непрерывную последовательность импульсов с выхода элемента 17. При этом на элементы 6 к 12 выдается сигнал разрещения, а на элемент 5 - сигнал запрета. Таким образом, введение первых 5, вторых 6 и третьего 12 элементов И, элементов 7 ИЛИ позволяет получать сигнатурные по каждому из п - выходов блока 1 параллельно во времени, а также при определении годности выпол нять одну операцию сравнения одной сигнатуры контролируемого логического блока с заданной в технической документации, что существенно повышает быстродействие устройства. Формула изобретения 1. Устройство для контроля логических бло ков, содержащее сигнатурный анализатор, соеди ненный выходом со входом блока индикации, генератор импульсов, соединенный входом с пе вым выходом блока управления, второй выход которого соединен с первым входом сигнатурного анализатора, третий выход - со входом |3адатчика тестов, соединенного выходами со Эподами контролируемого логического блока, регистры сдвига, первые и вторые выходы кото рых соединены с первыми и вторыми входами сумматора соответственно, отличающе, е с я тем, что, с целью повышения быстродействия устройства, в него введены первая и вторая группы элементов И по числу выходов контролируемого логического блока, элемент И, элементы ИЛИ, первые и вторые входы которых соединены с выходами соответствующих элементов И первой и второй групп элементов И, а выходы - с первыми входами регистров сдвига, первые входы элементов И первых и вторых групп соединены соответственно с четвертым и пятым выходами блока управления, второй выход которого соединен с вторыми входами регистров сдвига, а шестой вход блока управления соединен с первым входом элемента И, соединенного выходом со вторым входом сигнатурного анализатора, второй вход элемента И соединен с выходом генератора ивлпульсов и третьими входами регистров сдвига и сигнатурного анализатора, вторые входы соответствунидих элементов И второй группы соединены с вторыми входами соответствующих элементов И первой группы, а третьи входы сумматоров соединены с соответствующими выходами контролируемого логического блока, второй вход п-го сумматора соединен с третьим входом сигнатурного анализатора. 2. Устр(жство по п. 1, о т л и ч а ю щ ее с я тем, что блок управления содержит элемент ИЛИ, элемент И, первый и второй элементы задержки, счетшк, инвертор, первый и второй переключатели, первый, второй и третий триггеры, причем первый, второй, третий, четвертый и пятый блока управлеиия соединены с выходами первого элемента задержки, инвертора, элемента И, первым и вторым выходами первого триггера, выходом второго триггера соответственно, первый вход счетчика (Соединен с выходом второго триггера и первым входом первого триггера, выход - со вторым входом первого триггера, второй вход - со входами первого и второго элементов задержки и выходом элемента И, первый вход которого соеданен с первым выходом первого триггера и выходом инвертора, второй вход - с с выходом элемента ИЛИ, соединенного первым входом с выходом второго элемента задержки, вторым входом через третий триггер с выходами первого переключателя, выходы второго переключателя соединены со входами второго фиггера. Источники информации, принятые во внимание при экспертизе 1. Локализация неисправностей в микропроцессорных системах при помощи шестнадцатиричных ключевых кодов. - Электроника, 1977, N 5, с. 23-33. 2. Патент США № 3573751, кл. 340-172.5, 971 (прототип).

Авторы

Даты

1981-10-23—Публикация

1979-12-04—Подача