Изобретение относится к вычислительной технике и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении,

Целью изобретения является повышение надежности устройства.

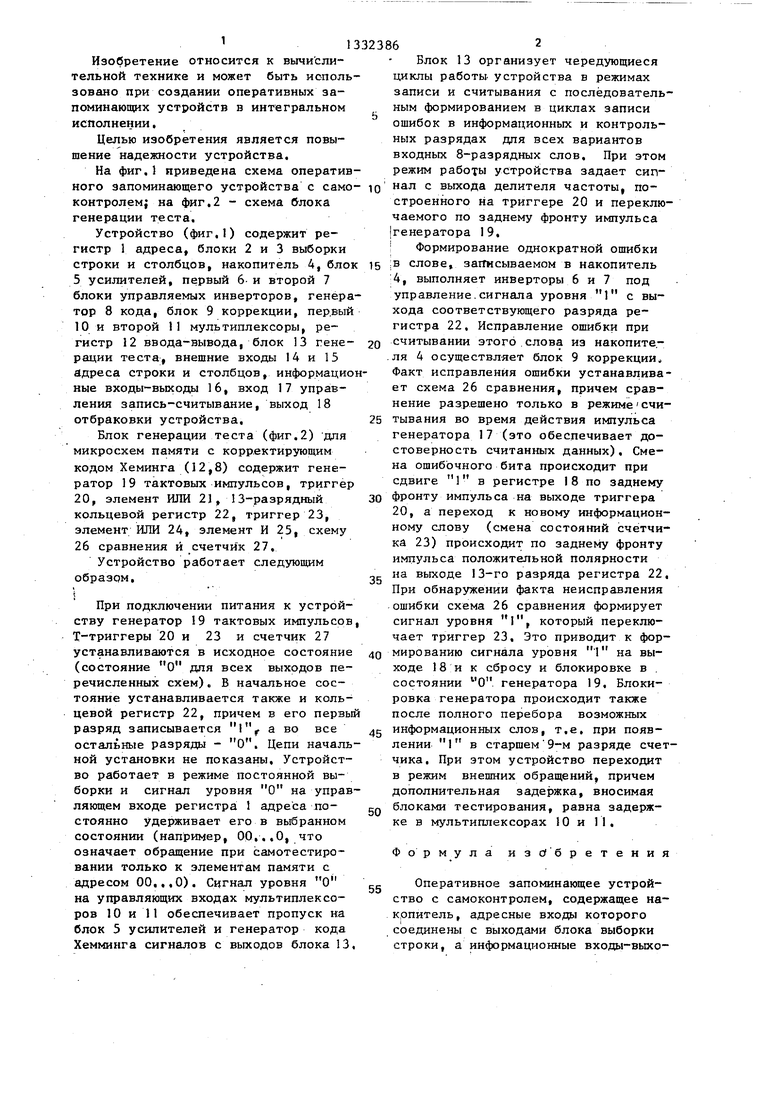

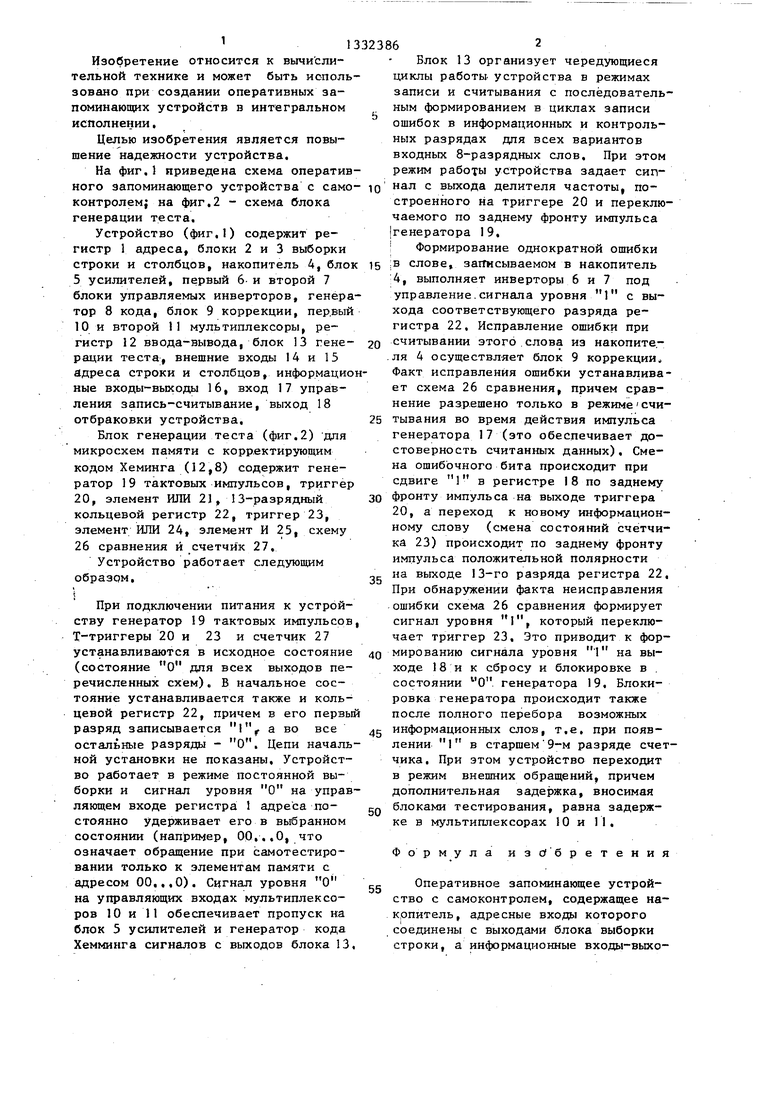

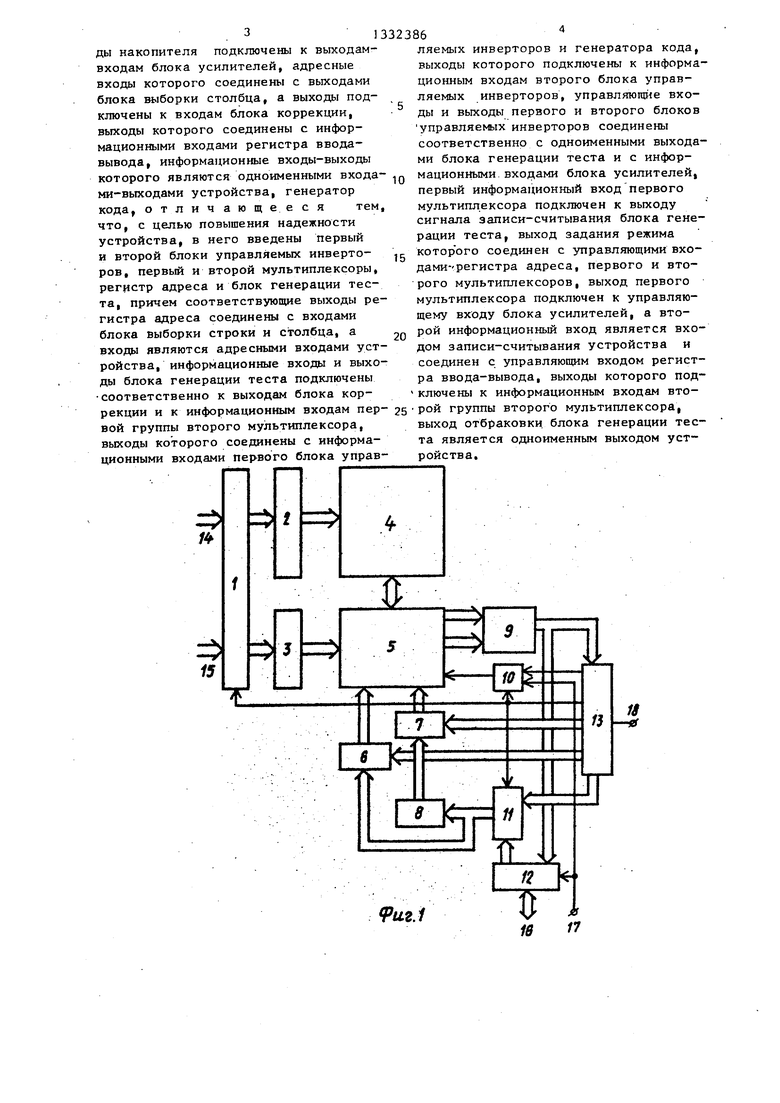

На фиг.1 приведена схема оперативного запоминающего устройства с само- ю выхода делителя частоты, по- контролем; на фиг,2 - схема блока строенного на триггере 20 и переклюБлок 13 организует чередующиеся циклы работы, устройства в режимах записи и считывания с последовательным формированием в циклах записи ошибок в информационных и контрольных разрядах для всех вариантов входных 8-разрядных слов. При этом режим работы устройства задает сил

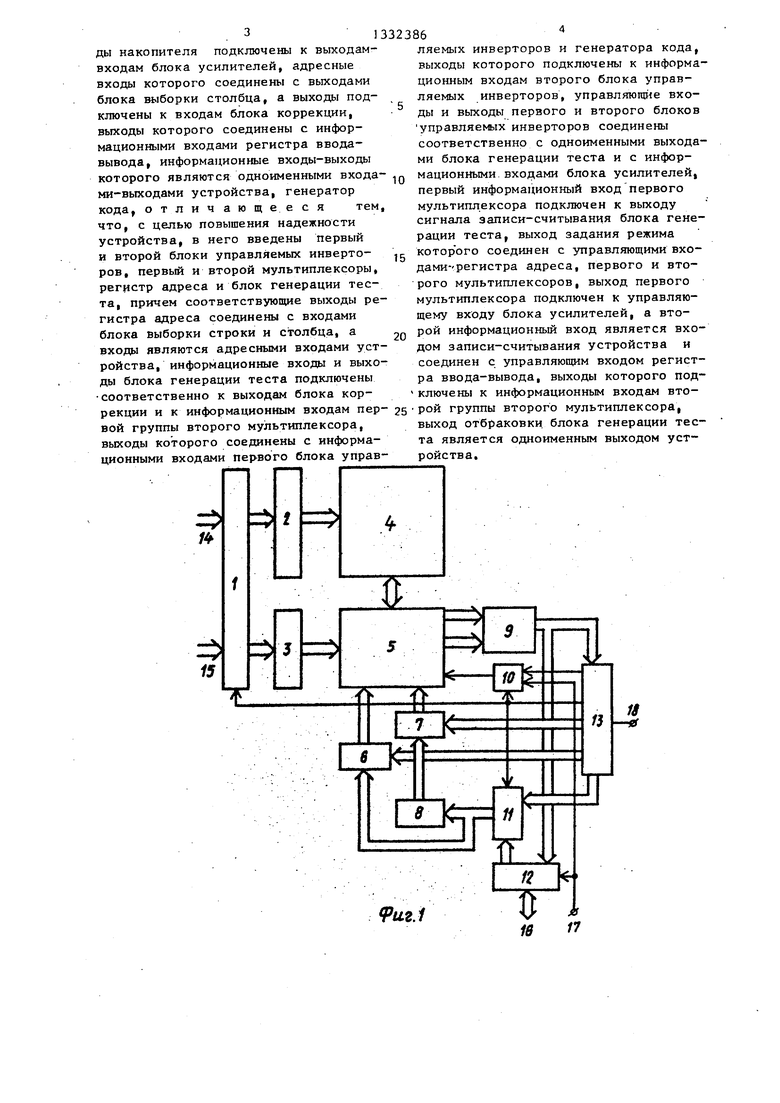

генерации теста,

Устройство (фиг,1) содержит регистр 1 адреса, блоки 2 и 3 выборки строки и столбцов, накопитель 4, блок 5 усилителей, первый 6-и второй 7 блоки управляемых инверторов, генератор 8 кода, блок 9 коррекции, первый 10 и второй 11 мультиплексоры, регистр 12 ввода-вывода, блок 13 генерации теста, внешние входы 14 и 15 адреса строки и столбцов, информационые входы-выходы 16, вход 17 управления запись-считывание, выход 18 отбраковки устройства.

Блок генерации теста (фиг,2) дгш микросхем памяти с корректирующим кодом Хеминга (12,8) содержит генератор 19 тактовых импульсов, триггер 20, элемент ИЛИ 21, 13-разрядный кольцевой регистр 22, триггер 23, элемент ИЛИ 24, элемент И 25, схему 26 сравнения и счетчи к 27,

Устройство работает следующим образом.

При подключении питания к устройству генератор 19 тактовых импульсов, Т-триггеры 20 и 23 и счетчик 27 устанавливаются в исходное состояние (состояние О для всех выходов перечисленных схем), В начальное состояние устанавливается также и кольцевой регистр 22, причем в его первый разряд записывается 1 а во все остальные разряды - О. Цепи начальной установки не показаны. Устройство работает в режиме постоянной выборки и сигнал уровня О на управляющем входе регистра 1 адреса постоянно Удерживает его в выбранном состоянии (например, 00,,,О, что означает обращение при самотестировании только к элементам памяти с адресом 00,,,0), Сигнал уровня О на управляющих входах мультиплексоров 10 и 11 обеспечивает пропуск на блок 5 усилителей и генератор кода Хемминга сигналов с выходов блока 13,

выхода делителя частоты, по- строенного на триггере 20 и переклюБлок 13 организует чередующиеся циклы работы, устройства в режимах записи и считывания с последовательным формированием в циклах записи ошибок в информационных и контрольных разрядах для всех вариантов входных 8-разрядных слов. При этом режим работы устройства задает сил

4, выполняет инверторы 6 и 7 управление.сигнала уровня

чаемого по заднему фронту импульса генератора 19,

Формирование однократной ощибки в слове, загТисываемом в накопитель

под

1 с выхода соответствующего разряда регистра 22, Исправление ошибки при считывании этого слова из накопите,- ля 4 осуществляет блок 9 коррекции Факт исправления ошибки устанавливает схема 26 сравнения, причем сравнение разрешено только в режиме счи- тывания во время действия импульса генератора 17 (это обеспечивает до0

5

0

0

стоверность считанных данных). Смена ошибочного бита происходит при сдвиге 1 в регистре 18 по заднему фронту импульса на выходе триггера 20, а переход к новому информационному слову (смена состояний счетчика 23) происходит по заднему фронту импульса положительной полярности иа выходе 13-го разряда регистра 22, При обнаружении факта неисправления ошибки схема 26 сравнения формирует сигнал уровня I, который переключает триггер 23, Это приводит к формированию сигнала уровня 1 на выходе 18 и к сбросу и блокировке в . состоянии О, генератора 19, Блокировка генератора происходит также после полного перебора возможных g информационных слов, т,е, при появлении 1 в старшем 9-м разряде счетчика. При этом устройство переходит в режим BHennftHX обращений, причем дополнительная задержка, вносимая блоками тестирования, равна задержке в мультиплексорах 10 и 1I,

Формула изс бретения

g Оперативное запоминающее устройство с самоконтролем, содержащее на- крпитель, адресные входы которого соединены с выходами блока выборки строки, а информационные входы-выхо.3

ды накопителя подключены к выходам- входам блока усилителей, адресные входы которого соединены с выходами блока выборки столбца, а выходы подключены к входам блока коррекции, выходы которого соединены с информационными входами регистра ввода- вывода, информационные входы-выходы которого являются одноименными входа ми-выходами устройства, генератор кода, отличающееся тем что, с целью повышения надежности устройства, в него введены первый и второй блоки управляемьк инверторов, первый и второй мультиплексоры, регистр адреса и блок генерации теста, причем соответствующие выходы ре гистра адреса соединены с входами блока выборки строки и столбца, а входы являются адресными входами уст ройства, информационные входы и выхо ды блока генерации теста подключены соответственно к выходам блока коррекции и к информационным входам пер вой группы второго мультиплексора, выходы которого соединены с информационными входами блока управ

10

32386

ляемых инверторов и генератора кода, выходы которого подключены к информационным входам второго блока управляемых инверторов, управляю1Щ{е входы и вькоды первого и второго блоков yпpaвляe ыx инверторов соединены соответственно с одноименными выходами блока генерации теста и с информационными . входами блока усилителей, первый информационный вход первого мультиплексора подключен к выходу сигнала записи-считывания блока генерации теста, выход задания режима которЪго соединен с управляющими входами-- регистра адреса, первого и второго мультиплексоров, выход первого мультиплексора подключен к управляющему входу блока усилителей, а вто2Q рой информационный вход является входом записи-считывания устройства и соединен с управляющим входом регистра ввода-вывода, выходы которого под- ключены к информационным входам вто25рой группы второго мультиплексора, выход отбраковки блока генерации теста является одноименным выходом устройства.

15

1в If

да в 7 О fr

V.

«г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1554030A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для сдвига | 1988 |

|

SU1587591A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

Изобретение относится к вычислительной технике и может быть использоваио при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель, регистр адреса, бЛ оки выборки строки и столбца, блок коррекции, генератор кода, первый и второй мультиплексоры, первый и второй блоки управляеьих инверторов, регистр ввода - вывода и блок генерации теста. В устройстве осуществляется тестовая проверка встроенных схем обнаружения и коррекции ошибок многоразрядных БИС запоминакщих устройств путем последовательной имитации одиночных ошибок для каждой кодовой комбинации информационных разрядов. 2 ил. г (Л

| Алексеенко Л.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| - М,: Радио и связь, 1982, с | |||

| Приспособление для картограмм | 1921 |

|

SU247A1 |

| Патент США № 4335459, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1987-08-23—Публикация

1986-03-31—Подача