2. Регулятор по п. 1, отлич ающи.й ся тем, что времени содержит элемент НЕ, первый элемент И и первый элемент задержки и последовательно соединенные пороговый элемент, первый RS-триггер, второй элемент И, второй RS-триггер, третий элемент И, второй элемент за,цержки и элемент ИЛИ, соединенный выходом с выходом реле времени, а вторым входом - с выходом первого элемента задержки, соединенного входом с выходом первого элемента и, соединенного первым входом с вторым выходом второго RS -триггера, а вторым входом - с выходом порогового элемента и с вторым входом третьего элемента И, подключенного выходом через элемент НЕ ко второму входу первого элемента И, R-вхбд второго RS-триггера соединен с R-входом первого КЗ-триггера и с вторым входом реле времени, соединенного первым входом с входом порогового элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный регулятор | 1983 |

|

SU1117585A1 |

| Импульсный регулятор | 1982 |

|

SU1105859A1 |

| Импульсный регулятор | 1984 |

|

SU1259209A1 |

| Импульсный регулятор | 1984 |

|

SU1238025A1 |

| Импульсно-релейный регулятор | 1984 |

|

SU1228072A1 |

| Частотно-импульсный регулятор | 1985 |

|

SU1278806A1 |

| Позиционный регулятор для систем с запаздыванием | 1987 |

|

SU1427328A1 |

| Позиционный регулятор для систем с запаздыванием | 1986 |

|

SU1416934A1 |

| Трехпозиционный регулятор | 1984 |

|

SU1259208A1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2011 |

|

RU2484547C1 |

1. ИМПУЛЬСНЫЙ РЕГУЛЯТОР, содержащий последовательно соединенные предварительный усилитель, интегратор, усилитель мощности, трех-позиционный релейный блок и реле времени, подключенное выходом к управляющему входу интегратора, (Отличающийся тем, что, с целью повышения динамической точности и йлстродействия регулято- ра, в нем установлены одновибратор и пороговый блок, соединённый входом с выходом предварительного усилителя, а выходом через одновибратор соединенный с вторым входом реле времени. (Л vj 00

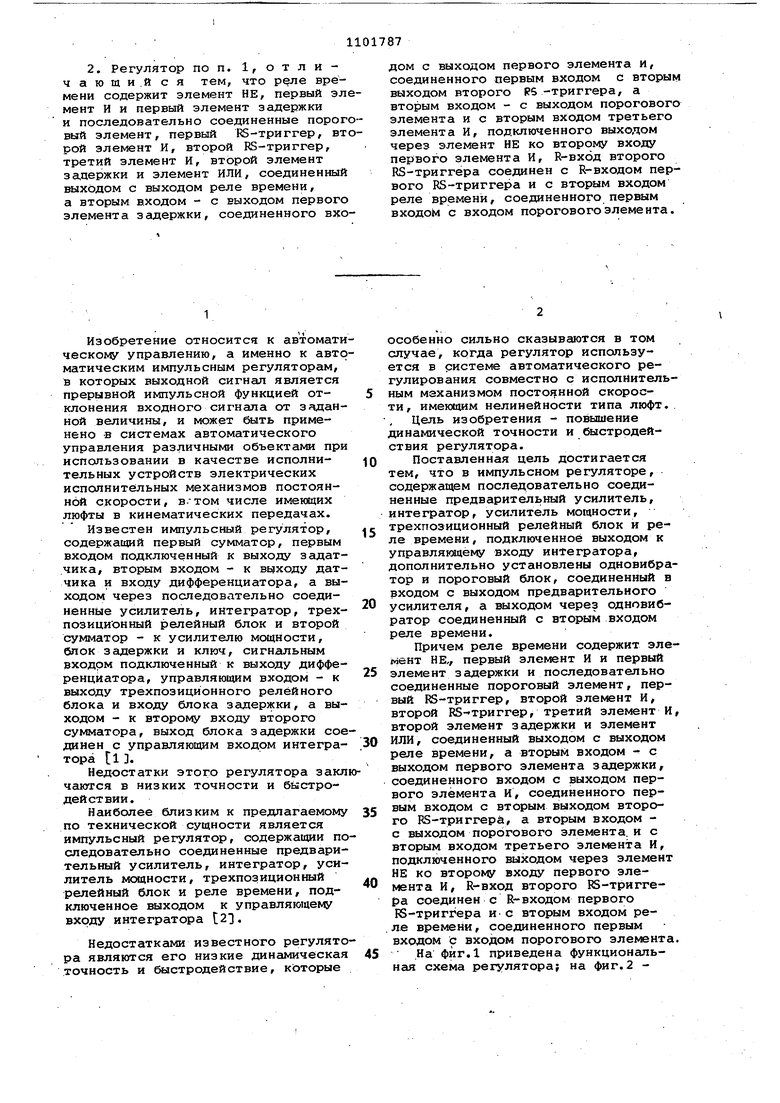

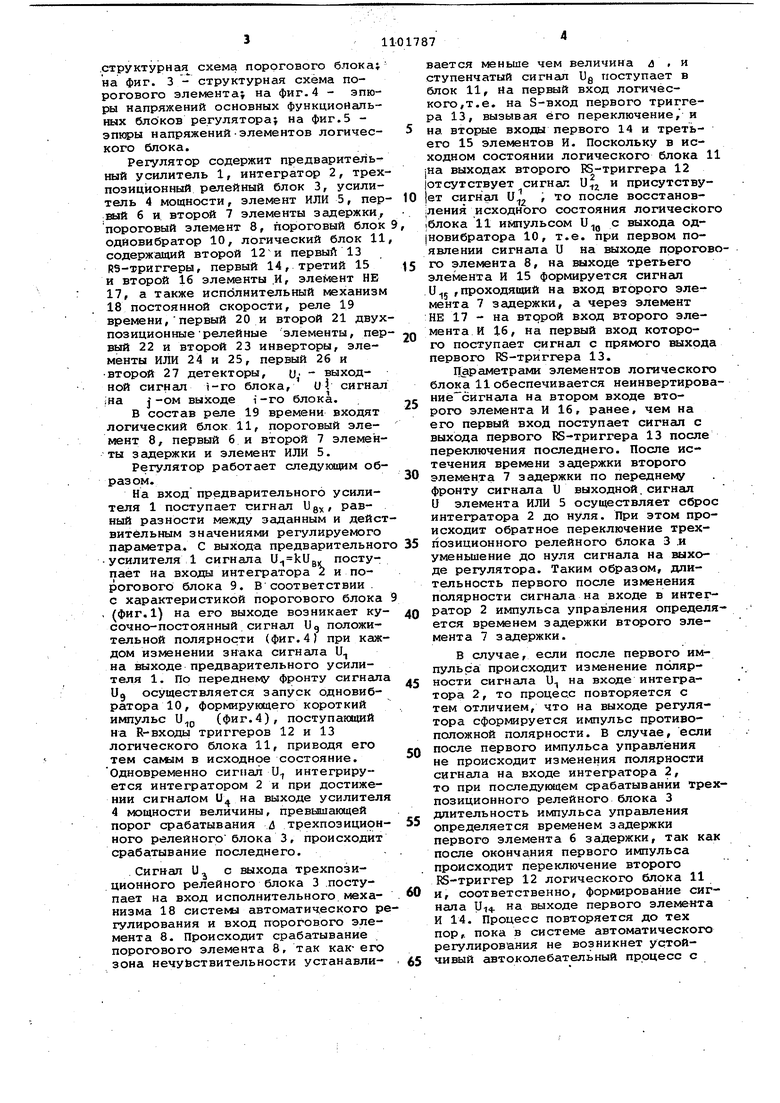

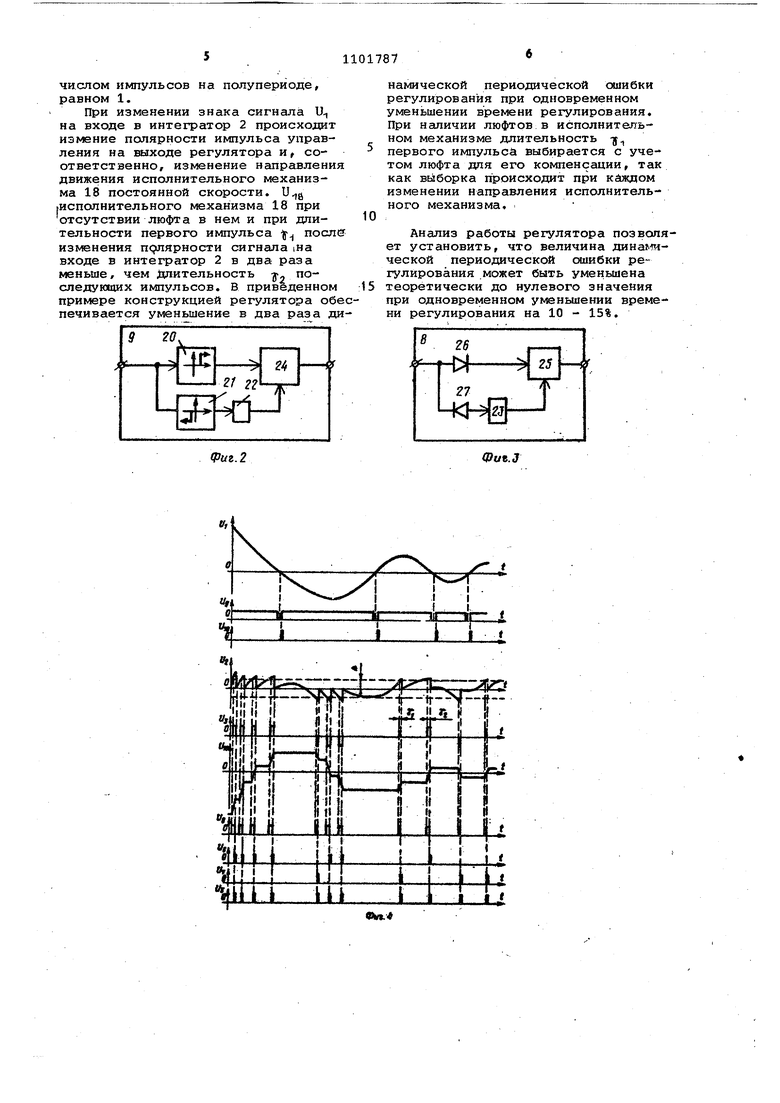

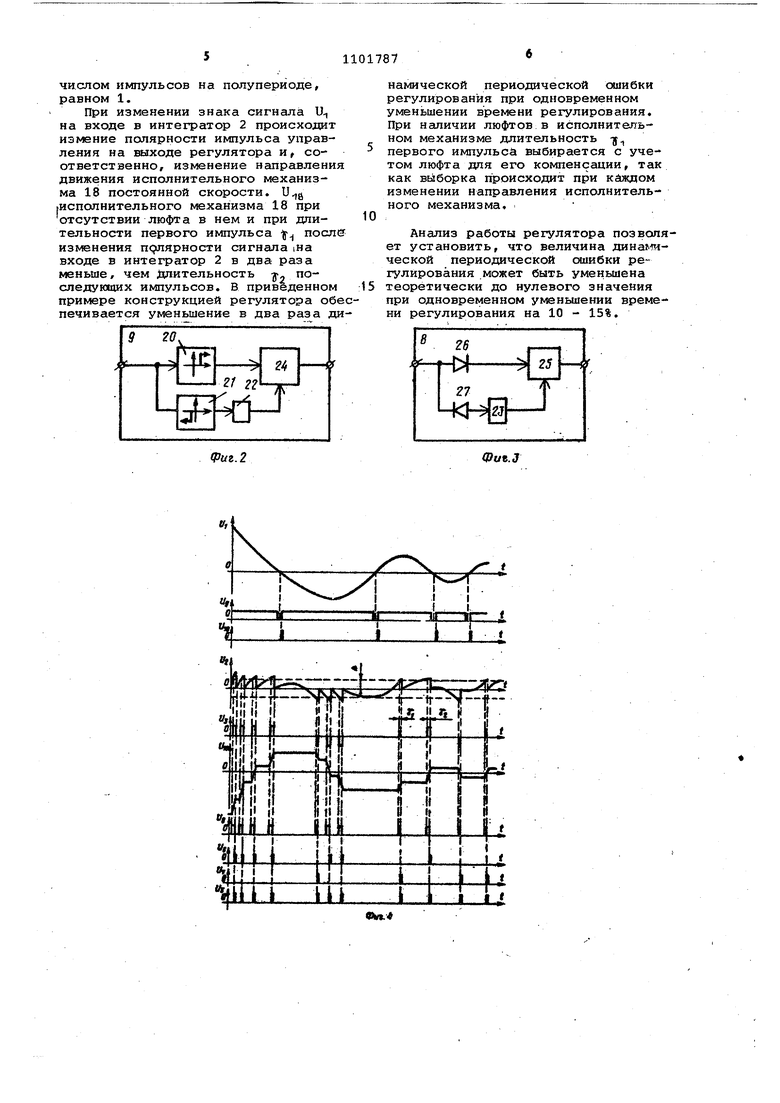

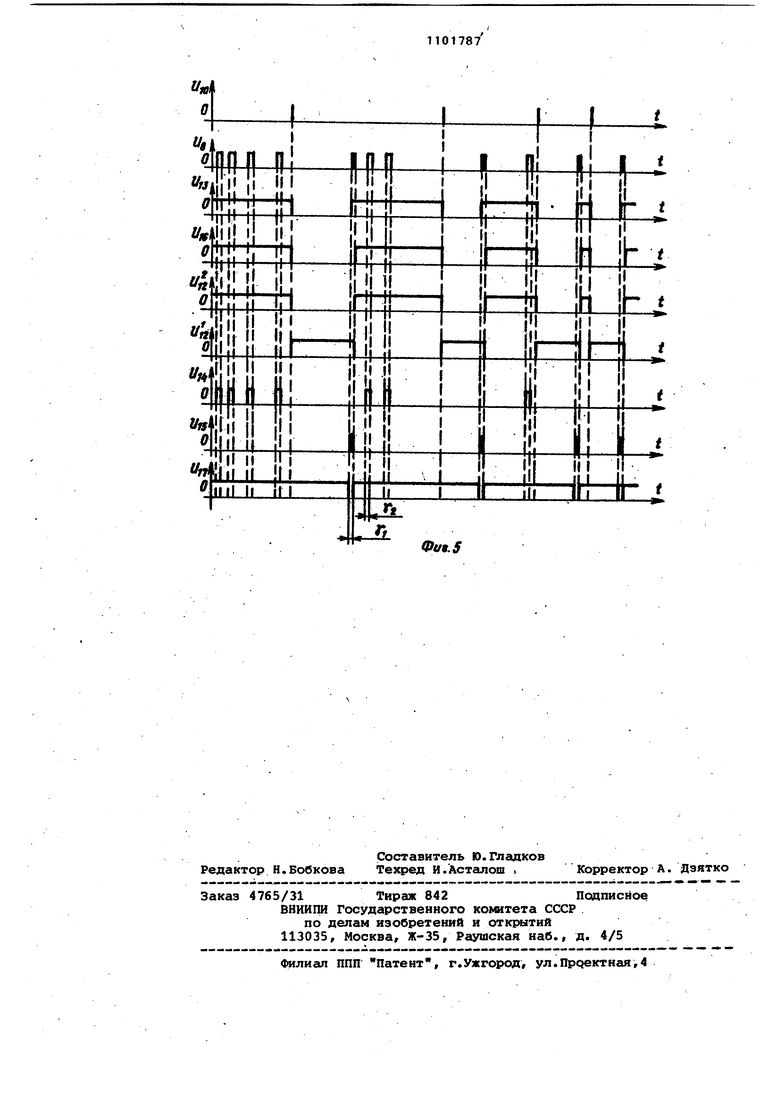

Изобретение относится к автомати ческому управлению, а именно к авто матическим импульсным регуляторам, в которых выходной сигнал является прерывной импульсной функцией отклонения входного сигнала от заданной величины, и может быть применено в системах автоматического управления различными объектами при использовании в качестве исполнительных устройств электрических исполнитбльных механизмов постоянной скорости. В-том числе имеющих люфты в кинематических передачах. Известен импульсный регулятор, содержащий первый сумматор, первым входом подключенный к выходу задатчика, вторым входом - к выходу датчика и входу дифференциатора, а выходом через последовательно соединенные усилитель, интегратор, трехпозиционный релейный блок и второй сумматор - к усилителю мощности, блок задержки и ключ, сигнальным входом подключенный к выходу дифференциатора, управляющим входом - к выходу трехпозиционного релейного блока и входу блока задержки, а выходом - к второму входу второго сумматора, выход блока задержки сое динен с управляющим входом интегратора 1 . Недостатки этого регулятора закл чаются в низких точности и быстродействии. Наиболее близким к предлагаемому по технической сущности является импульсный регулятор, содержащий по следовательно соединенные предварительный усилитель, интегратор, усилитель мощности, трехпозиционный релейный блок и реле времени, подключенное выходом к управляющего входу интегратора {2. Недостатками известного регулято ра являются его низкие динамическая точность и быстродействие, которые особенно сильно сказываются в том случае, когда регулятор используется в системе автоматического регулирования совместно с исполнительным механизмом постог нной скорости, имеющим нелинейности типа люфт. Цель изобретения - повышение динамической точности и быстродействия регулятора. Поставленная цель достигается тем, что в импульсном регуляторе, содержащем последовательно соединенные предварительный усилитель, интегратор, усилитель мощности, трехпозиционный релейный блок и реле времени, подключенное выходом к управлякяцему входу интегратора, дополнительно установлены одновибратор и пороговый блок, соединенный в входом с выходом предварительного усилителя, а выходом через одновибратор соединенный с вторым входом реле времени. Причем реле времени содержит элеотент НЕ,, первый элемент И и первый элемент задержки и последовательно соединенные пороговый элемент, первый RS-триггер, второй элемент И, второй RS-триггер, третий элемент И, второй элемент задержки и элемент ИЛИ, соединенный выходом с выходом реле времени, а вторым входом - с выходом первого элемента задержки, соединенного входом с выходом первого элемента И, соединенного первым входом с вторым выходом второго FS-триггера, а вторым входом с выходом порогового элемента, и с вторым входом третьего элемента И, подключенного выходом через элемент НЕ ко второму входу первого элемента И, R-вход второго RS-триггера соединен с R-входом первого PS-триггера и с вторым входом реле времени, соединенного первым входом с входом порогового элемента. На фиг.1 приведена функциональHcUit схема регулятора; на фиг. 2 .структурная схема порогового блока; на фиг. 3 - структурная схема порогового элeмeнтa на фиг.4 - эпюры напряжений основных функциональных блоков регулятораV на фиг.5 эпюры напряжений-элементов логического блока. Регулятор содержит предварительный усилитель 1, интегратор 2, трех поэиционный релейный блок 3, усилитель 4 мощности, элемент ИЛИ 5, пер вый б и второй 7 элементы задержки пороговый элемент 8, пороговый блок одйовибратор 10, логический блок 11 содержащий второй 12 и первый 13 RS-триггеры, первый 14, третий 15 и второй 16 элементы И, элемент НЕ 17, а также исполнительный механизм 18 постоянной скорости, реле 19 времени,первый 20 и второй 21 двух позиционныерелейные элементы, пер вый 22 и второй 23 инверторы, элементы ИЛИ 24 и 25, первый 26 и второй 27 детекторы, U - выходной сигнал i-ro блока, (1 сигнал на -ом выходе i -го блока. В состав реле 19 времени входят логический блок 11, пороговый элемент 8, первый б и второй 7 элементы задержки и элемент ИЛИ 5. Регулятор работает следукяцим образом. На вход предварительного усилителя 1 поступает сигнал UBK равный разности между заданным и дейст вительным значениями регулируемого параметра. С выхода предварительно -усилителя 1 сигнала поступает на входы интегратора 2 и порогового блока 9. В соответствии . с характеристикой порогового блока , (фиг.1) на его выходе возникает кусочно-постоянный сигнал Ug положительной полярности (фиг.4) при каждом изменении знака сигнала Ц на выходе предварительного усилителя 1. По переднему фронту сигнала Ug осуществляется запуск одновибратора 10, формирующего короткий импульс (фиг.4), поступающий на R-входы триггеров 12 и 13 логического блока 11, приводя его тем caNbiM в исходное состояние. Одновременно сигнал U интегрируется интегратором 2 и при достижении сигналом и на выходе усилителя 4 мощности величины, превышающей порог срабатывания /J трехпозиционного релейного блока 3, происходит срабатывание последнего. Сигнал Uj с выхода трехпозиционного релейного блока 3 поступает на вход исполнительного механизма 18 система автоматического ре гулирования и вход порогового элемента 8. Происходит срабатывание порогового элемента В, так как- его зона нечувствительности устанавливается меньше чем величина 4 . и ступенчатый сигнал UQ поступает в блок 11, йа первый вход логического,т.е. на S-вход первого триггера 13, вызывая его переключение, и на вторые входы первого 14 и третьего 15 элементов И. Поскольку в исходном состоянии логического блока 11 jHa выходах второго RS-триггера 12 отсутствует сигнал и присутствует сигнал и ТО после восстановления исходного состояния логического (блока 11 импульсом U с выхода од|новибратора 10, т.е. при первом появлении сигнала U на выходе порогового элемента 8, на выходе третьего элемента И 15 формируется сигнал ,проходящий на вход второго элемента 7 задержки, а через элемент НЕ 17 - на второй вход второго элемента И 16, на первый вход которого поступает сигнал с прямого выхода первого RS-триггера 13. Параметрами элементов логического блока 11 обеспечивается неинвертирование сигнапа на втором входе второго элемента И 16, ранее, чем на его первый вход поступает сигнал с выхода первого RS-триггера 13 после переключения последнего. После истечения времени задержки второго элемента 7 задержки по переднему фронту сигнала И выходной, сигнал и элемента ИЛИ 5 осуществляет сброс интегратора 2 до нуля. При этом происходит обратное переключение трехпозиционного релейного блока 3 .и уменьшение до нуля сигнала на выходе регулятора. Таким образом, длительность первого после изменения полярности сигнала на входе в интегратор 2 импульса управления определяется временем задержки второго элемента 7 задержки. В случае, если после первого импульса происходит изменение полярности сигнала U на входе интегратора 2, то процесс повторяется с тем отличием, что на выходе регулятора сформируется импульс противоположной полярности. В случае, если после первого импульса управления не происходит изменения полярности сигнала на входе интегратора 2, то при последукмцем срабатывании трех- позиционного релейного блока 3 длительность импульса управления определяется временем задержки первого элемента 6 задержки, так как после окончания первого импульса происходит переключение второго RS-триггер 12 логического блока 11 и, соответственно, формирование сигнала У-,4. на выходе первого элемента И 14. Процесс повторяется до тех пор,, пока в системе автоматического регулирования не возникнет устойчивый автоколебательный процесс с

числом импульсов на полупериоде, равном 1.

При изменении знака сигнала U-, на входе в интегратор 2 происходит измение полярности импульса управления на выходе регулятора и соответственно, изменение направления движения исполнительного механизма 18 постоянной скорости. .исполнительного механизма 18 при отсутствии люфта в нем и при длительности первого импульса послег изменения полярности сигнала |На входе в интегратор 2 в два раза меньше, чем щитeльнocть у- О следующих импульсов. В приведенном примере конструкцией регулятора обеспечивается уменьшение в два раза динамической периодической ошибки регулирования при одновременном уменьшении времени регулирования. При наличии люфтов в исполнительном механизме длительность -у первого импульса выбирается с учетом люфта для его компенсации, так как вьаборка происходит при каждом изменении направления исполнительного механизма.

Анализ работы регулятора позволяет установить, что величина динаг-ической периодической ошибки регулирования может быть уменьшена теоретически до нулевого значения при одновременном уменьшении времени регулирования на 10 - 15%.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Импульсный регулятор | 1981 |

|

SU1004969A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кунцевич В.М | |||

| и Чеховой tO.H | |||

| Нелинейные системы с частотно-импульсной модуляцией | |||

| Киев, Техника,1970, с.42-45 (прототип). | |||

Авторы

Даты

1984-07-07—Публикация

1982-10-29—Подача