Изобретение относится к измерительной технике и может быть использовано для идентификации звеньев систем автоматического регулирования.

, По основному авт. св. № 499557 известно устройство, содержащее источник входного сигнала, связанный с входами динамического звена и преобразователя входного сигнала, соединенные последовательно первый блок вычитания, первый ключ и первый интегратор, включенные последовательно второй ключ и второй интегратор, третий ключ и блок управления, соответствующие выходы которого соединены с управляющими входами источника входного сигнала и ключей, второй блок вычитания включен между выходом первого интегратора и входом второго ключа, третий блок вычитания - между выходом второго интегратора и входом третьего ключа, три цифровых делителя напряжения, причем вход первого из них связан с выходом преобразователя входного сигнала, а выход - с вычитающим входом первого блока вычитания, входы второго и третьего цифровых делителей напряжения соединены с выходом

преобразователя выходного сигнала, а их входы - соответственно с вычитающими входами второго и третьего блоков вычитания, блок управляющих импульсов, коммутатор и три реверсивных счетчика, входы которых подключены к соответствующим выходам коммутатора, а выходы соединены с управляющими входами цифровых делителей

10 напряжения, входы блока управляющих импульсов связаны со вторыми выходами всех ключей, а его выходы - с одним входом коммутатора, с другим входом которогосоединен выход бло15 ка управления fl.

Однако в известном устройстве статический коэффициент передачи звена определяется в одной точке ха20 рактеристики, т.е. при одном фиксиро. ванном значении входного сигнала, и в результате при идентификации звеньев с нелинейной статической характеристикой возникает значительная погрешность в определении всех парамет25ров .

Цель изобретения - повышение точности устройства.

Цель достигается тем, что в устройство для определения параметров

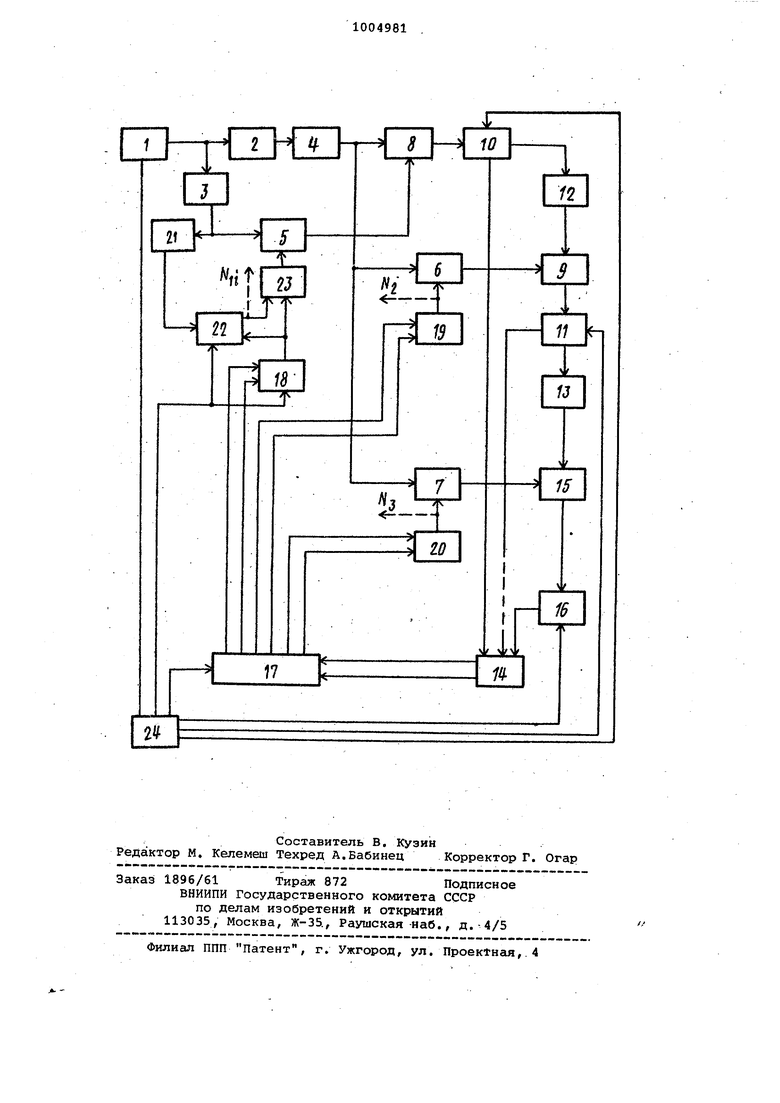

30 динамических звеньев систем автоматического регулирования дополнительно ввалены последовательно соединенные аналогоцифровой преобразователь, блок памяти, элемент ИЛИ, выход кот рого подключен 1{ управляющему входу первого цифрового делителя напряжения, а второй вход - к выходу перво зеверсизкого счетчика и к атерому входу блока памяти, третий вход которого соединен с третьим выходом блока управления и с установочным входом первого реверсивного счетчика, причем вход аналогоцифрового преобразователя подключен к выходу преобразователя входного сигнала. На чертеже приведена функциональ ная схема предложенного устройства. Устройство включает источник 1 входного сигнала, динамическое звено 2, преобразователь 3 входного си нала, преобразователь 4 выходного сигнала, первый цифровой делитель 5 напряжения, второй цифровой делитель 6 напряжения, третий делитель напряжения, первый блок 8 вычитания второй блок 9 вычитания, первый клю 10, второй ключ 11, первый интегратор 12, второй интегратор 13, блок управляющих импульсов, третий блок 15 вычитания, третий ключ 16, комму татор 17, первый реверсивный счетчик 18, второй реверсивный счетчик 1 третий реверсивный счетчик 2d, аналогоцифровой преобразователь 21, блок 22 памяти, элемент ИЛИ 23, бло 24 управления, . Устройство работает следующим об разом. Динамическое звено 2 описывается дифференциальным уравнением второго порядка + - у k(K}x, Где X и у. - входной и выходной сигналы динамического эвен а , а - постоянные параметры, подлежшдие определению; k(x) - нелинейная статическая характеристика динамического звена. Преобразователи 3 и 4 входного и выходного сигналов преобразуют си налы X и у в напряжения , . X. , W бьгц i где m и m,j - коэффициенты преобразования«В первом .такте производится кусочно-линейНая аппроксимация нелинейкой характеристики k(x). Для это го блок 24 управления вырабатывает сигнал, запускаюсций источник 1 вход ного сигнала, а также с помощью ключа 10 переключает выход блока 8 вычитания на вход блока 14 управляющих импульсов. Источник 1 входного сигнала вырабатывает сигнал X, например, ступен.чатой формы с такимиинтервалами, что переходный процесс в звене 2 успевает закончиться. Бло-к 14 усиливает сигнал рассогласования и в зависимости от его знац а выдает импульсы по одному из выходов, которые в первом такте через коммутатор 17 подключены к управлянвдим входам реверсивного счетчика 18. Счетчик 18 управляет коэффициентом передачи цифрового делителя 5 напряжения, В результате во время постоянства сигнала х- выполняется равенствоUBb,x(t.) К,,-(х.) 1 , 2 , , . . 1 , .время достижения установившегося значения выходным сигналом при х х. const; ( 1 - количество точек аппроксимации J К .(х.) - коэффициент передачи цифрового делителя 5 напряжения в момент времени t-- , определяемый выражением С, N,. где С. - постоянный коэффициент; ,-. - цифровой код в реверсивном счетчике 18 в момент времени . в момент времени ц цифровой код в счетчике 18 пропорционален-значению нелинейной статической характеристики звена 2 при х х И . т Одновременно аналогоцифровой преобразователь 21 преобразует, сигнал х в цифровой код, который поступает на адресный вход блока 22 памяти, В это же время сигнал от блока 24 управления, разрешает запись по данному адресу в блок 22 содержимого счетчика 18 Таким образом, после первого такта в блоке 22 памяти по соответствующим значениям х адресам записан массив значений k(), аппроксимирующих нелинейную статическую характеристику динамического звена 2, Во втором такте блок 24 управления переводит блок 22 памяти в режим считывания и по установочному входу сбрасыв.ает реверсивный счетчик 18 импульсов в нулевое состояние. Одновременно вырабатывается входной сигнал, выход блока .8 через ключ 10 подключается к выходу интегратора 12, а выход блока 9 через ключ 11 соединяется с выходом блока 14 управляющих импульсов, выхода которого переключаются на входы реверсивного счетчика 15 через кои№ татор 17.

При этом форма входного сигнала х можетбыть произвольной с условием, что через время t ty, выходной сигнал у примет установившееся значение При изменении входного сигнала х аналогоцифровой преобразователь 21 Вьфабатывает адресные коды, по которымиз блока 22-памяти считываются коды, соответствующие k(x), которые через логическую схему ИЛИ 23 поступают в цифровой делитель 5 напряжения.

Таким образом, моделируется нелинейная характеристика k(x) динамическо о эвена 2, интегратор 12 интегрирует разность сигналов (x)x , а его выходное напряжения равно , -t

U;,(t) « (

Через время t 7/. ty, производная у Ори при у(о)у (о) О . имеем

,).

Ь.)

Цепь управления коэффициентом передачи Kj цифрового делителя 6 напряжения отрабатывает равенство

1(и) .)

из (1) следует

а Na,

где Сд - постоянный коэффициент; M,j - код в счетчике 19 J

Т - прстоянная времени интегратора 12.

В третьем такте блок 24 управления переключает выход блока 9 через ключ 11 на вход интегратора 13, а выход блока 15 через ключ 16 соединяется с входом блока 14, выход коTopioro коммутируется на вход реверсивного счетчика 20 через коммутатор 17. Реверсивный счетчик 19 находится в режиме хранения кода, реверсивный счетчик 18 находится в нулевом состоянии, а дифровьвл делителем Б напряжения управляет блок 22 памяти.

Управление коэффициентом передачи К з цифрового делителя 7 напряжеНИН происходит до выполнения равенства .

SIJ«.,K)

)

где ( - выходное напряжение интегратора 13.

Следовательно,

о- Ъ где С, - постоянный коэффициент;

Т - постоянная.времени интегратора 13; - код в счетчике 20,

N,

Таким образом, после трех тактов параметры Зр и а линей-ной части передаточной функции динамического звена 2 определяются цифровыми кодами N и N в соответствующих реверсивных счетчиках. Параметры аппроксимации нелинейной статической характеристики определяются цифровыми кодами (i , ... t) в блоке 22 пампти.

Таким образом, предложенное устройство позволяет учесть нелинейнрсть статической характеристики динамического звена и за счет этого повысить точность определения всех его параметров.

Ф.ормула изобретения

Устройство для определения параметров динамических звеньев систем автоматического регулирования по авт. св. № 499557, отличающееся тем, что, с целью повышения точности, оно содержит последовательно соединенные ангшогоцифровой преобразователь, блок памяти, элемент ИЛИ, выход которого подключен к управляющему входу первого цифрри вого делителя напряжения, а второй вход - к выходу первого реверсивного счетчика и к второе входу блока

памяти, третий вход которого соединен с третьим выходом блока управления и с установочным входом первого реверсивного счетчика, причем вход аналогоцифрового преобразователя

подключен к выходу преобразователя входного сигнала.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

499557, кл. G 05 В 23/02, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения параметров динамических звеньев систем автоматического регулирования | 1974 |

|

SU499557A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Устройство для интегрирования электрического сигнала | 1982 |

|

SU1115066A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для функционального контроля систем управления | 1983 |

|

SU1145323A1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| Преобразователь угловых перемещений в код | 1978 |

|

SU926703A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-24—Подача