(54) АДАПТИРУЕМОЕ СУММИРУЮЩЕ-БЫЧИТАЮЩЕЕ УСТРОЙСТВО

1

Изобретение относится к вычислитЪльной технике и автоматике и может быть приме.нёйо для пост1$рения надежных арифметических узлов цифровой обработки информации,;

известны комбинационные суммирующе-вычитаияцие устройства, предназначенные для суммированиями вычитания двоичных чисел, представленных в прямых кодах, и состоящие из элементов равнозначности (.неравнозначности)и схем ЙС и 21.

Недост аткси«1 таких устройств явпяются их низкие функциональность ft надежность.

Известны устройства, обладающие рпособностью к адаптации. при- неисп «с равностях Сз1.

Однако эти способности либо ограничены, либо предполагают наличие резервного устройства, т. е. имеют большую сложность и/ как следствие, низкую надежность.

Наиболее близким к предлагаемому является суимирукице вычитаюадее устг ройство, которое состоит из че1тырех элементов равнозначности и элемента И и позволяет реализовать сложение и в 1читание прямых и инверсных кодов двоичных чисел С J.

Недостатком данного устройства является его низкая надежность при наличии любой неисправности устройство становится неработоспособным) и отсутствие полного разрешения Неисправностей элементов схемы, что затрудняет поиск и устранение возникших неисправностей.

Цель изобретения- - повышение дёжности суммируквде-вычитающего устройства путем введения избыточности в. его схему для обеспечения возмож-гности правильного функционирования устройства, при наличии любой логической неисправности любого элемента

15 схемы.

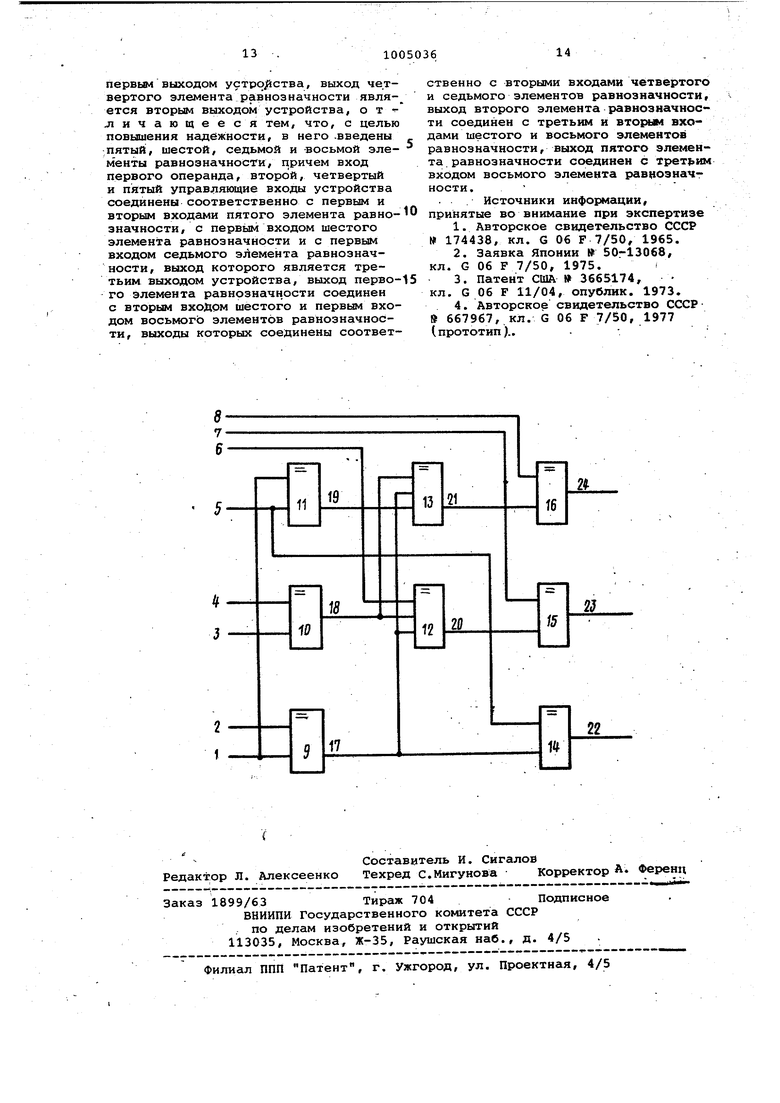

Поставленная цель достигается тем, что в адаптируемое суммирующе-вычитакйцее. устройство,. содержащее первый, второй, третий,четвертый элементы

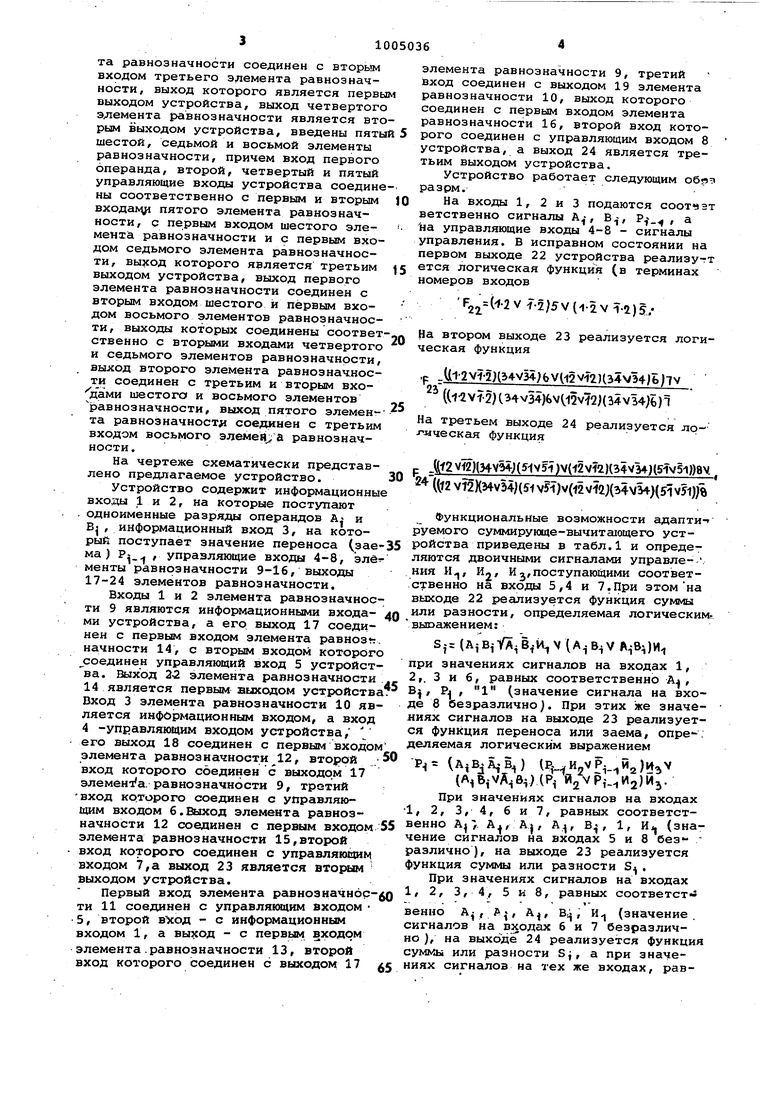

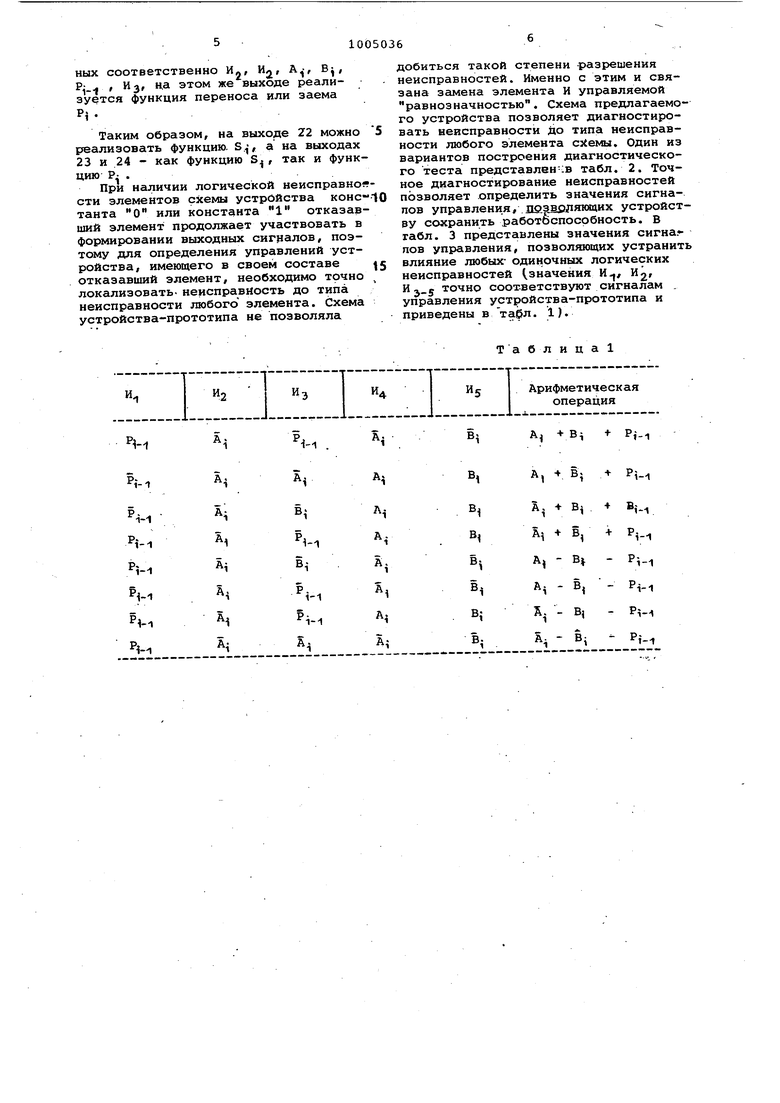

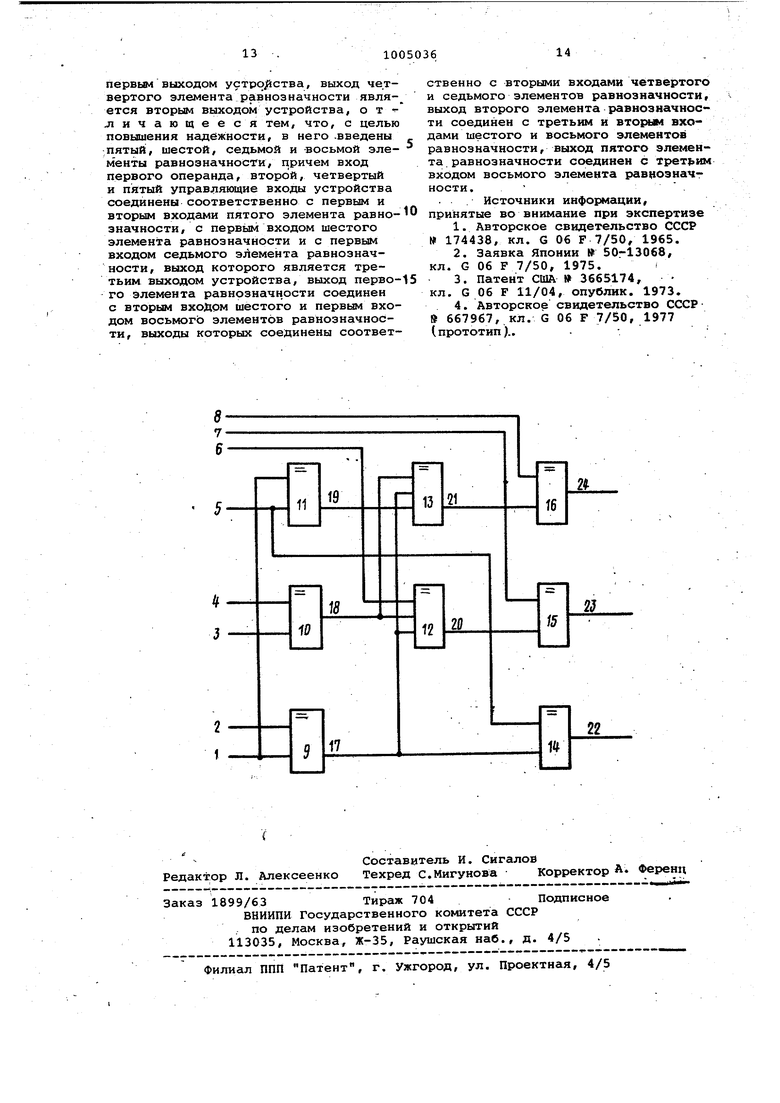

20 равнозначности, причем вход первого рлеранда, второго операндами переноса, первый, второй и .третий управля,(ощиё входы устройства соединены соот - ветственно с первым и.вторья входами первого элемента равнозначности, с первым и .вторым входами второго элемента равнозначности, с первым входом третьего элемента равнозначности и с первым ВХОДОМ четвертого элемента 0 равнозначности, выход первого элемента равнозначности соединен с вторым входом третьего элемента равнозначности, выход которого является первы выходом устройства, выход четвертого элемента равнозначности является вто рым выходом устройства, введены пяты шестой, седьмой и восьмой элементы равнозначности, причем вход первого операнда, второй, четвертый и пятый управляющие входы устройства соедине ны соответственно с первым и вторым входаку пятого элемента равнозначности, с первым входом шестого элемента равнозначности и с первым входом седьмого элемента равнозначности, выход которого является третьим выходом устройства, выход первого элемента равнозначности соединен с вторым входом шестого и первым входом восьмого элементов равнозначности, выходы которых соединены соответ ственно с вторыми входами четвертого и седьмого элементов равнозначности, выход второго элемента равнозначности соединен с третьим и вторым входами шестого и восьмого элементов равнозначности, выход пятого элемента равнозначностл соединен с третьим входом восьмого злемеа;а равнозначности. На чертеже схематически представлено предлагаемое устройство. Устройство содержит информационны входы 1 и 2, на которые поступают . одноименные разряды операндов А.- и В, информационный вход 3, на который поступает значение переноса (заема ) Р , управляющие входы 4-8/ элё менты равнозначности 9-16, выходы 17-24 элементов равнозначности. Входы 1 и 2 элемента равнозначности 9 являются информационными входами устройства, а его выход 17 соединен с первым входом элемента равноз ; начности 14, с вторым входом которого Jcoeдинeн управляющий вход 5 устройства. Выход 2-2 элемента равнозначности 14 является первым выходом устройства Вход 3 элемента равнозначности 10 является информационным входом, а вход 4 -управляющим входом устройства/ его выход 18 соединен с первым входом элемента равнозначности 12, второй . вход которого соединен с выходо.м 17 элемен1а. равнозначности 9, третий ВХОД которого соединен с управляющим входом 6.Выход элемента равнозначности 12 соединен с первым входом элемента равнозначности 15,второй вход которого соединен с управляющим входом 7,а выход 23 является вторым выходом устройства. Первый вход элемента равнозначности 11 соединен с управлякицим входом 5, второй - с информационным входом 1, а выход - с первьм входом элемента.равнозначности 13, второй вход которого соединен с выходом 17 элемента равнозначности 9, третий вход соединен с выходом 19 элемента равнозначности 10, выход которого соединен с первым входом элемента равнозначности 16, второй вход которого соединен с управляющим входом 8 устройства, а выход 24 является третьим выходом устройства. Устройство работает следующим обг)з разрм. На входы 1, 2 и 3 подаются соотчэт ветственно сигналы , В,-, Р , а lia управляющие входы 4-8 - сигналы управления. В исправном состоянии на первом выходе 22 устройства реализу-тт ется логическая функция (в терминах номеров входов F2( .2;5V(l-2Vi.i)5.На втором выходе 23 реализуется логическая функция ,р .Ul-2V -2KMV34;(V(i2V-i2)(34V34 b)7V (()feVt12v72;(34Vi4;fe)1 На третьем выходе 24 реализуется лр- «ческая функция Р .((f2 )(HVMJ( )V(-f2VfZK34V34)(STv51)av 2 ((2 Vt2X3 v54M5l v5T}v(l2V 2X34V34)( Функциональные возможности адапти- руемого суммирующе-вычитающего устройства приведены в табл.1 и определяются двоичными сигналами управлеВИЯ И, Hj/ ИJ,поступающими соответственно на входы 5,4 и 7.При этомна выходе 22 реализуется функция суммы или разности, определяемая логическим выпажением: SP (AjBiVA B Vt V ( при значениях сигналов на входах 1, 2,. 3 и 6, равных соответственно А , Bi, PJ , 1 (значение сигнала на входе 8 безразлично). При этих же значениях сигналов на выходе 23 реализуется функция переноса или заема, опре-: деляемая логическим выражением P (A|BjA B) )H3V (,.,. V PMHjJHj. При значениях сигналов на входах 1, 2, 3, 4, 6 и 7, равных соответственно Ал, AJ, А, , 1, Hj, (значение сигналов на входах 5 и 8 без различно), на выходе 23 реализуется функция суммы или разности S. При значениях сигналов на входах 1, 2, 3,4, 5 и 8, равных соответственно А, /i{, А|, В: , И (значение, сигналов на входах 6 и 7 безразлично ), на выходе 24 реализуется функция сумка или разности S,, а при значениях сигналов на тех же входах, равных соответственно Ил, 1Л, , В

И

н.а этом же выходе реалиР -.

3

зуется функция переноса или заема PIТаким образом, на выходе 22 можно реализовать функцию. S., а на выходах 23 и 24 - как функцию S, так и функцию Р .

При наличии логической неисправноясти элементов схемы устройства константа О или константа 1 отказавший элемент продолжает участвовать в формировании выходных сигналов, поэтому для определения управлений устройства, имеющего в своем составе отказавший элемент, необходимо точно локализовать- неисправность до типа неисправности любого элемента. Схема устройства-прототипа не позволяла

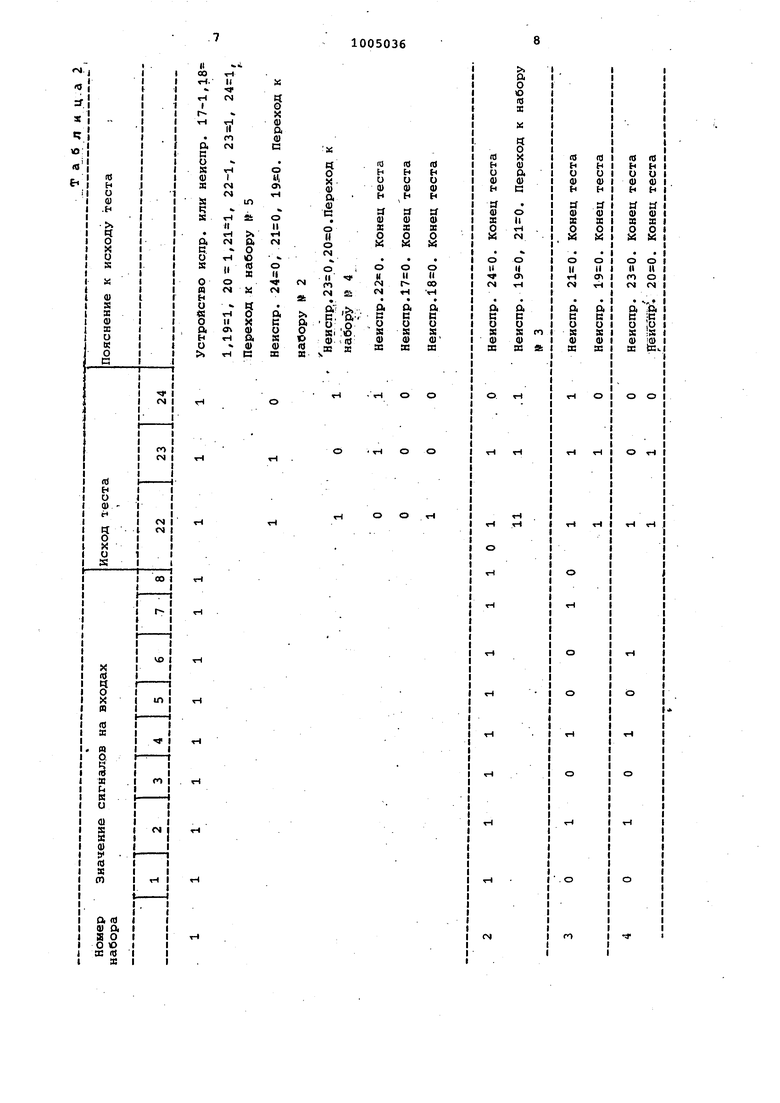

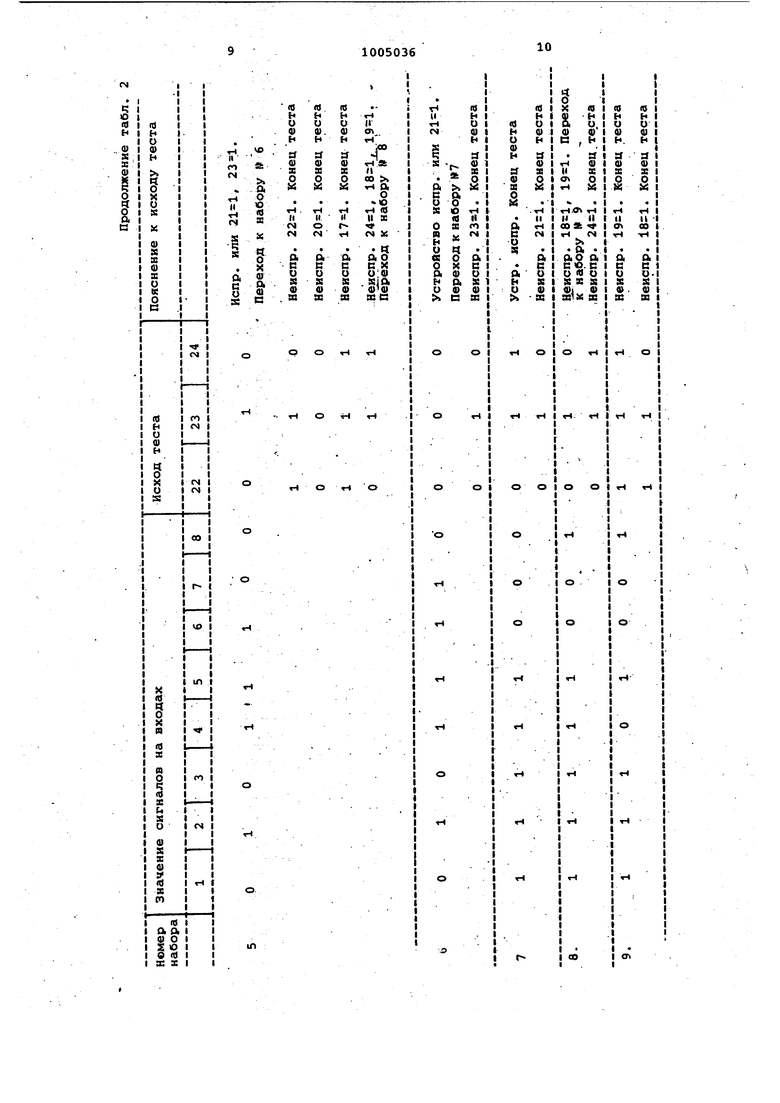

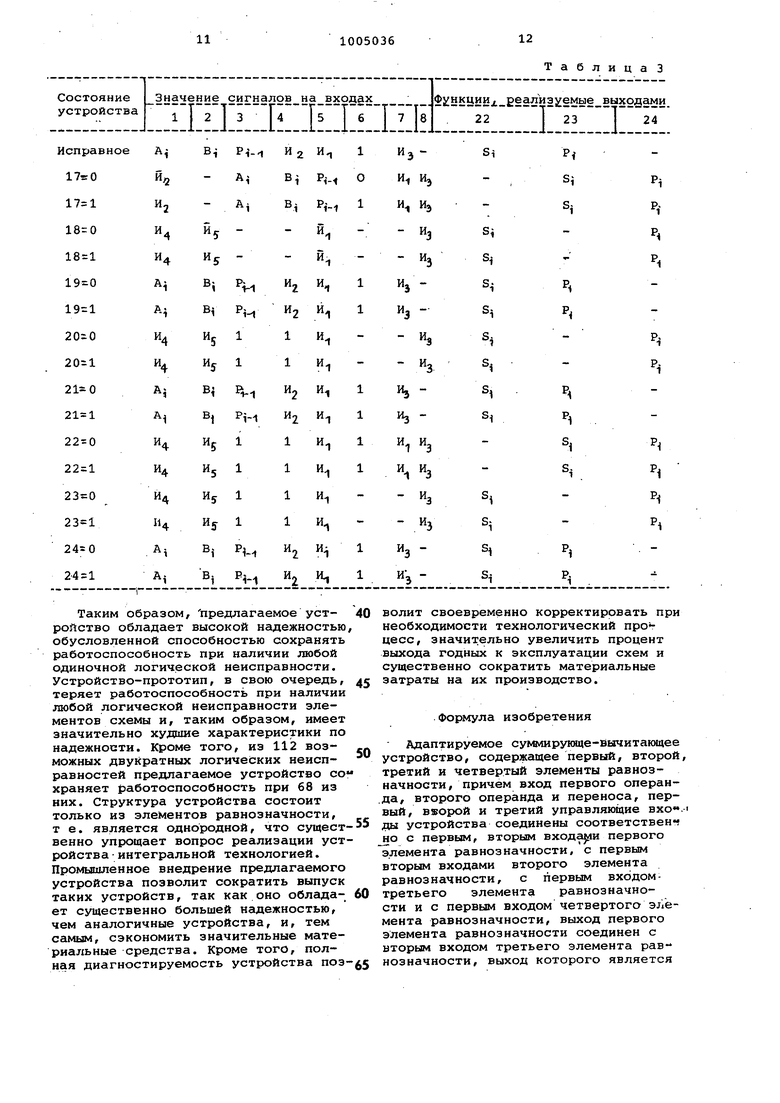

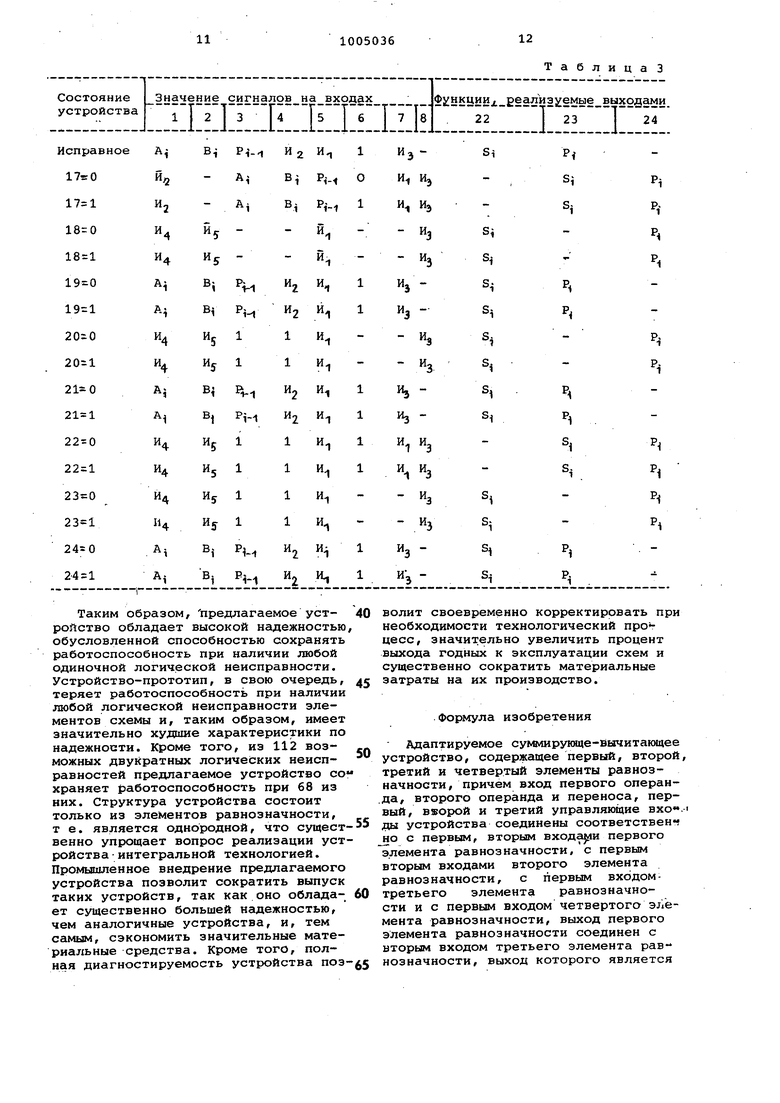

добиться такой степени -разрешения неисправностей. Именно с этим и связана замена элемента И управляемой равнозначностью. Схема предлагаемого устройства позволяет диагностировать неисправности До типа неисправности любого элемента схемы. Один из вариантов построения диагностического теста представленчв табл. 2. Точное диагностирование неисправностей позволяет определить значения сигналов управления, пйзвйляющих устройству сохранить работоспособность. В габл. 3 представлены значения сигна.пов управления, позволяющих устранит влияние любых- одиночных логических неисправностей значения И, И2, И точно соответствуют сигналам управления устройства-прототипа и приведены в табл. 1).

Таблица

ТаблицаЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Арифметико-логический модуль | 1983 |

|

SU1160395A1 |

| Управляемый арифметический модуль | 1978 |

|

SU840881A1 |

| Адаптируемое устройство для формирования сигнала переноса | 1984 |

|

SU1234829A1 |

| Отказоустойчивый многофункциональный логический модуль | 1981 |

|

SU1037255A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1980 |

|

SU922763A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Универсальный логический модуль | 1987 |

|

SU1476457A1 |

Таким образом, предлагаемое устройство обладает высокой надежностью обусловленной способностью сохранять работоспособность при наличии любой одиночной логической неисправности. Устройство-прототип, в свою очередь, теряет работоспособность при наличии любой логической неисправности элементов схемы и, таким образом, имеет значительно худшие характеристики по надежности. Кроме того, из 112 возможных двукратных логических неисправностей предлагаемое устройство со храняет работоспособность при 68 из них. Структура устройства состоит только из элементов равнозначности, т е. является однородной, что сущест венно упрощает вопрос реализации устройства интегральной технологией. Промышленное внедрение предлагаемого устройства позволит сократить выпуск таких устройств, так как оно обладает существенно большей надежностью, чем аналогичные устройства, и, тем самым, сэкономить значительные материальные средства. Кроме того, полная диагностируемость устройства позволит своевременно корректировать при необходимости технологический про цесс, значительно увеличить процент выхода годных к эксплуатации схем и существенно сократить материальные затраты на их производство.

Формула изобретения

Адаптируемое сумлирунмце-вычитающее устройство, содержащее первый, второй третий и четвертый элементы равнозначности , причем вход первого операн.да, второго операнда и переноса, первый, вжорой и третий управляющие вхо« ды устройства соединены соответствен но с первым, вторым входа ли первого элемента равнозначности, с первым вторым входами второго элемента равнозначности, с первым входомтретьего элемента равнозначности и с первым входом четвертого элемента равнозначности, выход первого элемента равнозначности соединен с вторым входом третьего элемента рав нозначности, выход которого является

первым выходом устро ства, выход четвертого элемента равнозначности является вторым выходом устройства, о т

.личающееся тем, что, с целью повышения надёжности, в него .введены

пятый, шестой, седьмой и -восьмой элементы равнозначности, причем вход первого операнда, второй, четвертый и пятый управляющие входы устройства соединены соответственно с первым и вторым входами пятого элемента равноэначности, с первым входом шестого элемента равнозначности и с первым входом седьмого элемента равнозначности, выход которого является третьим выходом устройства, выход перво го элемента равнозначн.ости соединен с вторым входом шестого и первым входом восьмого элементов равнозначности, выходы которых соединены соответ87- 6

19

t1

3

18

ID

2 1

17

ственно с вторыми входами четвертого и седьмого элементов равнозначности, выход второго элементаравнозначности соединен с третьим и вторьм входами шестого и восьмого элементов равнозначности, выход пятого элемента равнозначности соединен с третьим входом восьмого элемента равнозначности. .

Источники информации, принятые во внимание при экспертизе

кл. G 06 F 11/04, опублик. 1973.

2

21

13

t6

23

15

20

12

22

П

Авторы

Даты

1983-03-15—Публикация

1981-05-06—Подача