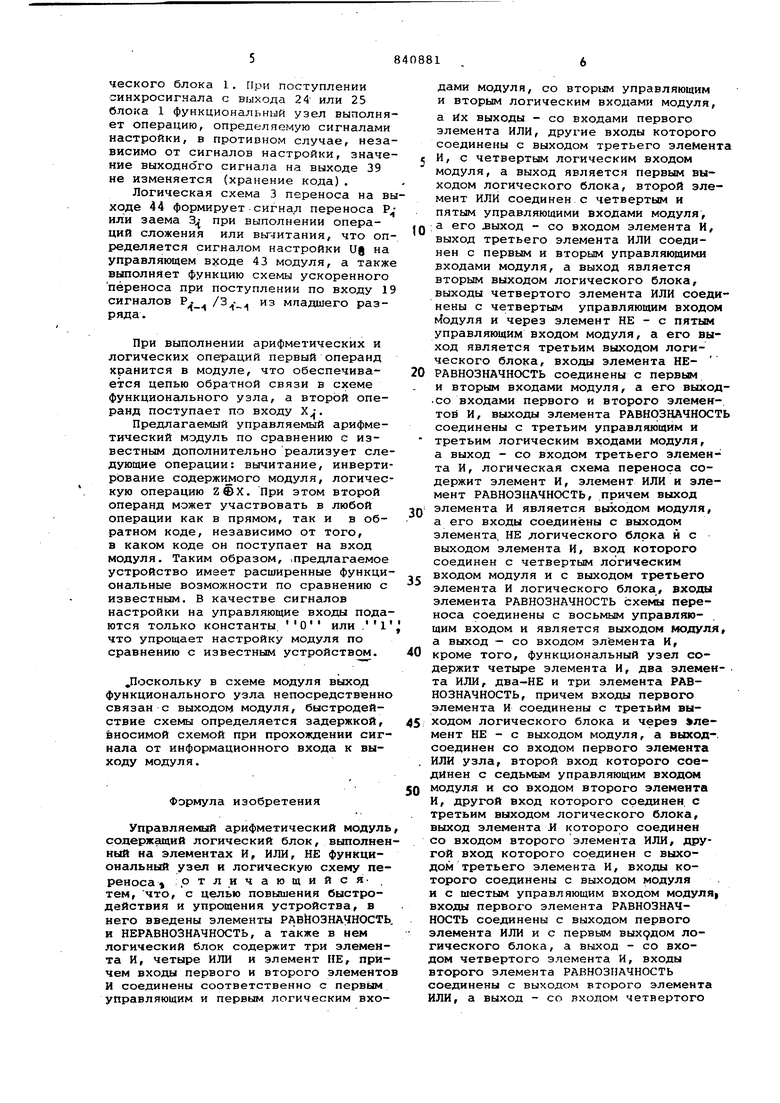

Изобретение относится к вычислительной технике и может использовать ся при построении различных узлов и устройств ЭВМ. Известны управляемые арифметические модули, реализующие функции: .логическое сложение, сдвиг вправо и влево, логическое умножение, арифметическое сложение, сложение по модулю два, прием прямых и обратных кодов, выдача содержимого модуля на выход 1. Недостатком известного модуля являются ограниченные функциональные возможности. Наиболее близким по технической сущности к предлагаемому являетря управляемый арифметический модуль, содержащий логический блок, функциональный узел и логическую схему переноса 2. Однако известный управляемый ариф метический модуль имеет ограниченные функциональные возможности,что ухудшает характеристики конструируемых н его основе узлов и устройств,а также недостаточно высокое быстродействие Цель изобретения - повышение быстродействия и упрощение устройства с одновременным расширением функциональных возможностей модуля. Поставленная цель достигается тем, что в управляемый -арифметический модуль, содержащий логический блок, выполненный на элементах Hj ИЛИ, НЕ, функциональный узел и логичес сую схему переноса, введены элементы РАВНОЗНАЧНОСТЬ и НЕРАВНОЗНАЧНОСТЬ, а также в нем логический блок содержит три элемента И,четыре ИЛИ и элемент НЕ,причем входы первого и второго элементов И. соединены соответственно с первым управляюп{им и первым логическим входами модуля,со вторым управляющим и вторым логическим входами модуля, а их выходы -, со входами первого элемента ИЛИ,другие входы которого соединены с выходом третьего элемента И, с четвертым логическим входом модуля, а вых.од является первым выходом логического блока,второй элемент ИЛИ соединен с четвертым и пятым управляющими входами модуля, а его выход со входом третьего элемента И, выход третьего элемента ИЛИ соединен с первым и вторым управляющими входами модуля, а выход является вторым выходом логического блока, выходь четвертого элемента ИЛИ соединены с четвертым управляющим входом модуля и через элемент НЕ - с пятым управля ющим входом модуля, а его выход является третьим выходом логического блока, входы элемента НЕРАВНОЗНАЧНОСТЬ соединены с первым и вторым входами модуля, а его выход - со вхо дами первого и второго элементов И, выходы элемента РАВНОЗНАЧНОСТЬ соединены с третьим управляющим й треть им логическим входами модуля, а выхо со входом третьего элемента И, логическая схема переноса содержит элеме И, элемент ИЛИ, элемент РАВНОЗНАЧНОС причем выход элемента И является выходом модуля, а его входы соединены с выходом элемента НЕ ло1 ического блока и с выходом элемента И, вход которого соединен с четвертым логическим входом модуля и с выходом третьего элемента И логического бло ка, входы элемента РАВНОЗНАЧНОСТЬ схемы переноса соединены с восьмым управляющим входом и является выхрходом модуля, а выход- со входом элемента И, кроме того, функциональ ный узел содержит четыре элемента И два ИЛИ, два - НЕ и три элемента РАВНОЗНАЧНОСТЬ, причем входы первого элемента И соединены с третьим выходом логического блока и череэ элемент НЕ - с выходом модуля, а вы ход соединен со входом первого элемента ИЛИ узла, второй вход кото рого соединен с седьмым управляющим входом модуля и со входом второго элемента И, другой вход которого соединен с третьим выходом логического блока, выход элемента И которого соединен со входом второго элемента ИЛИ, другой вход которого соединен с выходом третьего элемент И, входы которого соединены с выходом модуля и с шестым управляющим входом модуля, входы первого элемен РАВНОЗНАЧНОСТЬ соединены с выходом первого элемента ИЛИ и с первым выходом логического блока, а выход со входом четвертого элемента И, вх ды второго элемента РАВНОЗНАЧНОСТЬ соединены с выходом модуля и с выходом второго элемента ИЛИ, а выход со входсм четвертого элемента И, третий вход которого соединен со вторым выходом логического блока, а выход - со входом третьего элемен РАВНОЗНАЧНОСТЬ, другой вход которог через элемент НЕ соединен с выходом модуля. На чертеже представлена структур ная схема предлагаемого управляемог арифметического модуля. Он содержит логический блок i, функциональный блок 2 и логическую схему 3 переноса, причем логический блок 1 содержит три элемента И 4, 5 и 6, четыре элемента ИЛИ 7, 8, 9 и 10, два элемента РАВНОЗНАЧНОСТЬ, 11 и 12 и элемент НК 13. Управляющие входы 14-18 модуля подключены ко входам элементов следующим образом: вход 14 - к элементам 6, 9 и 12, вход 16 - к элементу 11, вход 17 к элементам 7 и 8, вход 18 - к элементам 7 и 13. Логические входы 1922 модуля подключены ко входам элементов следующим образом: вход 19 к элементу ИЛИ 10-, вход 20 - к элементу РАВЕ ОЗНАЧНОСТЬ, вход 21 - к элементу И 5, вход 22 - к элементу и б; выход элемента ИЛИ 10 является выходом 23 логического блока 1, выход элемента 8 - выходом 24, а выход элемента 9 - выходом 25 логического блока. Функциональный узел 2 содержит четыре элемента И 26, 27, 28 и 29, два элемента ИЛИ 30 и 31, три элемента РАВНОЗНАЧНОСТЬ 32, 33 и 34 и два элемента НЕ 35 и 36. Управляющие входы 37 и.38 модуля подключены соответственно ко входам элементов 28,30 и 27 узла. Выход элемента 34 РАВНОЗНАЧНОСТЬ является выходом 39 модуля и соединен со входами элемен тов 28 и 33 и с логической схемой переноса, а через элементы НЕ 35 и 36 - со входами элементов 26 и 34. Логическая схема 3 переноса содержит элемент ИЛИ 40, элемент РАВНОЗНАЧНОСТЬ 41 и элемент И 42. Входы элемента 42 подключены к выходу элемента НЕ 13 логического блока 1 и к выходам элементов 40 и 41. Входы элементов 40 и 41 соединены соответственно: вход элемента 40 соединен с логическим входом 19 модуля и с выkoдoм элемента И 4 блока 1; вход 41 - с управляющим входом 43 модуля и с выходом 39 модуля. Выход элемента И 42 является выходом 44 модуля. Арифметический модуль работает следующим обраэом. На логические входы 19-22 подаются соответственно сигналы переноса или, заема Р или 3,« из младшего (аэряда, сигнал кода Х операнда X или записываемого числа , сигнал S с выхода старшего разряда для сдвигов вправо, сигнал S ..| с выхода мпадаего разряда для сдвигов влево. Сигнсшы UV , Ujt и и на управляющих входах 14, 15 и 18 модуля коммутируют сигнёшы на логических входах 1922, управляющий сигнал U на входе 16 обеспечивает инвертирование входных кодов Х или Z , На управляющий вход 17 модуля подается синхросигнал} Ujf, , который обеспечивает срабатывание схемы модуля при выполнении любой, из функций. .Функциональный узел реализует выполнение требуемой операции и хранение результата операции. Нэстройка узла на выполнение требуемой функции производится сигналами и и U-y с управляющих входов 37 и 38 модуля, а также сигналом с выхода 25 логического блока 1. При поступлении синхросигнала с выхода 24 или 25 блока 1 функциональный узел выполня ет операцию, определяемую сигналами настройки, в противном случае, неза висимо от сигналов настройки, значе ние выходного сигнала на выходе 39 не изменяется (хранение кода). Логическая схема 3 переноса на в ходе 44 формирует сигнал переноса Р или заема 3 при выполнении операций сложения или вычитания, что оп ределяется сигналом настройки U§ на управляющем вз{оде 43 модуля, а также выполняет функцию схемы ускоренного переноса при поступлении по входу 1 сигналов Р 3 мпадшего разряда. При выполнении арифметических и логических операций первый операнд хранится в модуле, что обеспечивается цепью обратной связи в схеме функционального узла, а второй операнд поступает по входу . Предлагаемый управляемый арифметический модуль по сравнению с известным дополнительно реализует сле дующие операции: вычитание, инверти рование содержи мого модуля, логичес кую операцию Z®X. При этом второй операнд может участвовать в любой операции как в прямом, так и в обратном коде, независимо от того, в каком коде он поступает на вход модуля. Таким образом, .предлагаемое устройство имеет расширенные функциональные возможности по сравнению с известным. В качестве сигналов настройки на управляющие входы подаются только константы О или . что упрощает настройку модуля по сравнению с известным устройством. .Поскольку в схеме модуля выход функционального узла непосредственно связан с выходом модуля, быстродействие схемы определяется задержкой, вносимой схемой при прохождении сигнала от информационного входа к выходу модуля. Формула изобретения Управляемый арифметический модуль содержащий логический блок, выполнен ный на элементах И, ИЛИ, НЕ функциональный узел и логическую схему переноса 4 : о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия и упрощения устройства, в него введены элементы РАВНОЗНАЧНОСТЬ и НЕРАВНОЗНАЧНОСТЬ, а также в нем логический блок содержит три элемента И, четыре ИЛИ и элемент НЕ, причем входы первого и второго элементо И соединены соответственно с первым управляющим и первым логическим входами модуля, со вторым управляющим и вторым логическим входами модуля, а Их выходы - со входами первого элемента ИЛИ, другие входы которого соединены с выходом третьего элемента И, с четвертым логическим входом модуля, а выход является первым выходом логического блока, второй элемент ИЛИ соединен с четвертым и пятым управляющими входами модуля, ;а его ыход - со входом элемента И, выход третьего элемента ИЛИ соединен с первым и вторым управляющими входами модуля, а выход является вторым выходом логического блока, выходы четвертого элемента ИЛИ соединены с четвертым управляющим входом foдyля и через элемент НЕ - с пятым управляющим входом модуля, а его выход является третьим выходом логического блока, входы элемента НЕРАВНОЗНАЧНОСТЬ соединены с первым и вторым входами модуля, а его выходсо входами первого и второго элементов И, выходы элемента РАВНОЗНАЧНОСТЬ соединены с третьим управляющим и третьим логическим входами модуля, а выход - со входом третьего элемента И, логическая схема переноса содержит элемент И, элемент ИЛИ и элемент РАВНОЗНАЧНОСТЬ, причем выход элемента И является выходом модуля, а его входы соединены с выходом элемента. НЕ логического блока и с выходом элемента И, вход которого соединен с четвертым логическим входом модуля и с выходом третьего элемента И логического блока, входы элемента РАВНОЗНАЧНОСТЬ cxe№j переноса соединены с восьмым управляющим входом и является выходом модуля, а выход - со входом элемента И, кроме того, функциональный уэел содержит четыре элемента И, два элемен-. та ИЛИ, два-НЕ и три элемента РАВНОЗНАЧНОСТЬ, причем входы первого элемента И соединены с третьим выходом логического блока и через лемент НЕ - с выходом модуля, а выход-, соединен со входом первого элемента ИЛИ узла, второй вход которого соединен с седьмым управляющим входом модуля и со входом второго элемента И, другой вход которого соединен с третьим выходом логического блока, выход элемента И которог;о соединен со входом второго элемента ИЛИ, другой вход которого соединен с выходом третьего элемента И, входы которого соединены с выходом модуля и с шестым управляющим входом модулЯ| входы первого элемента РАВНОЗНАЧНОСТЬ соединены с выходом первого элемента ИЛИ и с первым вых9Дом логического блока, а выход - со входом четвертого элемента И, входы второго элемента РАВНОЗНАЧНОСТЬ соединены с выходом второго элемента ИЛИ, а выход - со входом четвертого

элемента И, третир вход которого соединен со вторым выходом логического блока, а выход - со входом,третьего элемента РАВНОЗНАЧНОСТЬ, другой вход которого через элемент НЕ соединен с выходом модуля.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 265565, кл. G 06 F 7/00, 1968.

2.Авторское свидетельство СССР 487387, кл G 06 F 7/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Арифметическое устройство | 1989 |

|

SU1635172A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Управляемый арифметический модуль | 1979 |

|

SU855654A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

Авторы

Даты

1981-06-23—Публикация

1978-05-22—Подача