1

Изобретение относится к автоматике и вичислительной технике и может быть использовано при разработке надежных суммирующих узлов обработки цифровой информации.

Цель изобретения - упрощение устройства.

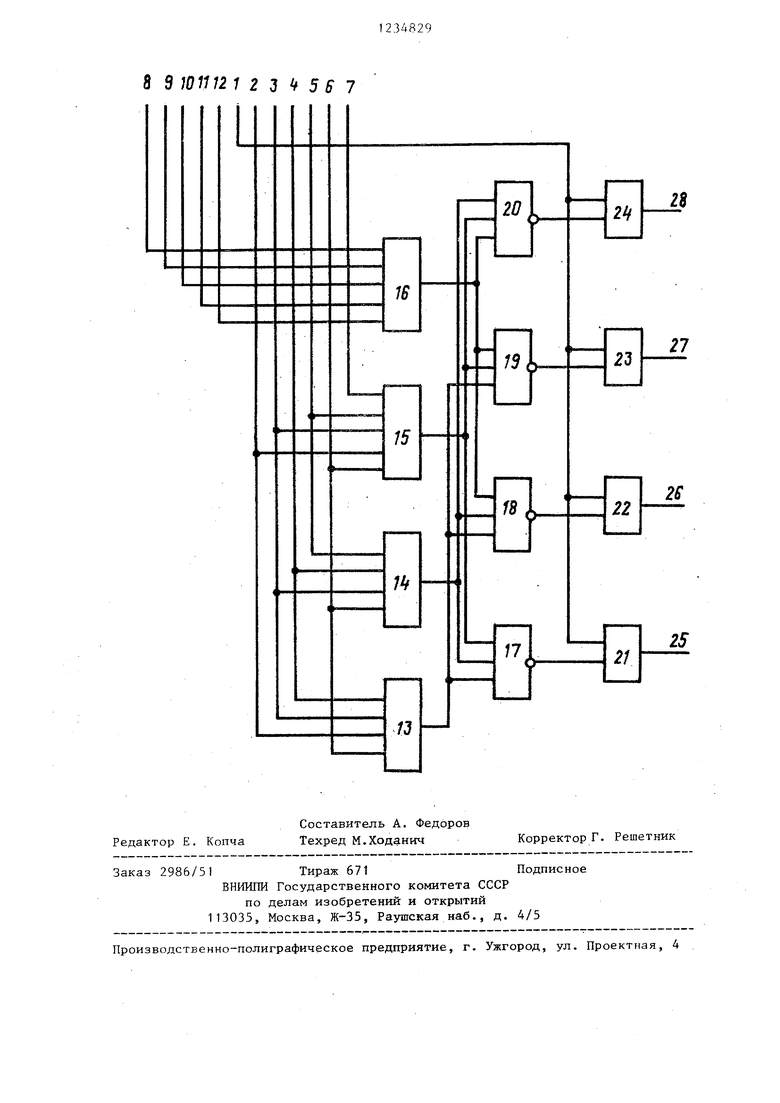

На чертеже изображена функциональная схема адаптируемого устройства для формирования сигнала переноса.

Устройство содержит информационные входы 1-7, управляющие входы 8-12 элементы 13-16 равнозначности, элементы 17-20 И-НЕ, элементы 21-24 равнозначности, выходы 25-28.

Р;, R(x, (R(x,,x.,,x,x) и R(x,,x,, x4,X5) AR(x, ,Х2 ,х,. ,х ,х))) ,

снимается значение сигнала переноса в следующий четвертичный разряд.

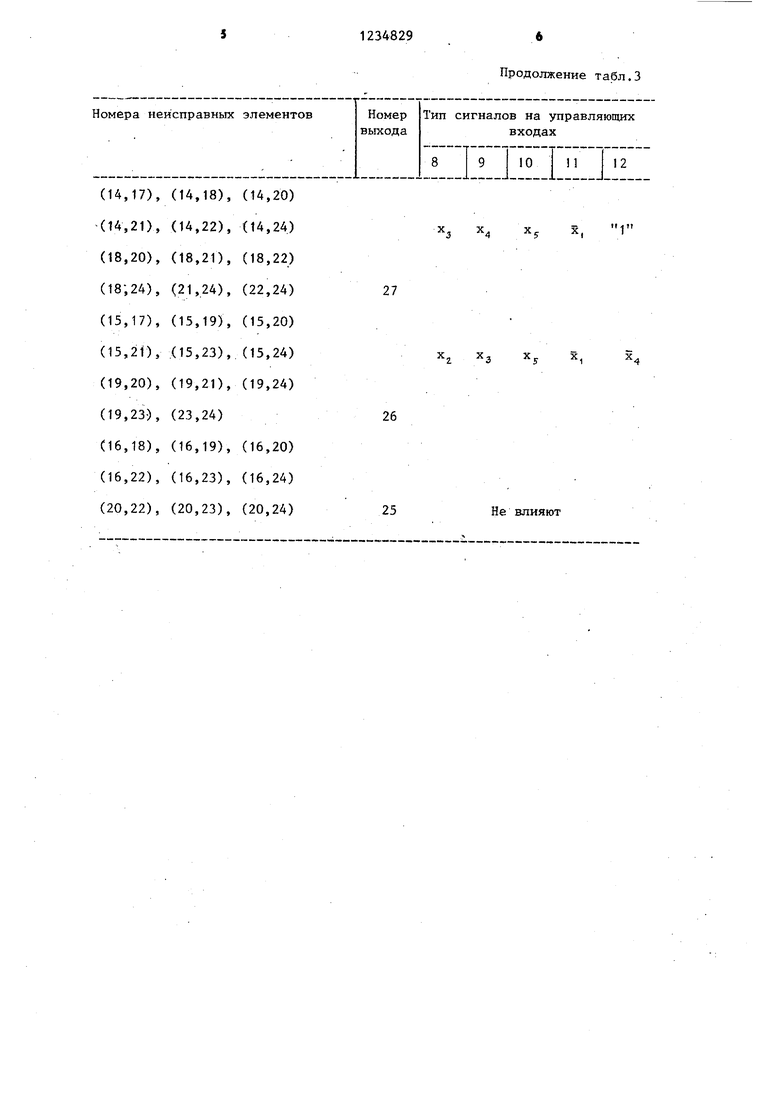

При наличии одиночных неисправностей на управляющие входы 8-12 подаются соответствующие сигналы и значение сигнала переноса снимается с одного из выходов 25-28 согласно табл. 2. При наличии двойных неисправностей сигнал переноса в следующий четвертичный разряд формируется на выходах устройства согласно табл. 3.

Задача определения отказавших элементов может решаться при помощи диагностических тестов, которые можно построить любым из известных способов, например методом полного перебора входных переменных.

Пример функционирования устройства.

Пусть по результатам тестирования устройства установлено, что имеет место неисправность типа . В этом случае на управляющие входы 8-12 подаются соответственно сигналы х , х, х, х, и Константа 1, Выходной сигнал снимается с выхода 28

Анализ возможных вариантов одиноч ньгх, двойных, тройных неисправностей показывает, что устройство сохраняет работоспособность при 100% одиночных неисправностей, 79% двойных и 41% тройных неисправностей.

Устройство построено на элементах двух типов. Однако При реализа- .ции устройства по интегральной технологии предпочтительна полная однородность структуры. Устройство можно легко привести к виду, упрощающему его решп1зацию в виде интегральггых микросхем. Для этого элементы ИЛИ-НЕ

348292

Устройство работает cлeдyJoш м образом.

На информа донные входы 1-7 подаются сигнал.. в соответствии с . 5 табл, 1. Причем к,, являются старши1чи разрядами суммируемых четвертичных операндов, х, х - мпад- гаими разрядами, х - сигнал переноса из предьщущего четвертичного О разряда.

В случае исправного состояния устройства значения сигналов на управляющих входах 8-12 безразличны, и с выхода 25, на котором реализует- 15 ся булевая функция вида

можно реализовать в виде элементов 2Q равнозначности с дополнительными входами, на которые постоянно подается сигнал Константа О.

Формула изобретения

Адаптируемое устройство для форхми- рования сигнала переноса, содержащее элементы равнозначности., причем первый и второй входы первого элемента равнозначности соединены с первым и вторым информационными входами устройства соответственно, первый и второй входы второго элемента равнозначности соединены с третьим и четвертым информационными входами устройства соответственно, первый и второй входы третьего элемента равно- знач:ности соединены с пятым и шестым информационными входами устройства соответственно, первьш и второй входы четвертого элемента равнозначности соединены с первым и вторым управляющими входами устройства соответственно, первый вход пятого элемента равнозначности соединен с седьмым информационным входом устройства 5 отличающееся тем, что, с целью упрощения 5 в него введены элементы И-НЕ, причем второй информационный вход устройства соединен с третьими входами второго и третьего элементов равнозначности, третий информационный вход устройства соеди- Hei с третьим входом первого элемента равнозначности, четвертый ин- формационный вход устройства соединен с четвертым входом третьего элемента равнозначности, пятый информационный вход устройства соединен с

четвертыми входами первого и второго элементов равнозначности, шестой информациойный вход устройства соединен с пятым входом первого элемента равнозначности, седьмой инфор мационный вход устройства соединен с первыми входами шестого, седьмого и восьмого элементов равнозначности i-й (,5) управляющий вход устрой ства соединен с i-м входом четверто го элемента равнозначности, входы первого элемента И-НЕ соединены с выходами первого, второго и четвер того элементов равнозначности соответственно, входы второго элеменНомер информационного входа1 2 3 |4 56 7

Тип сигнала

(13,17), .(13,18), (13,19) (13,21), (13,22),(13,23) (17,18), (17,19), (17,21) (17,22)), (17,23), (21,22) (21,23)

5

2348294

та И-НЕ соединены с выходами первого, третьего и четве ртого элементов равнозначности соответственно, входы третьего элемента И-НЕ соединены с выходами второго, третьего и четвер-. того элементов равнозначности соответственно, входы четвертого элемента И-НЕ соединены с выходами первого, второго и третьего элементов равно- значности соответственно, выход j-ro (j lj ) элемента равнозначности соединен с вторым входом (j+4)-ro элемента равнозначности, выход которого ссгединен с j -м выходом устройства.

10

15

Таблица 1

Л .

X, х

Та б л и ц а 2

Таблица 3

XjХзХ

1

(14,18),

(14,22),

(18,21),

(21,24),

(15,19),

.(15,23),

(19,21),

(23,24)

(16,19),

(16,23),

(20,23),

(14,20) (14,24) (18,22) (22,24) (15,20) (15,24) (19,24)

(16,20) (16,24) (20,24)

Продолжение табл.3

х X, X, X, Г

г 3 5 1 4

25

Не влияют

8 еЮ11121 2 J If 5 S 7

Редактор E, Копча

Составитель A. Федоров Техред М.Ходанич

Заказ 2986/51Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г, Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный адаптируемый четверичный сумматор | 1981 |

|

SU1053102A1 |

| Адаптируемый четверичный сумматор | 1986 |

|

SU1417011A1 |

| Одноразрядный четверичный сумматор | 1981 |

|

SU1023322A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| Самоконтролируемый мультиплексор | 1985 |

|

SU1302270A1 |

| Четверичный сумматор | 1983 |

|

SU1124290A1 |

| Устройство для возведения в квадрат в избыточном коде | 1985 |

|

SU1307457A1 |

| Устройство для вычисления обратной величины | 1984 |

|

SU1241231A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при разработке надежных суммирующих узлов обработки цифровой информации. Адаптируемое устройство формирования сигнала переноса предназначено для формирования сигнала переноса при суммировании четверичных чисел. Устройство содержит элементб равнозначности и ШШ-НЕ, семь информационных и пять управляющих входов и четыре выхода. На информационные входы устройства подаются разряды суммируемых четверичных цифр, сигнал переноса из предыдущего четверичного разряда и их инверсии, В случае исправного состояния устройства значения сигналов на управляющих входах безразличны. Значение вьЕсодного сигнала переноса снимается с первого выхода устройства. При возникновении в устройстве неисправности на управляющие входы подаются соответствующие сигналы, а выходной сигнал переноса снимается с одного из выходов устройства. Номер выхода и значения сигналов на управ-- ляющих входах определяются видом неисправности. Возможность адаптации при возникновении неисправности позволяет сохранять работоспособность устройства при любых одиночных, а также 79% двойных и 41% тройных неисправностей, 1 ил, 3 табя.(С (Л tvs СО 4 00 ю со

| Лыснков Б.Г | |||

| Арифметические и логические основы цифровых автоматов | |||

| Минск: Вьшейшая школа, 1980, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-11-27—Подача