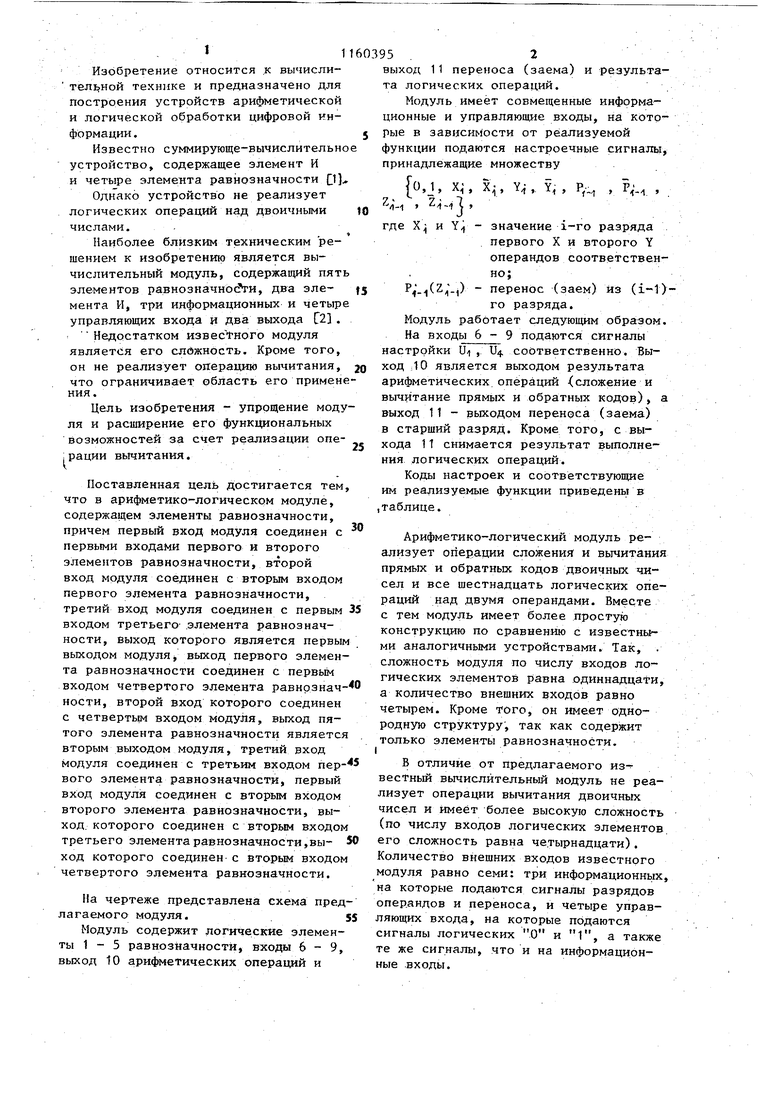

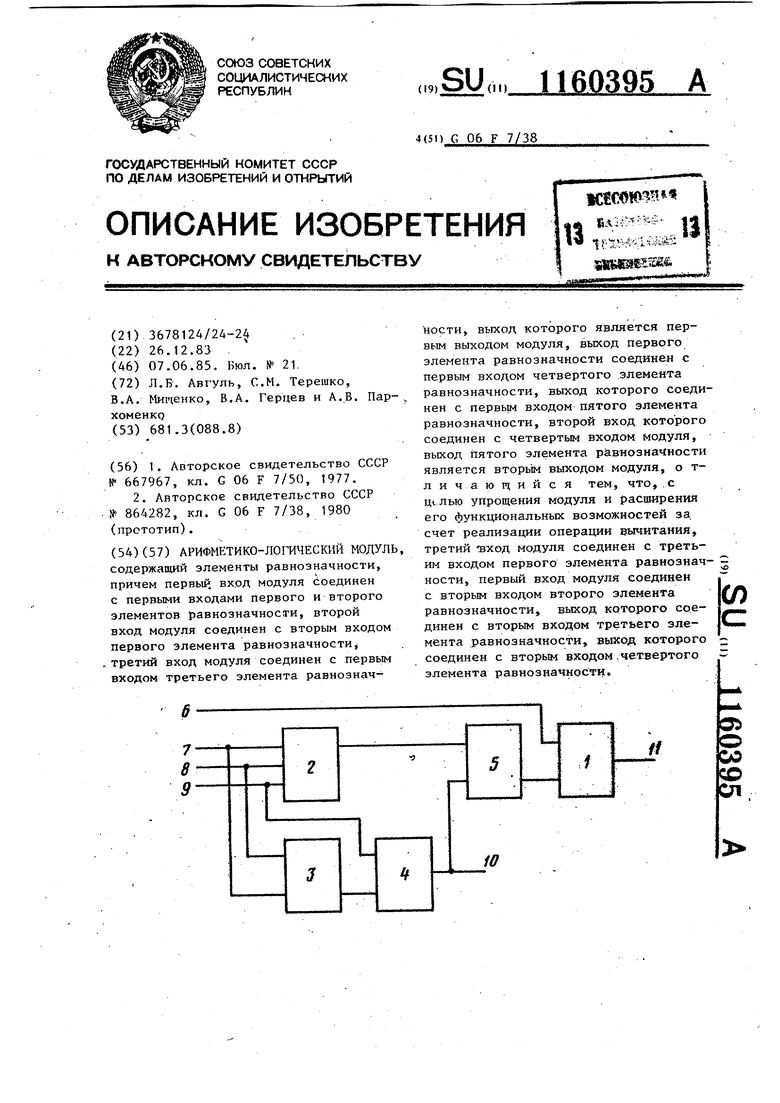

Изобретение относится к вычисли технике и предназначено для построения устройств арифметической и логической обработки цифровой информации. Известно суммирующе-вычислительно устройство, содержащее элемент И и четыре элемента равнозначности р) OnffaKo устройство не реализует логических операций над двоичными числами. . Наиболее близким техническим решением к изобретению является вычислительный модуль, содержащий пять элементов равнозначнос ги, два элемента И, три информационных и четыре управляющих входа и два выхода L2. Недостатком извес тного модуля является его слбжность. Кроме того, он не реализует операцию вычитания, что ограничивает область его примене ния . Цель изобретения - упрощение моду ля и расширение его функциональных возможностей за счет реализации опеi рации вычитания. Поставленная цель достигается тем что в арифметико-логическом модуле, содержащем элементы равнозначности, причем первый вход модуля соединен с первыми входами первого и второго элементов равнозначности, второй вход модуля Соединен с вторым входом первого элемента равнозначности, третий вход модуля соединен с первым входом третьего .элемента равнозначности, выход которого является первым выходом модуляj выход первого элемента равнозначности соединен с первьш входом четвертого элемента равнрзначности, второй вход которого соединен с четверть1М входом модуля, выход пятого элемента равнозначности является вторым выходом модуля, третий вход модуля соединен с третьим входом первого элемента равнозначности, первый вход модулей соединен с вторым входом второго элемента равнозначности, выход/которого соединен с вторым входом третьего элемента равнозначности,выход которого соединен с вторым входом четвертого элемента равнозначности. На чертеже представлена схема пред лагаемого модуля. . Модуль содержит логические элементы 1 - 5 равнозначности, входы 6-9, выход 10 арифметических операций и выход 11 переноса (заема) и результата логических операций. Модуль имеет совмещенные информационные и управляющие входы, на которые в зависимости от реализуемой функции подаются настроечные сигналы, принадлежащие множеству 0,1, X,, Yi . Y, , Р. z,,,j. где Х и Y значение 1-го разряда первого X и второго Y операндов соответственно;P - Z-i-i) - перенос (заем) из ()го разряда. Модуль работает следующим образом. На входы 6-9 подаются сигналы настройки Ui , 1)4 соответственно. Выход ilO является выходом результата арифметических.операций сложение и вычитание прямых и обратных кодов), а выход 11 - выходом переноса (заема) в старший разряд. Кроме того, с выхода 11 снимается результат выполнения логических операций. Коды настроек и соответствующие им реализуемые функции приведены в таблице. Арифметико-логическиг модуль реализует операции сложения и вычитания прямых и обратных кодов двоичных чисел и все шестнадцать логических операций над двумя операндами. Вместе с тем модуль имеет более простую конструкцию по сравнению с известными аналогичными устройствами. Так, . сложность модуля по числу входов логических элементов равна .одиннадцати, а количество внешних входов равно четырем. Кроме того, он имеет однородную структуру, так как содержит только элементы равнозначности. . . В отличие от предлагаемого известный вычислительный модуль не реализует операции вычитания двоичных чисел и имеет более высокую сложность (по числу входов логических элементов его сложность равна че.тырнадцати) . Количество внешних входов известного модуля равно семи: три информационных, на которые подаются сигналы разрядов операндов и переноса, и четыре управяющих входа, на которые подаются сигналы логических О и 1, а также те же сигналы, что и на информационные .входы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Управляемый арифметический модуль | 1978 |

|

SU840881A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Одноразрядный четверичный сумматор-вычитатель | 1984 |

|

SU1229756A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Вычислительный модуль | 1980 |

|

SU864282A1 |

| Адаптируемое суммирующе-вычитающее устройство | 1981 |

|

SU1005036A1 |

АРИФМКТИКО-ЛОГИЧЕСКИЙ МОДУ содержащий элементы равнозначности, причем первый, вход модуля соединен с первыми входами первого и второго элементов равнозначности, второй вход модуля соединен с вторым входо первого элемента равнозначности, третий вход модуля соединен с первы входом третьего элемента равнознач7 8 9 LJ it ОЭ ел ности, выход которого является первым выходом модуля, выход первого элемента равнозначности соединен с первым входом четвертого .злемеята равнозначности, выход которого соединен с первь1м входом пятого элемента равнозначности, второй вход которого соединен с четвертым входом модуля, выход пятого элемента равнозначности является BTopbiM выходом модуля, о тличающийся тем, что, .с щлью упрощения модуля и расширения его функциональных возможностей за. счет реализации операции вычитания, третий ВХОД модуля соединен с третьим входом первого элемента равнозначности, первый вход модуля соединен с вторым входом второго элемента равнозначности, выход которого соединен с вторым входом третьего элемента равнозначности, выход которого соединен с вторьм входом .четвертого элемента равнозиачнос:ти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительный модуль | 1980 |

|

SU864282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-07—Публикация

1983-12-26—Подача