Изобретение относится к вычислительной технике, в частности к устройствам обмена электронных вычислительных машин с внешними устройствами.

Известно устройство для связи цифровой вычислительной машины с внешними устройствами, содержащее блок оперативной памяти, блок долговременной памяти, регистр связи, коммутатор, формирователь адреса, шифратор, синхронизатор CllНаиболее близким к предлагаемому является устройство для сопряжения с абонентами, содержащее блок Долговременной памяти, регистр адреса регистр заявок, регистр готовности, блок начального пуска, элементы по числу абонентов,элемент ИЛИ, переключатель, входы и выходы устройства, 2 .

В данном устройстве не обеспечивается хранение констант, которые необходимы во многих системах-обмена. Константами, например, могут быть фиксированные адреса оперативной ftaмяти, управлякяцие слова внешних устройств, информация для прогргшмного контроля. Такое ограничение функциональных возможностей устройства ухудшает показатели его работы в системах обмена, использующих константа.

Цель изобретения - повышение производительности устройства.

Поставленная цель достигается тем, . что в микропрограммное устройство управления -каналом ввода-вывода, содержащее модификатор адреса, регистр адреса микрокоманд, блок постоянной

10 памяти Микропрограмм, регистр микрокоманд, дешифратор, информационный вход которого соединен с управляющим выходом регистра микрокоманд, hepвый адресный выход которого соединен с

,15 первым входом модификатора адреса, второй вход которого соединен с управляющим входом устройства, а выход - с информационным входом регистра адреса микрокоманд, управляющий

20 вход которого соединен с первым входом тактовых импульсов устройства, выход блока постоянной памяти микропрограмм соединен с информационным входе регистра микрокоманд, второй

25 вход тактовых импульсов устройства подключен к управляющему входу блока постоянной памяти микрокоманд, первый выход дешифратора подключен к управлякяцему выходу устройства,

30 дополнительно введены регистр регенерации .адреса, триггер управления регенерацией, блок элементов ИЛИ, триггер выборки констант, регистр констант , причем информационный вход регистра констант соединен с выходом констант регистра микрокоманд, выход идентификатора выборки констант кото рого соединен с установочным входом триггера выборки констант, единичный выход которого подключен к управляюдему входу регистра констант, выход которого подключен к информационному выходу устройства, нулевой выход триггера выборки констант подключен к управляющему входу дешифратора, второй выход которого соединен с управляющим входом регистра регенерации адреса, информационный вход которого соединен с вторым адресным выходом регистра микрокоманд, выход триггера управления регенерацией подключен к первому входу блока элементов ИЛИ, второй вход которого соединен с информационным выходом регистра адреса микрокоманд, выход признака константы которого соединен с установочным входом триггера управления регенерацией, управляющий вход которого соединен с первым входом тактовых импульсов устройства, выход регистра регенерации адреса соединен с третьим входом блока элементов ИЛИ выход которого соединен с адресным входом блока -постоянной памяти микропрограмм, третий вход тактовых импульсов устройства соединен с управляющим входом триггера выборки конетант.

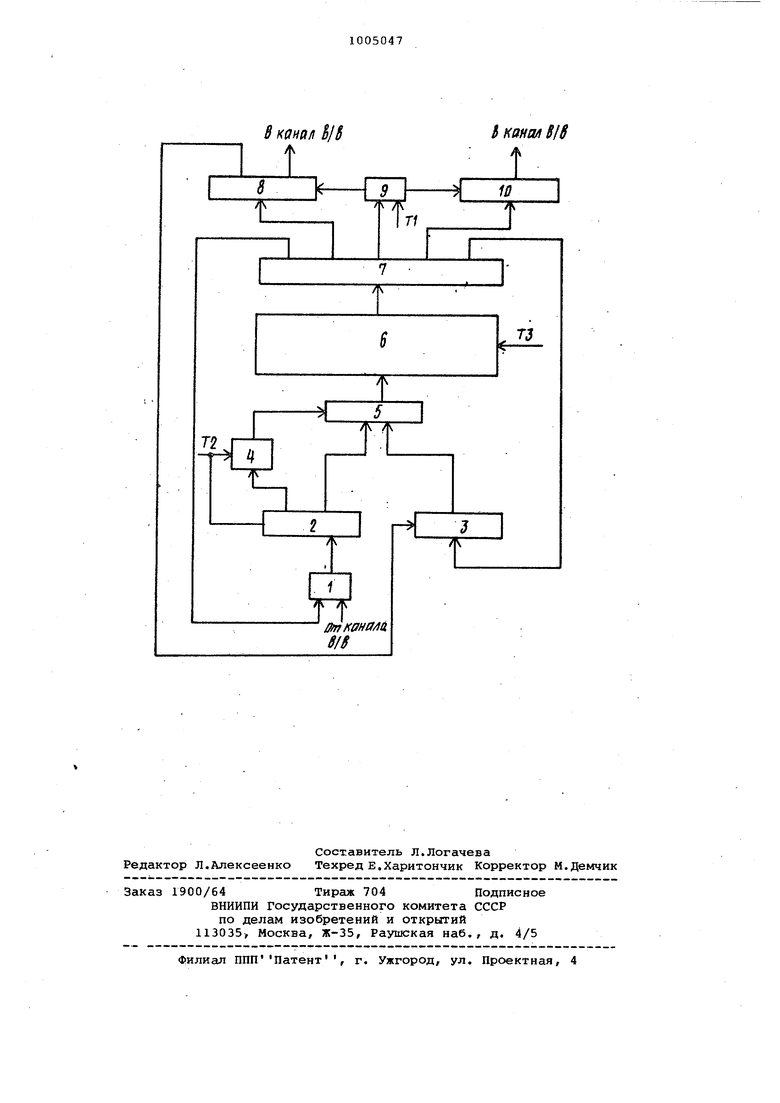

На чертеже представлена функцио- нальная схема микропрограммногб устройства управления каналом ввода-вывода, .

Микропрогграмное устройство управления каналом ввода-вывода содержит модификатор 1 адреса, регистр 2 адреса микрокоманд, регистр 3 регенерации адреса, триггер 4 управления регенерацией, блок 5 элементов ИЛИ, блок 6 постоянной памяти микропрограмм, регистр 7 микрокоманд, дешифратор 8, триггер 9 выборки констант, регистр 10 констант.

Работа микропрограммного устрой- г ства управления каналом ввода-вывода осуществляется следующим образом.

Адрес микрокоманды поступает нгГ первый вход модификатора 1 адреса, на второй вход которого поступает информация о состоянии канала ,.Измодификатора 1 измененный адрес микрокоманды записывается по тактовому импульсу Т2 в регистр 2 адреса микроксиланд, с второго выхода которого он поступает на второй вход блока 5 элементов ИЛИ и, если не требуется регенерации адреса,с выхода триггера 4 управления регенерацией вьщается на первый вход блока 5 элементов ИЛИ

сигнал разрешения прохождения адреса микрокоманды на первой вход блока 6 постоянной памяти микропрограмм. Затем по тактовому импульсу ТЗ из блок б постоянной памяти микропрограмм выбирается информация, соответствующая данному адресу, и записывается в регистр 7 микрокоманд, выходы КОТОРОГО дешифруются дешифратором.

Предположим, что в регистре 7 . микрокоманд наЗсодится микрокоманда, после выполнения которой из блока б долговременной памяти микропрограмм должна выбраться не микрокоманда, а константа. В ходе выполнения этой микрокоманды информация с выхода региЪтра 7 микрокоманд поступает на вх регистра. 3 регенерации адреса и заносится туда по появлению управляющего сигнала, который поступает с первого выхода дешифратора 8 на вход регистра 3 регенерации адреса. Эта информация представляет собой адрес (или часть адреса) микрокоманды, которая выполняется после выборки констацты. Затем информация с третьего выхода регистра 7 микрокоманд поступает на первый вход триггера 9 выборки констант, в котором и запоминается после появления на втором входе тактового импульса Т1. Эта информация является идентификатором выборки константы. Адрес константы поступает с. выхода регистра 7 микрокоманд на первый вход модификатора 1 адреса и заносится в регистр 2 адрес микрокоманд.

Таким образом/ в данный момент времени в регистре 2 адреса микрокоманд находится адрес константы, а в регистре 3 регенерации адреса - адре (или часть адреса) следующей за константой, микрокоманды.

Тррирер 4 у.правления регенерацией распознает- адрес константы и запоминает приэН)ак константы. Адрес константы из регистра 2 адреса микрокоманд через блок 5 попадает на вход блока б постоянной памяти микропрограмм. ПЬсле появления тактового кмпульса ТЗна входе блока б постоянной памяти микропрограмм выбирается константа и запоминается на регистре 7 микроко|манд. Триггер 9 выборки констант выдает на вход дешифратор а 8 сигнал запрещения дешифрации выходов регистра 7 микрокоманд, а на вход регистра 10 консг тант - сигнал разрешения приема информации с выходов регистра 7 микрокоманд. Константа запоминается на регистре 10 констант и поступает оттуда на другие устройства канала.

После этого идентификатор константы в триггере 9 выборкиконстант сбрасывается. В регистре 7 микрокоманд вместе с константой может храниться часть адреса следующей микрокоманды, которая поступает в регистр 2 адреса микрокоманд. Таким образом в данный MONffiHT времени в регистре 2 адреса микрокоманд находится или часть адреса следующей микрокоманды или информация, являющаяся частью константу и не имеющая отношения к адресу следующей .микрокоманды. Соответственно в регистре 3 регенерации адреса находится или часть адреса следующей микрокоманды дополняющая содержимое регистра 2 адреса микрокоманд до полного адреса, или целиком адрес следующей микрокоманды. Триггер 4 управления регенерацией вьидает сигнал разрешения на |йдновременное прохождение сигналов b выходов регистра 2 адреса микроко манд и регистра 3 регенерации адреса через блок 5 таким образом, что на вход б блока постоянной памяти микропрограмм поступает полный адрес следующей микрокоманды. После выборки микрокоманды по этому адресу признак константы в триггере 4 управ ления регенерацией сбрасывается и устройство управления каналом переxpQHT в первоначальный режим работы Использование новых блоков трйггера 4 управления регенерацией, регистра 3 регенерации адреса, блока 5, триггера 9 выборки констант, .регистра 10 констант выгодно отличает данное микропрограммное устройство управления каналом ввода-вывода от прототипа, так как обеспечивается работа одного и того же микропрограммного устройства управления в двух режимах: в режиме микропрограммного устройства управления ив режиме аппаратного устройства управ пения, что-позволяет, р.асширив функ циональные возможности устройства, повысить эффективность работы систем обмена. Повышение эффективности ска зывается, например, в увеличений .. производительности как системы обмен так, и ЦВМ в целом, в увеличении гиб кости устройства управления, что поз воляет простой заменой блока постоян ной памяти микропрограмм изменять не только сшгоритм обмена, но и I oftfAты и содержание констант о(4ена. Фррмула изобретения Микропрограммное устройство управления каналом ввода-гвывода/ содержащее модификатор адреса, регистр адреса микрокоманд, блок постоянной памяти микропрограмм, регист микрокоманд, дешифратор, информахшо ннй вход которого соединен с управляющим выходом регистра микрокоманА первый адресный выход(которого соединен с первым входом модификатора адреса, второй вход которого соединен с управляющим входом устройства, а выход - с информационным входом регистра адреса микрокоманд, управляющий вход которого соединен с первым входом тактовых импульсов устройства, выход блока постоянной памяти микропрограмм соединен с информационным входом регистра микрокоманд, второй вход тактовых импульсов устройства подключен к управляющему входу блока постоянной памяти микрокоманд, первый выход дешифратора подключен к управляющему выходу устройства, отличающееся тем, что,с целью повышения производительности, оно содержит регистр регенерации адреса, триггер управления- регенерацией, блок элементов ИЛИ, триггер выборки констант, регистр констант, причем информационный вход регистра констант соединен с выходом (Констант регистра микрокоманд, выход идентификатора выборки констант которого соединен с установочным входом .триггера выборки константу единичный выход которого подключен к управляющему входу регистра констант, выход которого подключен к информационному выходу устройства, нулевой выход триггера выборки констант подключен к управлякяцему входу дешифратора, второй выход которого соединен с управлякицим входом регистра регенерации гщреса, информационный вход которого соединен с вторым адресным выходом регистра микрокоманд, выход триггера управления регенерацией подключен к первому входу блока эле-, ментов ИЛИ, второй вход которого, соединен с информационньм выходом регистра адреса микрокоманд, выход признака константы которого соединен с установОЯным входом триггера управления регенерацией, управляющий вход которого соединен с первым входом тактовых импульсов устройства, выход регистра регенерации адреса соединей с третьим входом блокаЭлементов ИЛИ выход которого соединен с адресным входом блока постоянной памяти микрог. nporpai«M, третий вход тактовых имруль сов устройства соединен с управляющим входом триггера выборки констант. Источники информации, .принятые во внимание при экспертизе . 1. .Авторское свидетельство СССР I 5Э1850, кл. G 06 F 3/04, 1976. 2. Авторское свидетельство СССР 504199, кл. G 06 F 3/04, 1974 (прототип). . .

S кана/1 S/S

1

т

дпл ана/1л 8/8

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для управления цифровой вычислительной машиной | 1974 |

|

SU520591A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU811254A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство микропрограммного управления | 1985 |

|

SU1293730A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-15—Подача