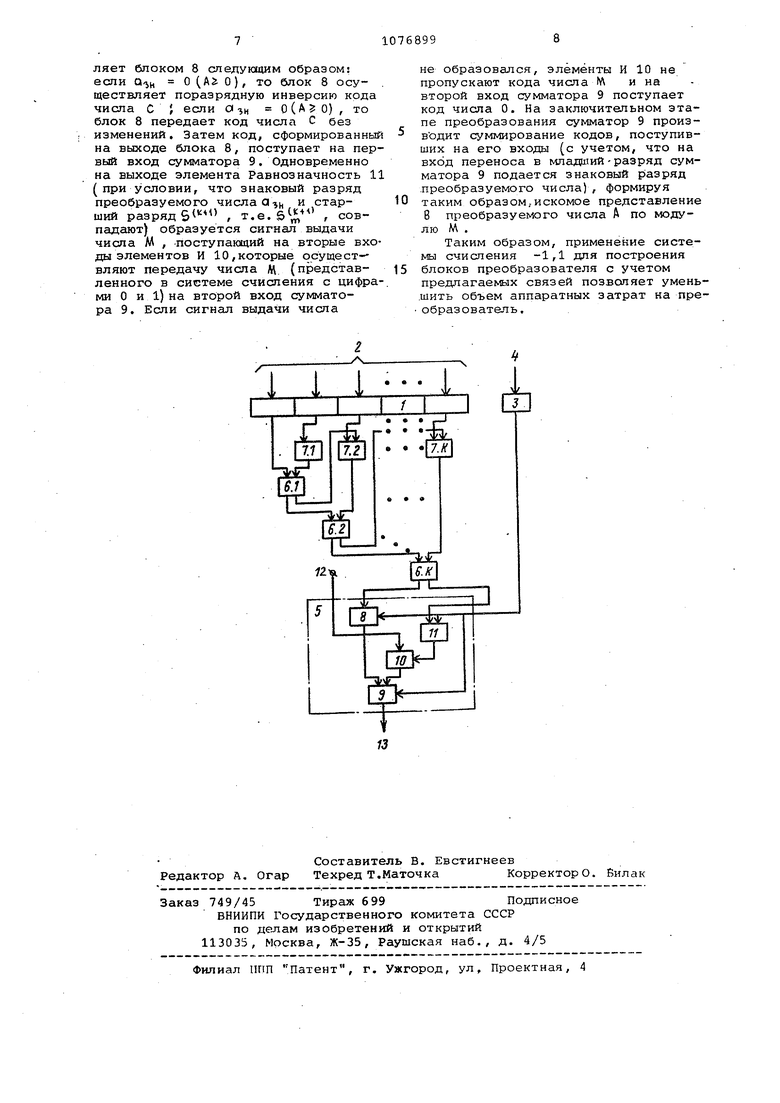

Изобретение относится к вычисли тельной технике и может быть испол эовано при построении специализиро ванных вычислитель -1)э1Х устройство Известен преобразователь;, предн наченны для преобразования двоичного кода в код системы остаточных классов и содержащий входной регис матричные cxeivbi умножения коррект рующий матричн1.Ш сумматор и выходной сумматор l . Недостатками указанного преобра зователя являются значительный объ оборудования и низкое быстродейств Наиболее близким технршеским ре шением к предлагаемог 1у является пр образователь двоичного числа в его представление по мо,щлю/Vi, содержащий три.ггер знака, вход которого является входом знака преоб разователя , входной регистр, состоя щий из К + 1 групп двоичных разрядов, вход которого является информационным входом преобразовгттел К блоков хранения констант, К сум маторов по модулю М и выходной сум матор , причем выход первой группы входного регистра подключен к первомУ входу первого сумматора по модулю А , второй вход которого соединен с выходом первого блока хране ния констант, выхо.ц 1 й группы ( 2,3,..., К -bli входного регр1стра подключен кадресному входу (1 -1)-го блока хранения констант, выход j -го блока хранения констант подключен к перво «у входу j -го сум матора по модулю ЛА J второй яход ) -го сумматора по модулю М подключен к информационному выходу (j -l)-го сумматора по модулю hK{l 2,3,.,,, К , информационный выход к -го сгум-латора по модул о подключен к первому информационному входу выходного суМЛатора по модулю ЛЛ , второй информационный вход которого соединен с управляющим входом К ГО сумматора по модулю М и является входо1М константы М преобразователя, знаковый вход выходного сумматора полклюгчен к выходу триггера знака 2J ,. Недостаток известного преобразователя обусловлен значительным объе мом оборудования, зызванного тем., что каждьп из суг маторов состоит из двух ill -разрядных сумматоров с распространением переносов, одного m -разрядного сум матора без распространения переносов и муль типлексораоЦель изобретения - уменьшение объема оборудования. Поставленная цель достигается тем, что в преобразователе и -разpH ;b;Horo двоичного -илсла в его представление по модулю № , содер жащем триггер знака,, вход которого является входом знака преобразовате.пя. входной регистр, состояпий из К -г 1 групп по гп (к n/m) двоич ных разрядов, вход которого является .информационным входом преобразователя К блоков хранения констант, К су:мматоров группы и. выходной сумматор, выход первой группы входного регистра подключен к первому входу первого сумматора группы, второй вход которого подключен к выходу первого, блока хранения констггнт, выход -и группы ( i 2 , 3 , „ . о , k +1) выходного регистра подключен к адресному входу ( -1)-го блока хранения констант, выход j -го хранения констант подключен к первог.-гу входу j -го сумматора группы, второй вход 3 -го сумл1атора группы подключен к информационному выходу (.j-l}-ro сугф.1атора группы (;j 2,3,,...., |) , информационный выход 1 -го сумматора группы подключен к первому информационнок1у входу выходного сумматора, второй информаи,ионный вход которого является входом константы М преобразователя, а первый знаковый вход подключен к выходу триггера знака, выход выходного сумматора является выходом преобразователя, управлявший вход 1 -го блока хранения констант подключен л; выходу старшего разряда ( -1) -го сумматора группы, второй знаковый вход вы| одного сумматора подключен к выхоДу старшего разряда К -го сумглатора группы. Кроме того, выходной сумгдатор содержит блок формирования прямого и обратного кодов, элемент Равнозначность, группу элементов К и двоичный сумматор, выход которого яв.ляется выходом выходного сумматораf первы информационный вход двоичного сумматора подключен к выходу блока форьтерозания прямого и обратного кодов, информационный вход которого является первым информационньэм входом выходного сумматора, второй информационный вход двоичного сум1.1атора подключен к группе выходов элементов И группы, первые входы которых соединены с вторым информационным входом выходного су1 Ф1атора, а вторые входа подключены к выходу элемента Рав.нозначность, первый вход которого соединен с управляюш,им входом блока формирования прямого и обратного кодов, с входом переноса двоичного сумгчштора и является первым, знаковым входом выходного сумматоре , второй вход элемента Равнозначность является вторым знаковым входом выходного сумматора, На чертеже представлена структурная схема преобразователя П -разрядного двоичного числа в его представление по модулю М „ Преобразователь содержит входно регистр 1, информационный вход 2, триггер 3 знека, вход 4 знака, выходной сумматор 5, сумматоры 6 Л, б,2,.,.,б, К группы, блоки 7о1, 7. ...,7. К хранения констант, входящие в состав сумматора 5 блок 8 фо мирователя прямогои обратного код двоичный сумматор 9, элементы И 10 группы, элемент Равнозначность 11, а также вход 12 константы М- и выход 13. . Преобразование целого цисла А в его представление 6 по модулю производится следующим образом. Мантисса числа Д, разбивается на ( к +1 групп А 1, Для каждой и групп, формируется ее представл ние по модулю М . При этом В получается непосредственно, а для 2 , .. . , К +1 В формируются с помощью блоков 7 постоянной памяти Затем путем суммирования всех .п модулю М вычисляется представление мантиссы исходного числа по модулю М ВЬ(.„ В УтосЗ/. (1 .Для вычисления выражения (1) и пользуется дерево К сумматоров, к да1й из которых выполняет операцию вида 5lnO.|g-3(4Bi WoJM ( М где : J 1,2,..., К.. , На заключительном этапе преобра зования из В формируется В с учетом знака исходного числа А, Уменьшение объема оборудования в предлагаемом преобразователе по сравнений с известным достигается в результате более простой реализа ции операции суммирования по модулю М . С этой целью исходное число представляется в системе счисления с цифрами -1 и 1 (так называемой системе Баньковского,. в которой количественный эквивалент числа X Uvn,Xm-(f ...,Хо) определяется следующим образом: х,-Ь|,,где XJ е f-l,l.. Из выражения Сз) следует, что для целого числа X о,, , представленного в системе счисления с цифрами О .и 1 в дополнительном коде 0, )- 1 О его представление в системе Баньковского, полученное при условии, что цифра -1 кодируется, как О, а цифра 1 как 1, имеет вид Л Зи 1 m-n т-2 Таким образом, для m +1) -разрядных операндов, представленных в системе Баньковского, правило выполнения операции суммирования по модулю М .. (йыражение (2 ) состоит .в следующем: если при суммировании чисел 5il образовался или не образовался перенос из старшего разряда двоичного сумматора (соответственно Р 1 или р - .0) , то для получения окончательного результата операции необходимо прибавить соответственно число - М или + М , представленное также в системе Паньковского. Пример. 5 12+llmodl3 . 10 «loci 13 11100 - 12 + 11011 11 1. 10111 Р 1 + 00011ге-(-13) 11010 - 10 ,H2)(-Ul)mo(3 ВЕ(, 1Ъ 00100 (-12) + 00101- - (-11) . О 01001 р -О + 11101 - (+13) Из приведенного правила следует, что в случае, когда оба операнда являются либо положительными в стар ших разрядах обоих операндов эафиксированы единицы, т ,е . Ь « Vj либо отрицательными О}, то заведомо известно, что необходимо прибавить либо -М , либо + М соответственно. Поскольку в системе Баньковского каждое число Хе Ед( , где 2д, (0,1,2,.,., М-1Ь кроме положительного представления имеется- и отрицательное представление, так как Xs (X-M)wod М,. то ,цля любого значения операнда всегда можно подобрать такое представление операнда при котором значения старших разрядов обоих операндов совпадают. Следовательно,для (m +1)-разрядных операндов, представленных в .системе Баньковского, операцию суммирования по модулю /Л вида5 (5 В 1110 Мможно производить с помощью ( -t-1) -разрядного двоичного ciMMaTopa, при условии, что с пo ющью ПЗУ формирую -ся не

просто 8 , а в зависимостр} от значе аия 5 формируются ) или() для бД 1 или 5JJ, О соответственно. ,

Поскольку 6 является положительным числом, то в первом ПЗУ всегда формируется(В-М ) .

П р и м е р 2;

5 нО21-и)то(3 mod 15 11011 --11

f 00011 (-13)

11110.- () + 11100 - 12

11010 10 ((H2U(-1l))mod l3 ()mod 13

00101- -(-11) lllpl « (+13)

00010- () + 0010.0 -(-12)

(-10)

00110

На заключительномэтапе преобразования исходного числа А в его представление 8 по модулю М . необходимо преобразовать число 5 l) В f представленное s системе Баньковского, в положительное число Б г представленное в системе счисления с цифрами О и 1.

Исходя из .выражений (4) и (5) , а также учитывая то, что для положительного числа , представленного в системе счисления с цифрами О и 1 (-Ч)5(М-Ч) тосЗМи лЛ-V М - Vg где Хп - дополнительный код , приходим к следующим прав1-шам выполнения указанного преобразования.

ЕСЛИ А г- О и , т.е, а,и О, 6Г 1, о

Б С

(б)

где С - код, полученный изЗ путем отбрасывания разрядаб, ,j,,i

Если А О H. , T,e. то

, (7)

где М - w -разрядный код числа

в cHCTejv5e счисления с цифрами О и 1.

Еспи А 0 и5 :П, т,е,а,н i 6Г 1, то

(и)

+ с -м .

.

-1,

т.е. а

чи т

С, то

.

(91

Преобразователь работает следующим-образом.

В исходном состоянии триггер 3 знака и регистр 1 обнулены, В триггер 3 знака и входной регистр 1

записываются соответственно знак и мантисса преобразуемого числа А . После того, как знак и мантисса пре образуемого числа зафиксируются в триггере 3 знака и входном регистре 1 соответственно, на вход блока 7.1 хранения констант поступает И -разрядный код Д, под воздействием которого из блока 7.1 хранения констант считывается значение( )

соответствующее коду (представленное в системе Баньковского), которое поступает затем на первый вход сумматора 6.1 группы, на второй вход которого поступило уже число В ,

Сформированное непосредственно из и представленное в системе БаньковскогОе (Гумматор 6.1 труппы формирует 3Ha4eHHeS s()hiodMs(, представленное в системе Баньковского f которое поступает на второй

вход сумматора 6.2 группы блока

хранения констант. Одновременно старший бит S, , т.е. 5 , поступает на первый вход блока хранения констант на второй вход которого

поступил уже код А . Разряд 9 Дуправляет выборкой информации из блока 7.2 хранения констант 7,2 следующим образом: если О, то из блока 7.2 хранения констант считывается значение () соответствующее коду А ; если 5 1, то из блока 7i2 хранения констант считывается ,значение () , соответствующее коду А . Сформированное

таким образом на выходе блока 7.2 хранения констант значение( М) представленное в системе Баньковского,,поступает на первый вход сумматора 6.2 группы, который формирует значение S(, В) vnod М .,

представленное в системе Ваньковского. Аналогичным образом.с помощью блоков 7 . 3 , ,, 7 . К хранения констант и сумматоров 6.3,,.,,6,К групп вырабатываются последующие з начения

( ) moJ М, 3,k

(все представленные в системе Баньковского) вплоть до5 гр , которое формируется сумматором 6. k группы. Далее Т) младших i разрядов 5

(образующих код числа С) поступают на информационный вход блока 8 формирования прямого и обратного кода, на управляющий вход которого с триггера 3.знака поступает знак преобразуемого числа d зи г который управляет блоком 8 следующим образом: если Q-jH О (Ai 0), то блок 8 осуществляет поразрядную инверсию кода числа С ; если а-JH О (А 50), то блок 8 передает код числа С без изменений. Затем код, сформированный на выходе блока 8, поступает на первый вход сумматора 9. Одновременно на выходе элемента Равнозначность 11 (при условии, что знаковый разряд преобразуемого числа а,ц и старший разряд S , т.е. , совпадают) образуется сигнал выдачи числа М , поступающий на вторые входы элементов И 10,которые осуществляют передачу числа М (представленного в системе счисления с цифра-, ми О и 1) на второй вход сумматора 9. Если сигнал выдачи числа

не образовался, элементы И 10 не пропускают кода числа М и на второй вход сумматора 9 поступает код числа 0. На заключительном этапе преобразования сумматор 9 производит суммирование кодов, поступивших на его входы (с учетом, что на вход переноса в младшийразряд сумматора 9 подается знаковый р азряд .преобразуемого числа), формируя

0 таким образом,искомое представление 6 преобразуемого числа А по модулю М .

Таким образом, применение системы счисления -1,1 для построения

5 блоков преобразователя с учетом предлагаемых связей позволяет уменьшить объем аппаратных затрат на преобразователь.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1989 |

|

SU1793546A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

ПРЕОБРАЗОВАТЕЛЬ И -РАЗРЯДНОГО ДВОИЧНОГО ЧИСЛА В ЕГО ПРЕДСТАВЛЕНИЕ ПО МОДУЛЮ М , содержащий триггер з-нака, вход которого является входом знака преобразователя, входной регистр, состоящий из К + 1 групп по 1п

ji.w

I 1

I I М I T

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| «РЕОБР'АЗОВАТеЛЬ ДВОИЧНОГО КОДА - | 0 |

|

SU374596A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Трубчатая стержневая конструкция | 1988 |

|

SU1513102A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-28—Публикация

1982-06-02—Подача