единичным входом первого триггера, нулевой вход которого соединен с выходом одновибратора, выход которого также соединен с входом установки в нуль второго счетчика и входом первого элемента задержки, а вход - с (k+t)-biM выходом второго дешифратора.

2, Устройство по п,1 о т л и мающееся тем, что пересчетная схема содерж1 т счетчик, счетный вход которого является входом пересчетной схемы, а вход установки в нуль соединен с выходом пересчетной схемы и выходом одновибратора, вход которого соединен с выходом элемента И, входы которого соединены с соответствующими выходами счетчика и входами дешифрато ра, выходы которого соединены с группой выходов пересчетной схемыо

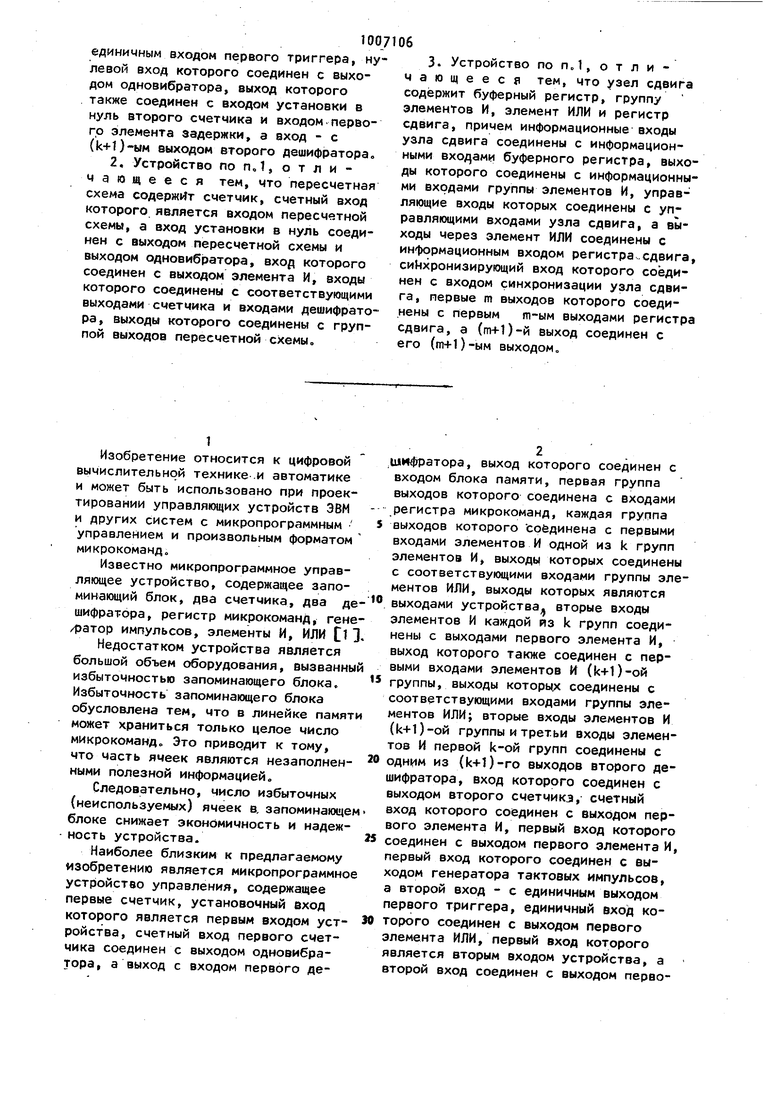

3. Устройство по п„1, о т л и чающееся тем, что узел сдвига содержит буферный регистр, группу элементов И, элемент ИЛИ и регистр сдвига, причем информационные входы узла сдвига соединены с информационными входами буферного регистра, выходы которого соединены с информационными входами группы элементов И, управляющие входы которых соединены с управляющими входами узла сдвига, а выходы через элемент ИЛИ соединены с информационным входом регистра .сдвига, синхронизирующий вход которого соединен с входом синхронизации узла сдвига, первые m выходов которого соединены с первым т-ым выходами регистра сдвига, а (т+1)-й выход соединен с его (т+1)-ым выходом„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1007107A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1008742A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1092505A1 |

1 .МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый счетчик, установочный вход которого подключен к адресному входу устройства, счетный вход первого счетчика соединен с выходом одновибратора, а выход - с входом первого дешифратора, выход которого соединен с адресным входом блока памяти, первая группа выходов которого соединена с входами регистра микрокоманд, i группа (, К - число целых микрокоманд в линейке), выходов которого .соединена с первыми входами элементов И i-ой группы, выходы которых соединены с соответствующими входами элементов ИЛИ группы, выходы которых подключены к операционному выходу устройства, вторые входы элементов И i-ой группы соединены с выходом первого элемента И, с первыми входами элементов И ()-oй группы, выходы которых соединены с .соответствующими входами элементов ИЛИ группы, вторые входы элементов И ()-oй группы и третьи входы элементов И Цk-oй групп соединены соответственно с выходами второго дешифратора. вход которого соединен с выходом второго сметчика, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора тактрвых импульсов, а второй вход - с единичным выходом первого триггера, единичный вход которого соединен с выходом первого элемента ИЛИ,- первый вход которого соединен с входом пуска устройства, а второй вход соединен с выходом первого элемента задержки; пересчеТную схему, второй элемент И, второй элемент задержки, отличающийся тем, что, с целью сокращения оборудования, оно дополнительно содержит генератор импульсов (Л сдвига, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с единичным выходом второго триггера, а С. . выход - со счетным входом пересчетной схемы и входом синхронизации узла сдвига, информационные входы которого соединены с второй группой выходов блока памяти, управляющие входы узла ч| сдвига соединены с группой выходов пересчетной схемы, m выходов - с треО тьими входами элементов И (k+l)-oй о группы (т-разрядность микрокоманды), а (т+1)-ый выход - с четвертыми входами элементов И (Я+1)-ой группы, входом второго элемента задержки и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом пересчетной схемы, а выход - с нулевым входом второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом второго элемента задержки, а второй вход - с

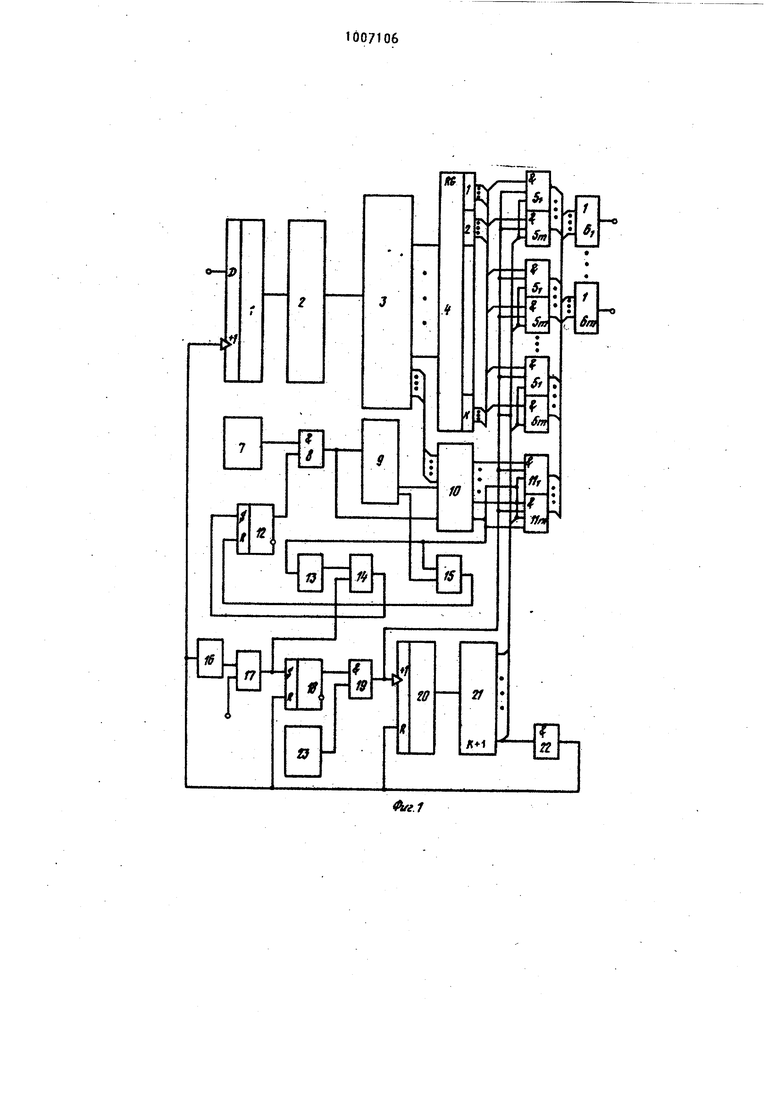

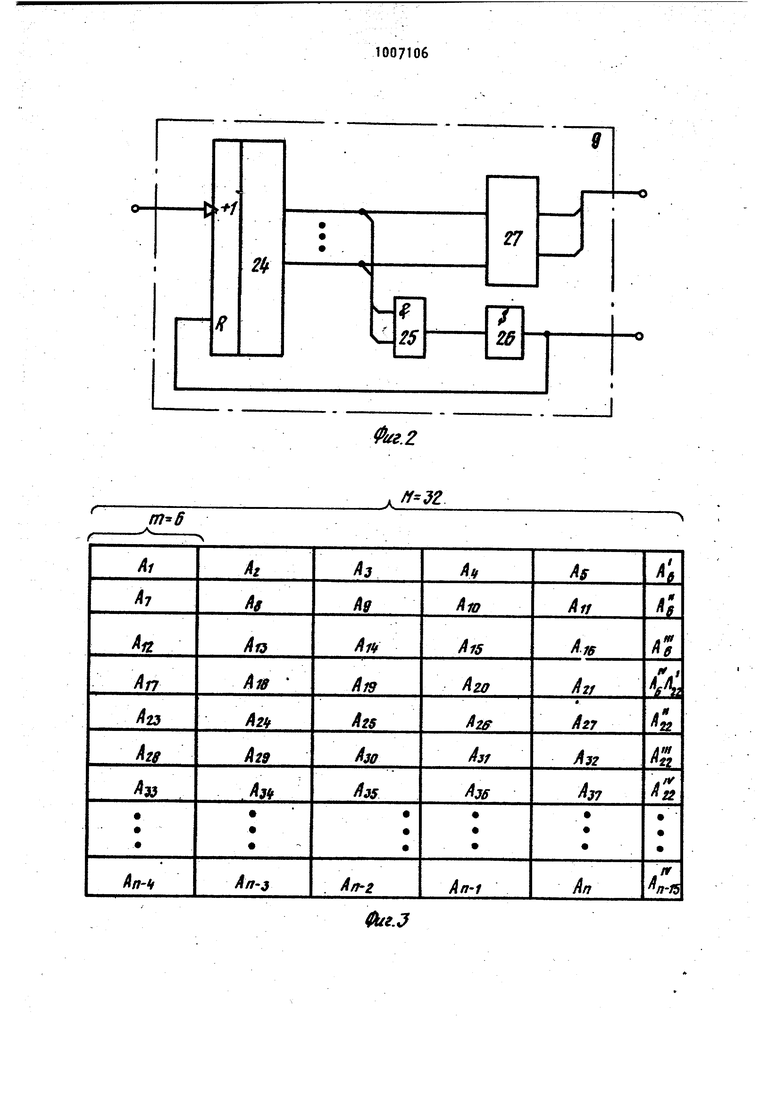

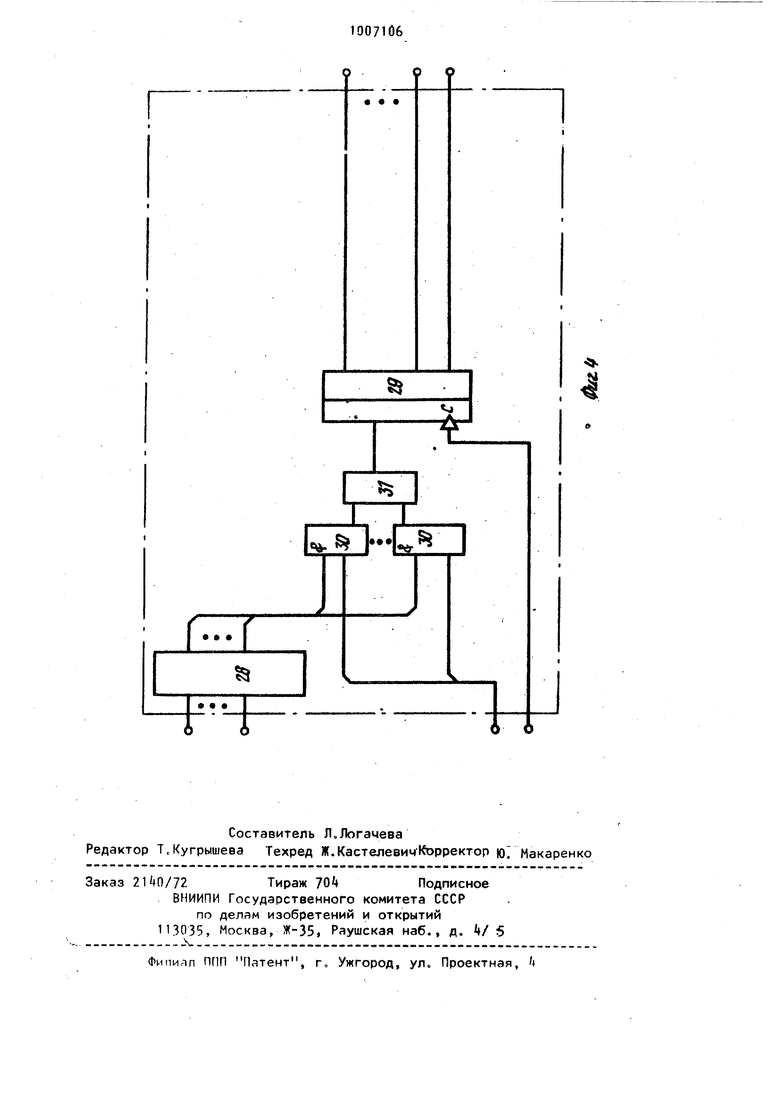

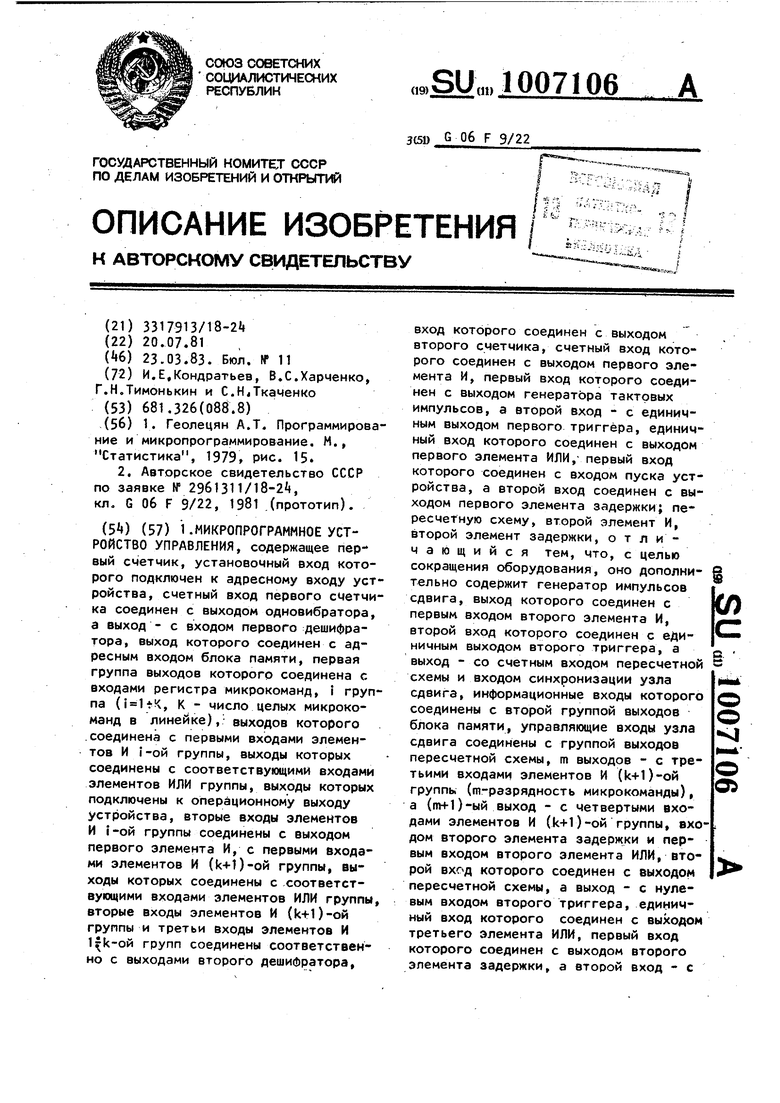

Изобретение относится к цифровой вычислительной технике .и автоматике и может быть использовано при проектировании управляющих устройств ЭВМ и других систем с микропрограммным управлением и произвольным форматом микрокоманд. Известно микропрограммное управляющее устройство, содержащее запоминающий блок, два счетчика, два де шифратора, регистр микрокоманд, гене /ратор импульсов, элементы И, ИЛИ 1 3 Недостатком устройства является большой объем оборудования, вызванны избыточностью запоминающего блока. Избыточность запоминающего блока обусловлена тем, что в линейке памят может храниться только целое число микрокоманд. Это приводит к тому, что часть ячеек являются незаполненными полезной информациейо Следовательно, число избыточных (неиспользуемых) ячеек в. запоминающе блоке снижает экономичность и надежность устройства. Наиболее близким к предлагаемому изобретению является микропрограммно устройство управления, содержащее первые счетчик, установочный вход которого является первым входом устройства, счетный вход первого счетчика соединен с выходом одновибратора, а выход с входом первого деифратора, выход которого соединен с входом блока памяти, первая группа выходов которого соединена с входами регистра микрокоманд, каждая группа выходов которого соединена с первыми входами элементов И одной из k групп элементов И, выходы которых соединены с соответствующими входами группы элементов ИЛИ, выходы которых являются выходами устройства; вторые входы элементов И каждой из k групп соединены с выходами первого элемента И, выход которого также соединен с первыми входами элементов И (k+1)-oй группы, выходы которых соединены с соответствующими входами группы элементов ИЛИ; вторые входы элементов И )-oй группы и третьи входы элементов И первой k-ой групп соединены с одним из (k+l)-ro выходов второго дешифратора, вход которого соединен с выходом второго счетчика, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а второй вход - с единичным выходом первого триггера, единичный вход которого соединен с выходом первого элемента ИЛИ, первый вход которого является вторым входом устройства, а второй вход соединен с выходом первого элемента задержки, пересметную схему, второй.элемент И, второй ИЛИ, второй элемент задержкиГ21. В известном устройстве вследствие низкой гибкости структуры используется не весь объем блока памяти для хра нения микрокоманд и имеется большая аппаратурная избыточность всего устройства. Это обуславливает его низкую экономичность и сужает область целесообразного применения Целью изобретения является сокращение оборудования устройства Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее первый счетчик, установочный вход которого соединен с адресным входом устройств, счетный вход первого счетчика соединен с выходом одновибратора, а выход - с входом первого дешифратора, выход которого соединен с адресным входом блоторого соединена с входами регистра микрокоманд, i группа (, К - чис ло целых микрокоманд в линейке) выходов которого соединена с первыми входами элементов И i-ой группы, выходы которых соединены с соответствующими входами элементов ИЛИ группы, выходы которых подключены к операционному выходу устройства, вторые входы элементов И i-ой группы соединены с выходом первого элемента И, с первыми входами элементов И (и+1)-ой группы, выходы которых соединены с соответствующими входами элементов ИЛИ группы, вторые входы элементов И (k+1)-oй группы и третьи входы элементов И lrK-ой групп- соединены соответственно с выходами второго дешифратора, вход которого соединен с выходом второго счетчика, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, а второй вход - с единичным входом первого триггера, единичный Ьход которог соединен с выходом первого элемента ИЛИ, первый вход которого соединен с входом пуска устройства, а второй вхо соединен с выходом первого элемента задержки; пересчетную схему, второй элемент И, второй элемент ИЛИ, второй элемент задержки, дополнительно содер жит генератор импульсов сдвига, выход которого соединен с первым входом вто рого элемента И, второй вход которого соединен с единичным выходом второго 100 64 . триггера, а выход - со счетным в(oдoм пересчетной схемы и входом синхронизации узла сдвига, информационные входы которого соединены с второй группой выходов блока памяти, управляющие входы узла сдвига соединены с группой выходов пересчетной схемы, m выходов - с третьими входами элементов И (k+1)-oй группы, (т- разрядность микрокоманды) а (т+1)-ый выход - с четвертыми входами элементов И (К+1)-ой группы, входом второго элемента задержки и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом пересчетной схемы, а выход - с нулевым входом второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом второго элемента задержки, а второй вход - с единичным входом первого триггера, нулевой вход Которого соединен с выходом одновибратора, выход которого также соединен с входом установки в нуль второго счетчика и входом первого элемента задержки, а вход - с (k+1)-ым выходом второго дешифратора. Кроме того, пересчетная схема содержит счетчик, счетный вход которого является входом пересчетной схемы, а вход установки в нуль соединен с выходом пересчетной схемы и выходом одновибратора, вход которого соединен с выходом элемента И, входы которого соединены с ;соответствую1цими выходами счетчика и входами дешифратора, выходы которого соединены, с группой выходов пересчетной схемы. Кроме того, узел сдвига содержит буферный регистр, группу элементов И, элемент ИЛИ и регистр сдвига, причем информационные входы узла сдвига соединены с информационными входами буферного регистра, выходы которого соединены с информационными входами группы элементов И, управляющие входы которых соединены с управляющими входами узла сдвига, а выходы-через элемент ИЛИ соединены с информационным входом регистра сдвига, синхронизирующий вход которого соединен с входом синхронизации узла сдвига, первые m выходов которого соединены с первым рп-ым выходами регистра сдвига, а (т+1)-й выход соединен с его (т+1)-ым выходом. ная схема предлагаемого микропрограммного устройства; на фиг.2 - функциональная схема пересчетной схемы; на фиг.З вариант упаковки блока памяти при длине линейки блока памяти М 32 и длине микрокоманды m 7; на фиго - функциональная схема узла сдвига Предлагаемое устройство содержит первый счетчик 1, первый дешифратор 2, блок 3 памяти, регистр k, k групп элементов И 5, группу элементовИЛИ 6, генератор 7 импульсов сдвига , второй элемент И 8, пересчетную схему 9, узел 10 сдвига,(К+Т)-|6группу элемен- ; тов И 11 ,второй триггер 12, второй элемент. 13 задержки, третий элемент ИЛИ 1 второй элемент ИЛИ 15 первый элемент 16 задержки, первый элемент ИЛИ 17, первый триггер 18, первый элемент И 19, второй счетчик 20j второй дешифратор 21, одновибратор 22, гене ратор 23 тактовых импульсов Ио - Пересчетная схема содержит счетчик 2А, элемент И 25, одновибратор 2 дешифратор.27. На фиг.З AJJ - i-я микрокоманда, AJ , Ау, AJ-, j-я микрокоманда, за писанная по частям; п - количество микрокоманд, записанных в блоке памяти,, Узел сдвига содержит буферный регистр 28, регистр 29 сдвига, группу элементов И 30, элемент ИЛИ 31. Предлагаемое устройство работает следующим образом На вход устройства поступает начальный адрес, по которому счетчик 1 и дешифратор 2 выбирают в блоке 3 памяти нужную линейку с микрокомандами, С блока 3 памяти цель1е микрокоманды переписываются в регистр k, а часть микрокоманды переписывается в первые разряды регистров 29 Сигнал поступающий на другой вход устройства, проходит через элемент ИЛИ 17 и поступает на единичный вход триггера Т8. Сигналом триггер устанавливается в единицу, а с выхода элемента ИЛИ 17 через элемент ИЛИ I также устанавливается в единицу триггер 12. Сигнал с его единичного выхода разрешает прохождение импульсов сдвига с генератора 7 через элемент И 8. Импульсы сдвига поступают на синхронизирующий вход узла 10 и сдвигают информацию в регистре 29. Эти импульсы поступают также на счетный вход счетчика 24. „ и когда их количество будет равно числу разрядов в части микрокоманды,записанной в линейке, на выходе элемента И 25 выявляется сигнал Этот сигнал поступает на вход одновибратора 26, который вырабатывает импульСс Этот импульс устанавливает в нуль счетчик 24. а также через элемент ИЛИ 15 поступает на нулевой вход триггера 12о Триггер 12 запрещает прохождение импульсов сдвига, и информация в узле 10 не сдвигается,, Сигнал с триггера 18 разрешает прохождение тактовых импульсов с генератора 23 через элемент И 19 на счетный вход счетчика 20. По состоянию счетчика 20 дешифратор поочередно считывает микрокоманды через группы элементов И 5 и группу элементов ИЛИ, при наличии тактового импульса с выхода элемента И 19 на втором входе элементов И 5 в порядке очередности считываются все k микрокоманд. Если в регистре 10 полной микрокоманды нет, о чем говорит отсутствие метки на (т+1)-ом выходе узла 10, то по сигналу на (k-i-l)-OM выходе дешифратора 21 одновибратор 22 формирует импульс, который устанавливает счетчик 20 и триггер 18 в нуль, увеличивает содержимое счетчика 1 и поступает на вход элемента 16 задержки Если же в узле 10 записана полностью микрокоманда, о чем свидетельствует метка на (т+1)-ом выходе, то по сигналу с (k+1)-ro выхода дешифратора 21 считывается микрокоманда По содержимому счетчика 1 дешифратор 2 в блоке 3 памяти выбирает следуюущую линейку с микрокомандами. Целые микрокоманды с блока 3 памяти переписываются в регистр , а часть микрокоманды - в следующие разряды регистра 29. При этом задержанный импульс от одновибратора 22 с выхода элемента задержки через элементы ИЛИ 17 и 14 устанавливает в единичное состояние триггер 12, а также триггер 18 и производит .сдвиг информации в узле 10, при этом осуществляется считывание микрокоманд, как было описано выше. В .процессе работы устройства может возникнуть случай, когда на (пн-1)-ом выходе регистра 10 появляется метка. И счётчик 9 еще не установлен в нуль Тогда метка с (гтн-1)-го выхода регистра 10 через элемент ИЛИ 15 устанавливает триггер 12 в нуль, тем самым запрещая прохождение импульсов сдвига с генератора 7 через элемент И 8, и сдвиг информации. Содержимое счетчика 9 не изменяется. После того, как счи- $ таны все k микрокоманд, с регистра 10 считывается (kt1)-я микрокоманда. Метка, задержанная элементом 13 задержки, через элемент ИЛИ 14 поступает на единичный вход триггера 12. Триггер 12 разрешает прохождение импульсов сдвига через элемент И 8. Счетчик 2 продолжает считать импульсы И при наличии сигналов на всех входах элемента И 25, одновибратор формирует импульс. Далее устройство работает аналогично описанному выше.

Выигрыш в объеме полезноиспользуемого оборудования предлагаемого устройства по сравнению с известным оценивается выражением

-n, .,

dV.5 100«ai|Ji. а по отношению к базовому объекту 25%.

г.д

bSJ lis5

r-r

r--i

Авторы

Даты

1983-03-23—Публикация

1981-07-20—Подача