(5) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1008742A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1007107A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1151960A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Устройство для контроля микропрограмм | 1982 |

|

SU1034042A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

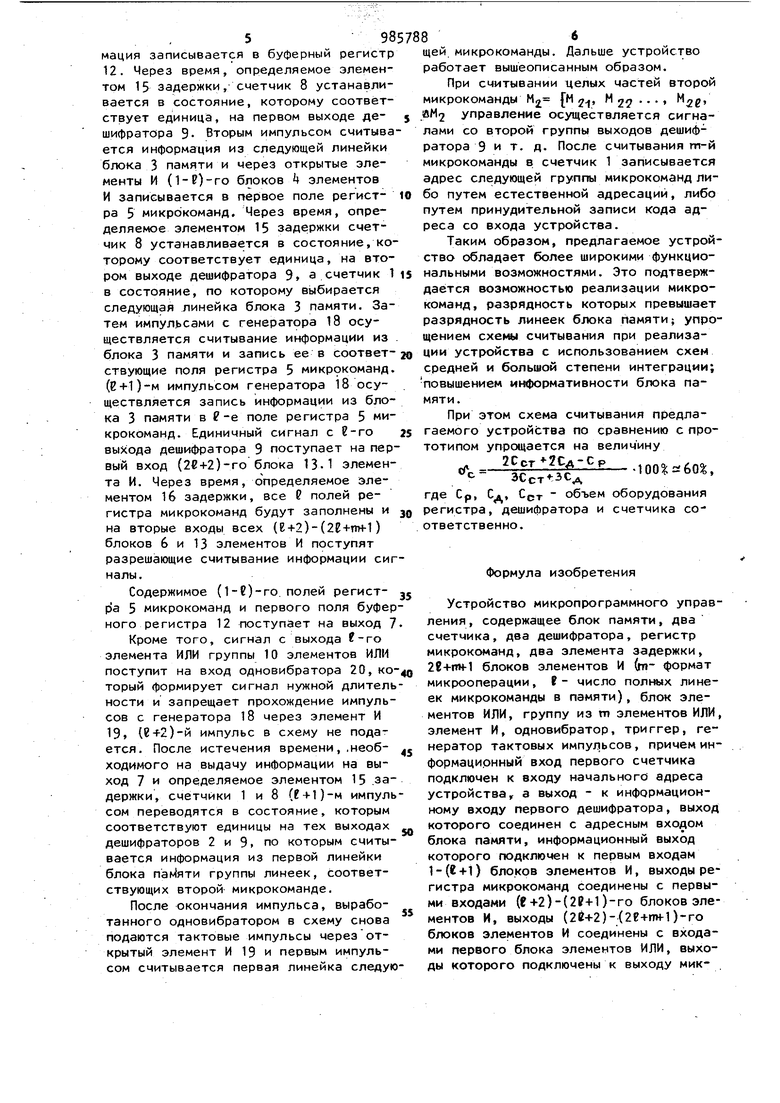

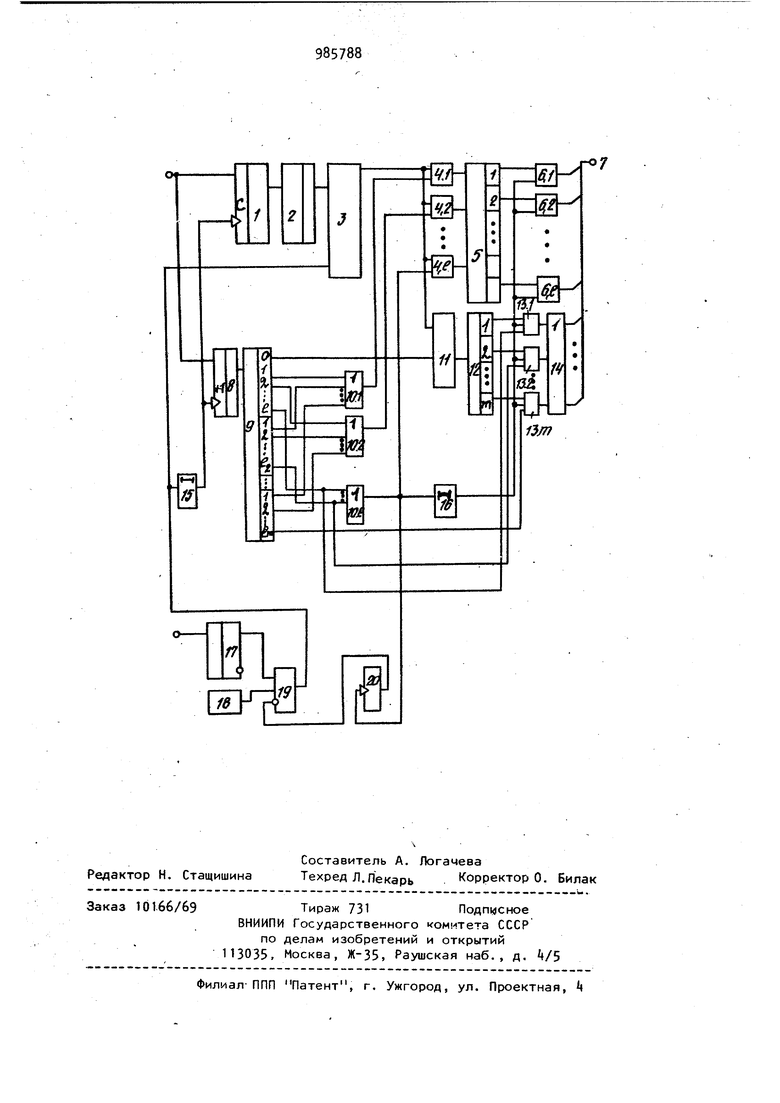

Изобретение относится к вычисли гельной технике и может быть исполь зовано при синтезе устройств для ЦВМ. Известно устройство микропрограммного управления, содержащее запоминающий блок, два счетчика, два дешифратора, регистр микрокоманд, генератор импульсов, группу из (К+1) блоков элементов И, блок элементов ИЛИ tl IIНедостатком данного устройства является низкая экономичность запоминающего блока, обусловленная тем, что в ячейке запоминающего блока может храниться только целое число микрокоманд. Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство микропрограммного управления,, содержащее блок памяти, два счет чика, два дешифратора, регистр микрокоманд, два элемента задержки, 2E+im+1 блок элементов И, блок элементов ИЛИ, группу из тп элементов ИЛИ, элемент И, одновибратор, триггер, генератор тактовых импульсов 2. Недостатком данного устройства являются низкие функциональные возможности , которые обусловлены невозможностью реализации микропрограмм, состоящих из микрокоманд, разрядность которых больше длины линеек блока памяти , причем остаток целой микрокоманды должен не превышать половину длины формата микрокоманды; невозможностью управления операционными устройствами большой размерности, т. е. операционными устройствами, для которых в каждом такте работы необходимо формировать большое число управляющих воздействий (микроопераций), в каждом такте устройство может выдавать микрокоманды, общее число разрядов которых меньше длины линейки на разрядность остатков; сложностью схем считывания , что ведет к снижению отказоустойчивости в целом и усложняет процесс производства таких устройств в 3985 интегральном исполнении; сложностью модификации схемы при изменении параметров микролрограммы. Цель изобретения - расширение функциональных возможностей устройства, Поставленная цель достигается тем, чтб в устройство, содержащее блок памяти, два счетчика, два дешифратора, регистр микрокоманд, два элемента задержки, 2K+mf1 блок элементов И (тформат микрооперации, й- число полных линеек микрокоманды в памяти), блок элементов ИЛИ, группу из m элементов ИЛИ, ;элемент И, одновибратор триггер, генератор тактовых импульсов причем информационный вход первого счетчика подключен к входу начального адреса устройства, а выход соединен с информационным входом первого дешифратора, выход которого соединен с адресным входом блока памяти, информационный выход которого соединен с первыми входами 1 (С+1) блоков элементов И, выходы регистра микрокоманд соединены с первыми входами (+2)-(2ё+1)-го блоков элементов И, выходы (2Е+2)-( )-го блоков элементов И соединены с входами первого блока элементов ИЛИ, выходы которого подключены к выходу микрооперации устройства, единичный вход триггера подключен к входу пуска устройства, единичный выход - к первому входу элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход элемента И соединен через первый элемент задержки со счетным входом второ го счетчика, выход которого соединен с входом второго дешифратора, первый выход которого соединен с вторым входом (Е+1)-го блока элементов И, допол нительно введены буферный регистр, причем установочный вход второго счет чика соединен с входом начального адреса устройства, 1 и выход () j-й группы выходов второго дешифратора () подключены к у-му входу f-ro элемента ИЛИ группы, выходы кото рых подключены к вторым входам i-ro блока .элементов И, выход которого соединен с входом регистра микрокоманд S-e выходы j-й группы выходов второго дешифратора соединены соответственно с первыми входами (2K+2)-(2e+mf 1)-го блоков элементов И, выход б-го элемента ИЛИ группы соединен через одновибратор с инверсным входом элемента И, выход которбго соединен с управляющим входом блока памяти и через эленент задержки со счетным входом первого счетчика, выход -го элемента ИЛИ группы соединен через элемент задержки с вторыми входами (В+2)-(5Р+ -НГН-1)-го блоков элементов И; выходы (Р+2)-(2Р+1 )-го блоков элементов И подключены к выходу микроопераций устройства; выход (Р+1)-го блока элементов И соединен с информационным входом буферного регистра, выходы которого соединены стретьими входами (2е+2)-(2P+rm-1 )-го блоков элементов И. Сущность изобретения состоит в повышении экономичности блока памяти устройства управления путем записи отдельных микрокоманд любого формата р линейки памяти, в том числе и микрокоманд с форматом, превышающим размер линейки, а остатков различной длины, не вошедших в эти линейки, в отдельные ячейки, На чертеже представлена функциональная схема устройства, / Устройство содержит первый сметчик 1, первый дешифратор 2, блок 3 памяти, (1-Р)-й блок элементов И, регистр 5 микрокоманд, (+2)-( )-й блок 6 элементов И, выход 7 микроопераций устройства, второй счетчик 8, второй дешифратор 9 группа 10 элементов ИЛИ, (е+1)-й блок элементов И 11, буферный регистр 12, (22+2)-(26+ +Гп+1)-й блоки 13 элементов И, блок 1 элементов ИЛИ, первый элемент 15 задержки, второй элемент 16 задержки, триггер 17, генератор 18 тактовых импульсов, элемент И 19, одновибратор 20, В исходном состоянии оба счетчика 1 и 8 и триггер 17 находятся в нулевом состоянии, элемент И 19 закрыт, регистры микрокоманд 5 и буферный 12 свободны. Предлагаемое устройство работает следующим обр-азом. По начальному адресу, поступающему на первый вход счетчика 1 и вход счетчика 8 на первом дешифраторе 2 возбуждается выход, соответствующий начальному адресу, а на втором .дешифраторе 9 нулевой выход. Сигналом Пуск fpиггep 17 устанавливается в единичное состояние, разрешая прохождение импульсов с генератора 18 через элемент И 19. Г1ервый импульс разрешает считывание информации с начальной ячейки блока 3 памяти. Через открытый дешифратором 9 (6 + 1)-i блок элементов И 11 эта информация записывается в буферный регистр 12. Через время, определяемое элементом IS задержки, счетчик 8 устанавливается в состояние, которому соответствует единица, на первом выходе дешифратора 9- Вторым импульсом считывается информация из следующей линейки блока 3 памяти и через открытые элементы И (1-Р)-го блоков k элементов И записывается в первое поле регистра 5 микрбкоманд. Через время, определяемое элементом 15 задержки счетчик 8 устанавливается в состояние, которому соответствует единица, на втором выходе дешифратора 9, а счетчик 1 в состояние, по которому выбирается следующая линейка блока 3 памяти. Затем импульсами с генератора 18 осуществляется считывание информации из . блока 3 памяти и запись ее в соответ-20 ции ствующие поля регистра 5 микр9команд (2+1)-м импульсом генератора 18 осуществляется запись информации из блока 3 памяти в S-е поле регистра 5 микрокоманд. Единичный сигнал с -го вывода дешифратора 9 поступает на пер вый вход (2е+2)-го блока 13.1 элемента И. Через время, определяемое элементом 16 задержки, все Р полей регистра микрокоманд будут заполнены и на вторые входы всех (Е+2)-(2 +т1Н-1) блоков 6 и 13 элементов И поступят разрешающие считывание информации си налы. Содержимое (1-С)-го. полей регистpa 5 микрокоманд и первого поля буфер ного регистра 12 поступает на выход 7 Кроме того, сигнал с выхода -го элемента ИЛИ группы 10 элементов ИЛИ поступит на вход одновибратора 20, ко торый формирует сигнал нужной длитель ности и запрещает прохождение импульсов с генератора 18 через элемент И 19, (+2)-й импульс в схему не подается. После истечения времени, ,необходимого на выдачу информации на выход 7 и определяемое элементом 15 .задержки, счетчики 1 и В (6+1)-м импуль сом переводятся в состояние, которым соответствуют единицы на тех выходах дешифраторов 2 и 9, по которым считывается информация из первой линейки блока паМяти группы линеек, соответствующих второй микрокоманде. После окончания импульса, выработанного одновибратором в схему снова подаются тактовые импульсы через открытый элемент И 19 и первым импульсом считывается первая линейка следую

щей микрокоманды. Дальше устройство работает вышеописанным образом.

При считывании целых частей второй микрокоманды Мз у,

2 1 21 М 25 . . . Mjg,

вМ2 управление осуществляется сигналами со второй группы выходов дешифратора 9 и т. д. После считывания т-й микрокоманды в счетчик 1 записывается адрес следующей группы микрокоманд либо путем естественной адресаций, либо путем принудительной записи кода адреса со входа устройства.

Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями. Это подтверждается возможностью реализации микрокоманд, разрядность которых превышает разрядность линеек блока памяти; упрощением схемы считывания при реализаустройства с использованием схем средней и большой степени интеграции; повышением информативности блока памяти. При этом схема считывания предлагаемого устройства по сравнению с прототипом упрощается на величину ( ст гСд-Ср inn°, , где Ср, Сд, CCT объем оборудования регистра, дешифратора и счетчика соответственно. Формула изобретения Устройство микропрограммного управления , содержащее блок памяти, два счетчика, два дешифратора, регистр микрокоманд, два элемента задержки, 28+ГТН-1 блоков элементов И 6п- формат микрооперации, t- число полных линеек микрокоманды в памяти), блок элементов ИЛИ, группу из m элементов ИЛИ, элемент И, одновибратор, триггер, генератор тактовых импульсов, причем информационный вход первого счетчика подключен к входу начального адреса устройства у а выход - к информационному входу первого дешифратора, выход которого соединен с адресным входом блока памяти, информационный выход которого подключен к первым входам 1-(2+1) блоков элементов И, выходы регистра микрокоманд соединены с первыми входами (f 4-2)-()-го блоков элементов И, выходы (2e+2)-(2e+rm-l)-ro блоков элементов И соединены с входами первого блока элементов ИЛИ, выходы которого подключены к выходу микрооперации устройства, единичный вход триггера подключен к входу пуска устройства, единичный выход - к первому входу элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход элемента И подключен через первый элемент задержки со счетным входом второго счетчика, выход которого соединен с входом второго дешифратора, первый выход которого соединен с вторым входом (+1)го блока элементов И, отличающее с я тем, что, с целью расшире,ния функциональных возможностей путем реализации микропрограмм, состоящих из микрокоманд с разрядностью, превышающей разрядность линеек блока памяти, дополнительно содержит буферный регистр, причем установочный вход второго счетчика соединен с входом начального адреса устройства,-и выход (e1-P) й группы выходов второго дешифратора () подключены к j-му входу i-го элемента ИЛИ группы, выхо|ды которых подключены к вторым входам js -го блока элементов И, выход которого подключен к входу регж;тра микро98

Источники информации, принятые во внимание при экспертизе

Of

rf

-07

4,1

a 5Т7Г

П2т:Й

/

fi

14

ItttH

м

im

Авторы

Даты

1982-12-30—Публикация

1981-07-02—Подача