элемента И, а четвертые входы - с с входами установки в нуль второго 2 - (и+1)-м выходами третьего дешиф-, счетчика и триггера и входом элемента ратора, выход одновибратора соединен задержки.

10087 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1981 |

|

SU1007107A1 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1007106A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1981 |

|

SU976443A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1130863A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

1

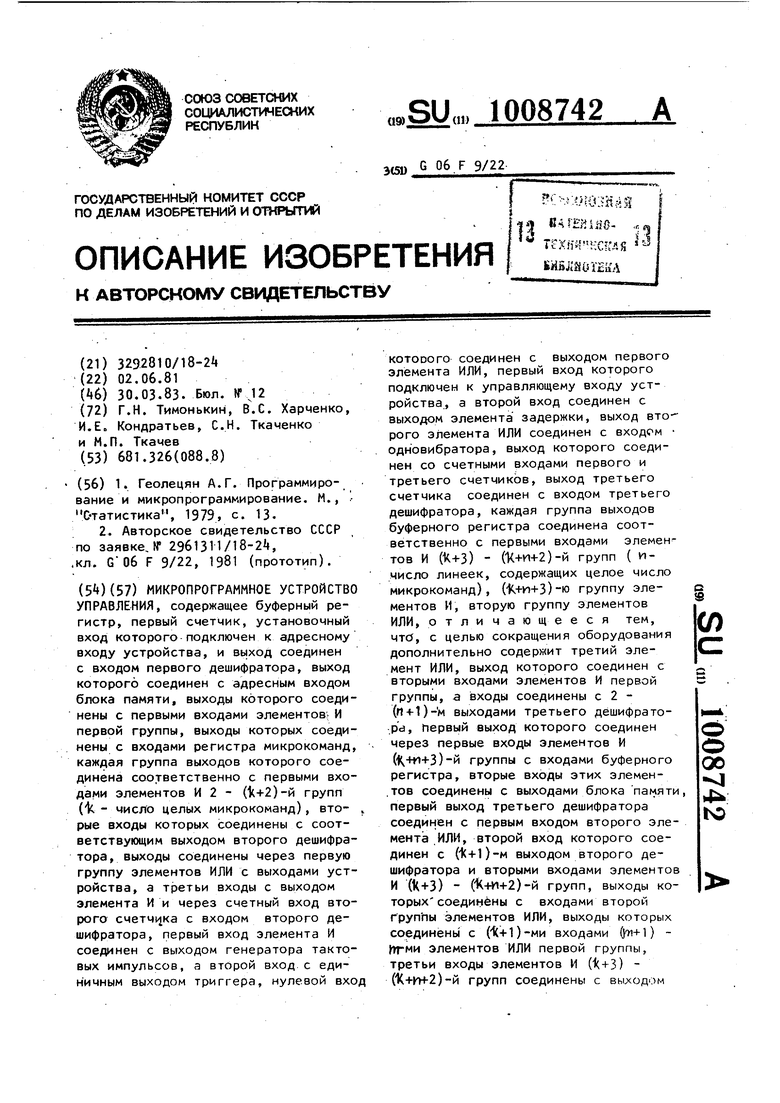

Изобретение относится к вычислительной технике и мокет быть использовано при синтезе устройств управления микропрограммных ЭВМ и других систем.

Известно микропрограммное устройсво управления, содержащее запоминают щий блок, два счетчика, два Йешифратора, регистр микрокоманд, генератор импульсов, элементы И и ИЛИ р.

Недостатком данного устройства является низкая экономичность запоминающего блока, обусловленная тем, что в линейке запоминающего блока может храниться только целое число микрокоманд.

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому являетс устройство, содержащее буферный регистр, первый счетчик, первый вход которого является первым входом уст ройства, а выход соединен с входом первого дешифратора, выход, которого соединен с входом блока памяти, выходы которого соединены с первыми входами первой группы элементов И, выходы которой соединены с входами регистра микрокоманд, каждая группа выходов которого соединена с первыми входами элементов И соответствующей группы 2 - {1ч-2)-й групп элементов И, вторые входы элементов И ;которых соединены с одним из выходов второго дешифратора, выходы соединены через первую группу элеменТО8 ИЛИ с выходами устройства, а третьи входы - с выходом элемента И, а черезСчетный вход второго счет чика с входом второго дешифратора, первый вход элемента И соединен с выходом генератора, а второй вход с единичным выходом триггера, нулевой вход которого соединен с выходом пер вого элемента ИЛИ, первый вход которого является вторым входом устройства, а второй вход соединен с выходом элемента задержки, выход второго элемента ИЛИ соединен с входом одновибратора, выход которого соединен с счетными входами первого и третьего счетчиков, выход третьего счетчика соединен с входом третьего дешифратора, каждая группа выходов буферного регистра соединена с первым входом элемента И соответствующей группы (1(+3) - ((2)-й групп элементоб И, (1(+и+3)-ю группу элементов И, вторую-группу элементов ИЛИ 2.

Недостатками данного устройства являются низкая экономичность и низкая универсальность. Низкая экономичность: обусловлена тем, что используются не все свободные ячейки памяти в линейке блока памяти. В зависимости от разрядности микрокоманды и разрядности линейки блока памяти может возникнуть три варианта упаковки информации в блоке памяти.

1-й вариант. Если разрядность линейки блока памяти равна целому числу форматов микрокоманд, то все ячейки блока памяти заполнены информацией.

2-й вариант. Если разрядность линейки блока памяти равна не целому числу форматов микрокоманд и число свободных ячеек меньше, чем половина формата микрокоманды, то устройство позволяет полностью заполнить все ячейки блока памяти информацией.

3-й вариант. Часто встречается случай, когда формат линейки блока памяти равен нецелому числу форматов микрокоманд и число свободных ячеек больше половины длины микрокоманды. Тогда в данном устройстве информация записывается в те ячейки, в которые помещается целое число микрокоманд и часть микрокоманд, меньшая, чем половина ее длины. Остальные ячейки блока памяти остаются свободными, незаполненными информацией и используются неэффективно.

Цель изобретения - сокращение оборудования .

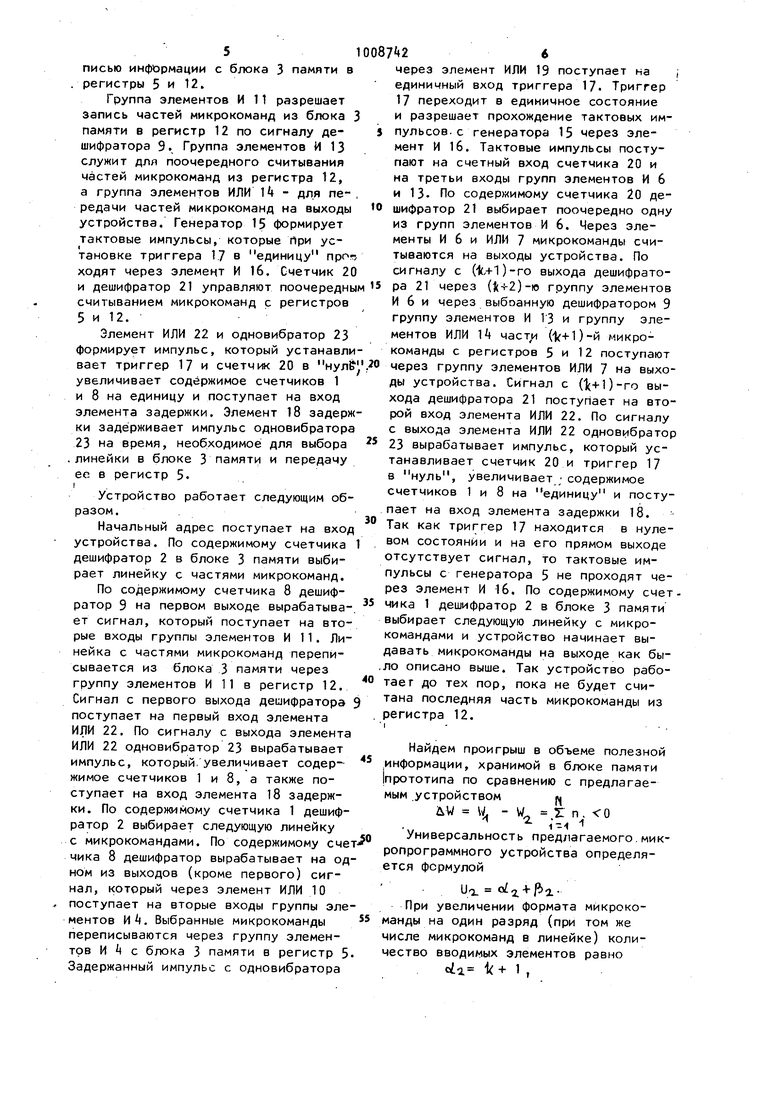

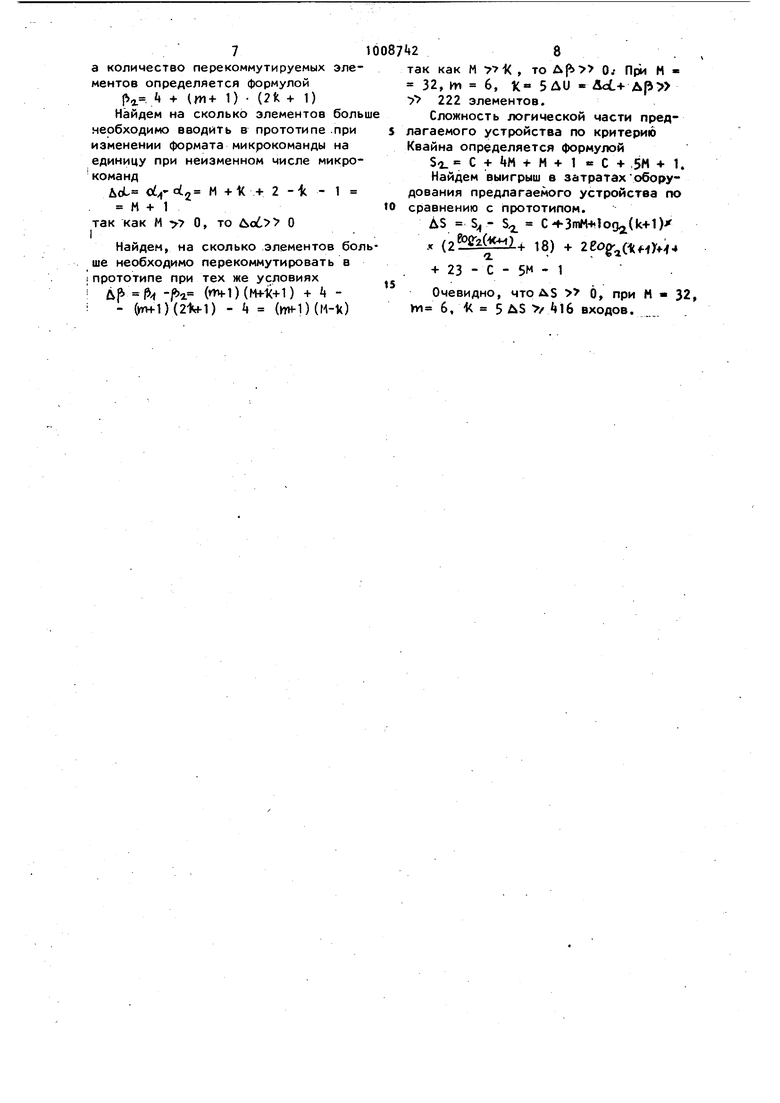

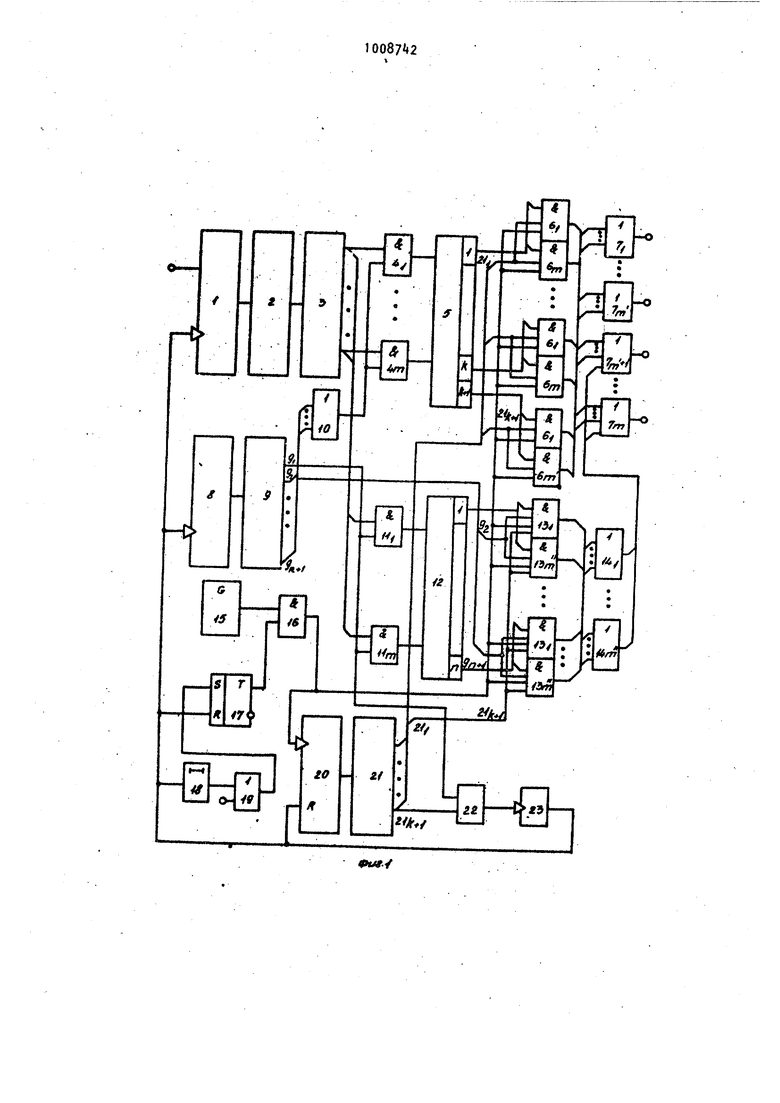

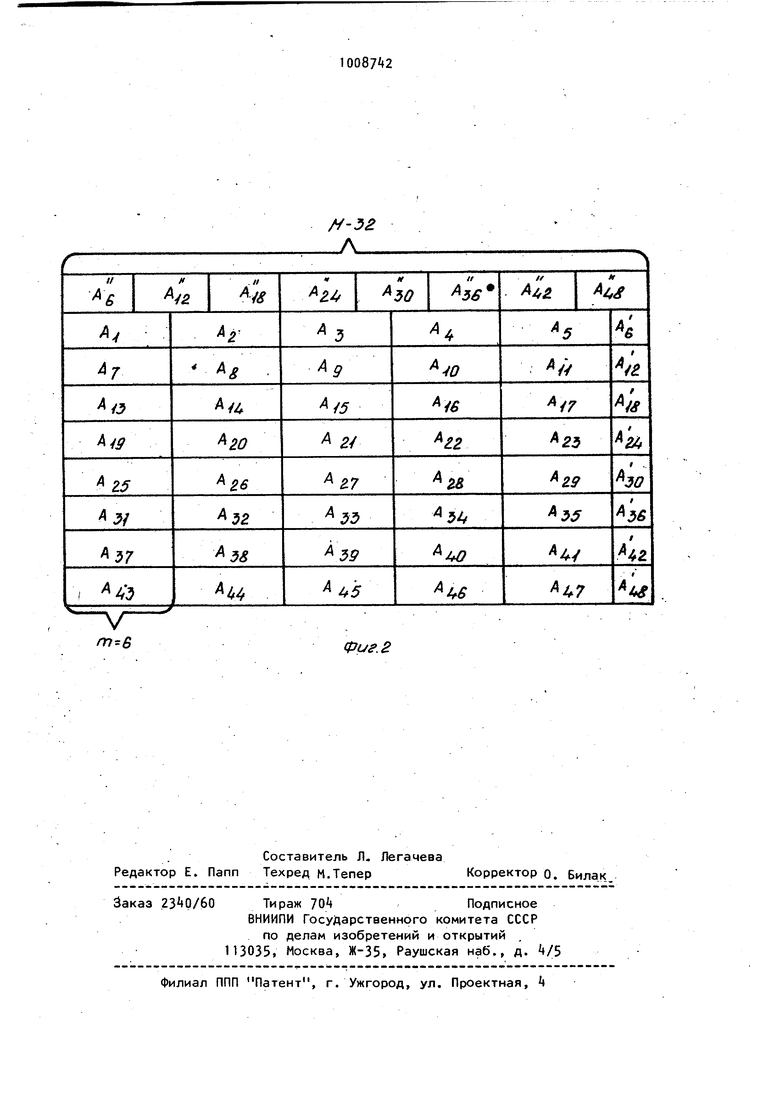

Поставленная цель достигается .тем что устройство, содержащее буферный регистр, первый счетчик, установочный вход которого подключен к адресному входу устройства, а выход соединен с входом первого дешифратора, выход которого соединен с адресным входом блока памяти, выходы которого соединены с первыми входами элементов И первой группы, выходы которых соединены с входами регистра микрокоманд, каждая группа выходов которого соединена соответственно с первыми входами элемента И 2 - (1(+2)-й группы (k - число целых микрокоманд вторые входы которых соединены с соответствующим выходом второго дешифратора выходы соединены через первую группу элементов ИЛИ с выходами устройства, а третьи входы с выходом элемента И и через счетный вход второго счетчика с входом второго .дешиф ратора, первый вход элемента И соединен с выходом генератора тактовых импульсов, а второй вход с единичным выходом триггера, нулевой вход которого соединен с выходом первого элемента ИЛИ, первый вход которого прдключен к управляющему входу устройст ва, а второй вход соединен с выходом элемента задержки, выхоД второго элемента ИЛИ соединен с входом од- . новибратора, выход которого соединен со счетными входами первого и третьего счетчиков, выход третьего счетчика соединен с входом третьего дешифратора, каждая группа выходов буферного регистра соединена соответственно с первыми входами элементов И (il+3) -(К+И+2)-й групп (п число линеек, содержащих целое число микрокоманд), (К+И+3)-ю группу элементов. И,. вторую группу элементов ИЛИ, дополнительно содержит третий элемент ИЛИ, выход которого соединен с вторыми входами элементов И первой группы, а входы соединены с 2 (и+1)-м выходами третьего дешифратора , первый выход которого соединен через первые вхсЗды элементов И (К+|1+3)-й группы с входами буферного регистра, вторые входы этих элементов соединены с выходами блока памяти, первый выход третьего дешифратора соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с (1(+1)-м выходом второго .дешифратора и вторыми входами элементов И (U+3) - ()-й Групп, выходы которых соединены с входами второй группы элементов ИЛИ, выходы которых соединены с (1(+1)-ми входами 1 2 (ки+1) -И1-МИ элементов ИЛИ-первой , группы, третьи входы элементов И (К+З) - ((+и+2)-й групп соединены с выходом элемента И, а четвертые вхоы - с 2 - (и+1)-ми выходами третьего дешифратора, выход одновибратора соеинен с входами установки в нуль торого счетчика и триггера и вхоом элемента- задержки. Сущность изобретения состоит в по- : ышении экономичности и универсальости путем записи частей микрокоманд, е поместившихся в линейку блока паяти, в отдельною линейку - линейку остатков. .- . На фиг. 1 изображена функциональная схема предлагаемого микропрограммного устройства; на фиг. 2 - вариант упаковки информации в блоке памяти предлагаемого микропрограммного устройства при , m 6. Предлагаемое устройство (фиг. 1). содержит первый счетчик 1, первый дешифратор 2, блок 3 памяти, первую группу элементов И , регистр 5 микрокоманд, 2 - (11+2)-ю группы элементов И 6, первую группу элементов ИЛИ 7, третий счетчик 8, третий дешифратор 9 третий элемент ИЛИ 10, (1.+и+3)-ю группу элементов И 11 буферный регистр 12 (1(+3) - (К+И+2)группу элементов И ТЗ, вторую группу элементов ИЛИ 14, генератор 15 тактовых импульсов, элемент И 16, триггер 17, элемент 18 задержки, первый элемент ИЛИ 19, второй счетчик 20, вто- . рой дешифратор 21, второй элемент ИЛИ 22, одновибратор 23. На фиг. 2 приняты следующие оботзначения: А - t-я . , „ микрокоманда; , гл- части j-й микрокоманды. Счетчик 1 и дешифратор 2 формируют адрес, по которому в блоке памяти выбирается нужная линейка с микрокомандами . В блоке памяти 3 хранятся все микрокоманды. Группа элементов И по сигналам деиифратора 9, которые собираются элементом ИЛИ 10, разрешает передачу микрокоманд из блока 3 памяти в регистр 5. В регистре 5 хранятся считываемые микрокоманды. Группы элементов И 6 служат для поочередного считывания микрокоманд из регистра 5 а группа элементов ИЛИ 7 - Для вывода микрокоманд на выходы устройства. Счетчик 8 и дешифратор 9 управляют записью информации с блока 3 памяти в регистры 5 и 12. Группа элементов И 11 разрешает запись частей микрокоманд из блока 3 памяти в регистр 12 по сигналу дешифратора 9. Группа элементов И 13 служит для поочередного считывания частей микрокоманд из регистра 12, а группа элементов ИЛИ 14 - для передачи частей микрокоманд на выходы устройства. Генератор 15 формирует тактовые импульсы, которые При установке триггера 1.7 в единицу пров ходят через элемент И 16. Счетчик 20 и дешифратор 21 управляют поочередны считыванием микрокоманд с регистров 5 и 12. Элемент ИЛИ 22 и одновибратор 23 формирует импульс, который устанавли вает триггер 17 и счетчик 20 в нул& увеличивает содержимое счетчиков 1 и 8 на единицу и поступает на вход элемента задержки. Элемент 18 задерж ки задерживает импульс одновибратора 23 на время, необходимое для выбора .линейки в блоке 3 памяти и передачу ее в регистр 5. I . . Устройство работает следующим образом. . Начальный адрес поступает на вход устройства. По содержимому счетчика дешифратор 2 в блоке 3 памяти выбирает линейку с частями микрокоманд. По содержимому счетчика 8 дешифратор 9 на первом выходе вырабатывает сигнал, который поступает на вторые входы группы элементов И 11. Линейка с частями микрокоманд переписывается из блока 3 памяти через группу элементов И 11 в регистр 12. Сигнал с первого выхода дешифратора поступает на первый вход элемента ИЛИ 22. По сигналу с выхода элемента ИЛИ 22 одновибратор 23 вырабатывает импульс, который, увеличивает содержимое счетчиков 1 и 6, а также поступает на вход элемента 18 задержки. По содержимому счетчика 1 дешифратор 2 выбирает следующую линейку с микрокомандами. По содержимому сче чика 8 дешифратор вырабатывает на од ном из выходов (кроме первого) сигнал, который через элемент ИЛИ 10 поступает на вторые входы группы эле ментов И. Выбранные микрокоманды переписываются через группу элементов И с блока 3 памяти в регистр 5 Задержанный импульс с одновибратора через элемент ИЛИ 19 поступает на ; единичный вход триггера 17. Триггер 17 переходит в единичное состояние и разрешает прохождение тактовых импульсов.с генератора 15 через элемент И 1б. Тактовые импульсы поступают на счетный вход счетчика 20 и на третьи входы групп элементов И 6 и 13- По содержимому счетчика 20 дешифратор 21 выбирает поочередно одну из групп элементов И 6. Через элементы И 6 и ИЛИ 7 микрокоманды считываются на выходы устройства. По сигналу с (1(,+1)-го выхода дешифратора 21 через (}(+2)-ю группу элементов И 6 и через выбпанную дешифратором 9 группу элементов И 13 и группу элементов ИЛИ 1А частей ()-й микрокоманды с регистров 5 и 12 поступают через группу элементов ИЛИ 7 на выходы устройства. Сигнал с )-гг выхода дешифратора 21 поступает на второй вход элемента ИЛИ 22. По сигналу с выхода элемента ИЛИ 22 одновибратор 23 вырабатывает импульс, который устанавливает счетчик 20 и триггер 17 в нуль, увеличивает ; содержимое счетчиков 1 и 8 на единицу и поступает на вход элемента задержки 18. Так как триггер 17 находится в нулевом состоянии и на его прямом выходе отсутствует сигнал, то тактовые импульсы с генератора 5 не проходят через элемент И 16. По содержимому счетчика 1 дешифратор 2 в блоке 3 памяти выбирает следующую линейку с микрокомандами и устройство начинает выдавать микрокоманды на выходе как было описано выше. Так устройство работает до тех пор, пока не будет считана последняя часть микрокоманды из регистра 12. Найдем проигрыш в объеме полезной .информации, хранимой в блоке памяти |прототипа по сравнению с предлагаемым устройством |( AW W. - W Г п. 0 i--i Универсальность предлагаемого.микропрограммного устройства определяется формулой и . При увеличении формата микрокоманды на один разряд (при том же числе микрокоманд в линейке) количество вводимых элементов равно г 1 ,

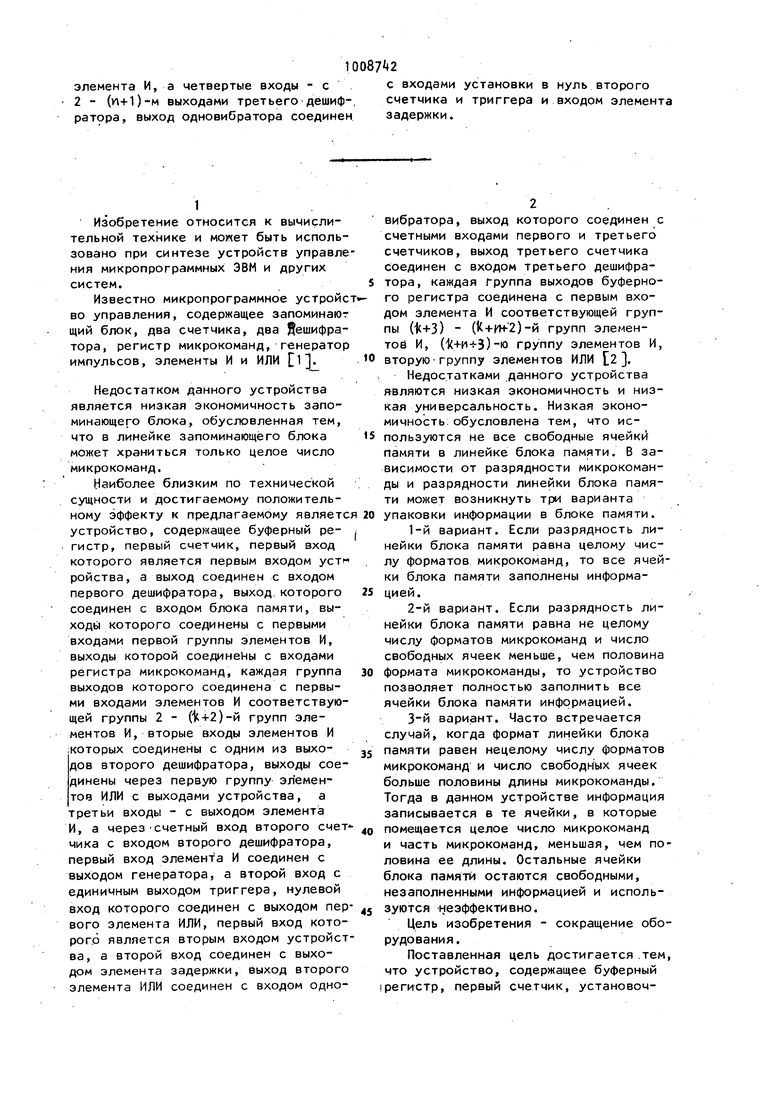

а количество перекоммутируемых элементов определяется формулой г. f + (т+ 1) ( 1) Найдем на сколько элементов боль необходимо вводить в прототипе .при изменении формата микрокоманды на единицу при неизменном числе микрокоманд

ioL М +К + 2 --k - 1

М + 1 так как М 7 О, то Доб О

Найдем, на сколько элементов болше необходимо перекоммутировать в I прототипе при тех же условиях i р -|Ьг (ть1)() + А - (rH-1)(2lw-1) - i (w1)(M-V)

так как М К , то Др 0.- При М « 32, m 6, К 5Ди « Дс(.+ др 222 элементов.

Сложность логической части предлагаемого устройства по критерию Квайна определяется формулой

$0. С + «- М + 1 С + ,5М + 1.

Найдем выигрыш в затратахоборудования предлагаемого устройства по сравнению с прототипом.

AS S - S C«-3mM-nlog2,(k+1)x

,( 18) + 2ео(КнУН4 + 23 - С 5м - 1

Очевидно, что AS 6, при

М - 32 yvi 6, -k 5 AS /Л1б входов.

/V-J

yv

m-6

Фие.В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Геолецян А.Г | |||

| Программирование и микропрограммирование | |||

| М., | |||

| Отатистика, 1979, с | |||

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке, N 2961311/18-2, .кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-03-30—Публикация

1981-06-02—Подача