и управляющим входом регистра сдвига, выход первого элемента И сое-;:динен со счетным входом счетчика, вторым входом второго элемента И и через второй элемент задержки - с вторым входом третьего элемента И, выход которого соединен с входом синхронизации регистра сдвига,вторая группа выходов блока памяти микрокоманд соединена с информационными входами регистра сдвига, первый выход которого соединен с третьим входом второго элемента И, рыходы регистра сдвига соединены соответственно с входами элемента ИЛИ-НЕ, выход,которого соединен с вторыми входами второго блока элементов И и с входом одновибратора, выход которого соединен с входами сброса счетчика и триггера, а через третий элемент задержки -С входом сброса регистра микроопераций, третий выход генератора тактовых импульсов соединен с управляющим входом блока памяти адресов микрокоманд, выходы дешифратора соединены с вторыми входами первого блока элементов И соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1151960A1 |

| Многотактное микропрограммное устройство управления | 1982 |

|

SU1094033A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1084793A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

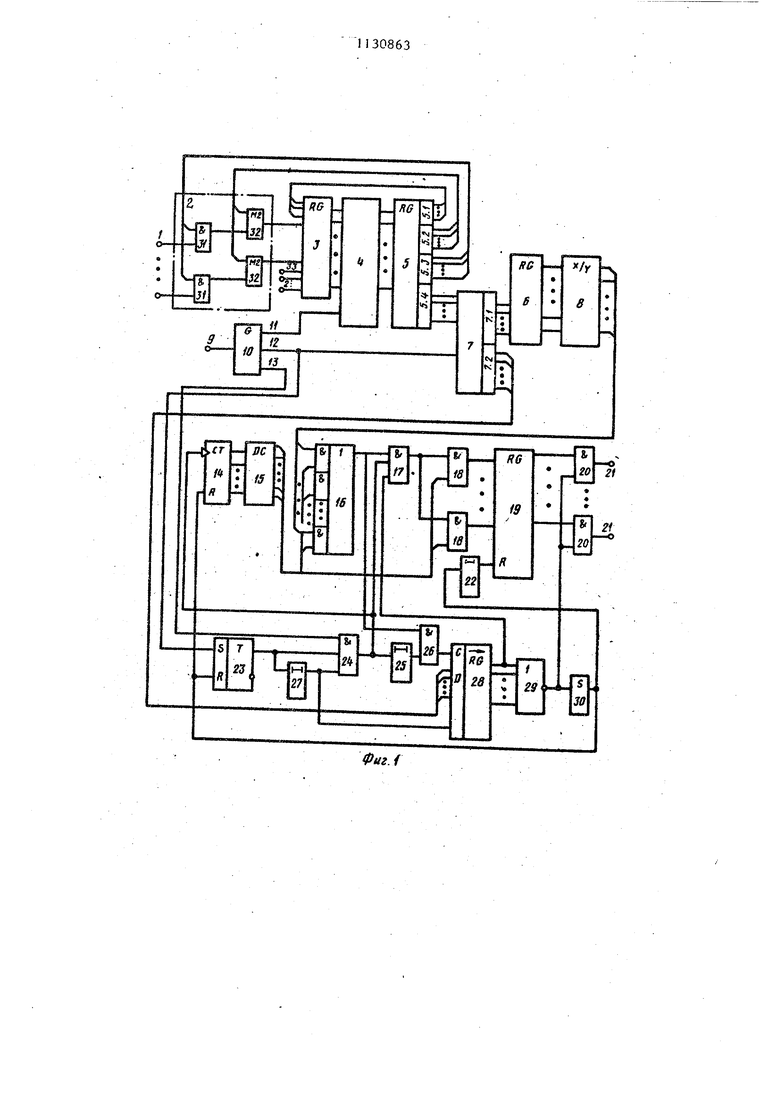

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок модификации адреса, регистр адреса, блок памяти адресов микрокоманд, регистр адреса микрокоманды, блок памяти микрокоманд, регистр микрокоманды, коммутатор, генератор тактовых импульсов, триггер, первый элемент И, счетчик, дешифратор, регистр сдвига, причем входы сигналов логических условий устройства соединены с первой группой входов блока модификации адреса, выходы которого соединены с первой группой входов регистра адреса, выходы которого соединены с адресными входами блока памяти адресов микрокоманд, выходы которого соединены с входами регистра адреса микрокоманды, первая группа выходов которого соединена с второй группой входов регистра адреса, вторая и третья группы выходов - соответственно с второй и третьей группами входов блока модификации адреса, четвертая группа выходов - с адресными входами блока памяти микрокоманд, первая группа выходов кото.юго соединена с входами регистра микрокоманды, выходы счетчика соединены соответственно, с входами дешифратора, выходы которого .соединены с.управляющими .входами коммутатора, входы кода операции устройства соединены с третьей группой входов регистра адреса, вход сигнала Пуск устройства соединен с входом генератора тактовых импульсор,, первый выход которого соединен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И, отличающее ся тем, что, с целью сокращения объема оборудования, оно содержитпервый, второй и третий элементы задержки, второй и третий элементы И, одновибратрр, эле(Л мент ИЛИ-НЕ, первый и второй блоки элементов И, регистр микроопераций, преобразователь кода микрокоманды, причем выходы регистра микрокоманды § соединены с входами преобразователя . кода микрокоманды, выходы которого соединены с информационными входами коммутатора, выход которого соединен СО с первыми входами второго и третьего элементов И, выход второго элех мента И соединен с первыми входами 01) &9 первого блока элементов И, выходы которого соединены с вхоДами регистра микроопераций, выходы которого соединены с первыми входами второго блока элементов И, выходы которого соединены с выходами микроопераций устройства, первый выход генератора тактовых импульСов соединен с единичным входом триггера, единичный выход которого соединен с вторым входом первого элемента И и чбрез первый элемент задержки - с третьим входом первого элемента И

Изобретение относится к автоматике, вычислительной технике, передаче данных и может быть использовано при проектировании микропрограммных устройств управления цифровых систем,

Известно двухуровневое микропрограммное устройство управления которое содержит два блока памяти, дешифратор, счетчик, регистр адреса, генератор тактовых импульсов, два блока элементов И, два элемента задержки, элемент ИЛИ-НЕ fl J

Недостатком указанного устройства является большая избыточность блока памяти микрокоманд, обусловленная низкой информативностью заполнения ячеек памяти.

Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является двухуровневое микропрограммное устройство управления, содержащее блок модификации адреса, регистр адреса, блок памяти адресов микрокоманд, ре гистр адреса микрокоманды, блок памти микрокоманд, регистр микрокоманды, коммутатор, генератор тактовых импульсов, триггер, первый элемент И, счетчик, дешифратор, регистр сдвига, причем входы сигналов логичких, условий устройства соединены с первой группой входов блока модификации адреса, выходы бло.ка модификации адреса соединены с адресными входами блока памяти адресов микрокоманд, выходы которого соединены с

входами регистра адреса микрокоманды, первая группа выходов которого соединена с второй группой входов регистра адреса, вторая и третья группы выходов соединены соответственно с второй и третьей группой входов блока модификации адреса, четвертая группа выходов соеди|Нена с адресными входами блока памяти микрокоманд, первая группа выходов которого - с входами регистра микрокоманды} выходы счетчика соединены с входами дешифратора, выходы которого - с управляющими входами коммутатора, выходы кода оцерации устройства соединены с третьей группой входов регистра адреса, вход сигнала Пуск соединен с входом генератора тактовых импульсов, первый выход которого соединен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И f2J.

Недостатками, ограничивающими область применения известного устройства, являются большая избыточность блока памяти микрокоманд и низкий коэффициент информативного заполнения блоков памяти.

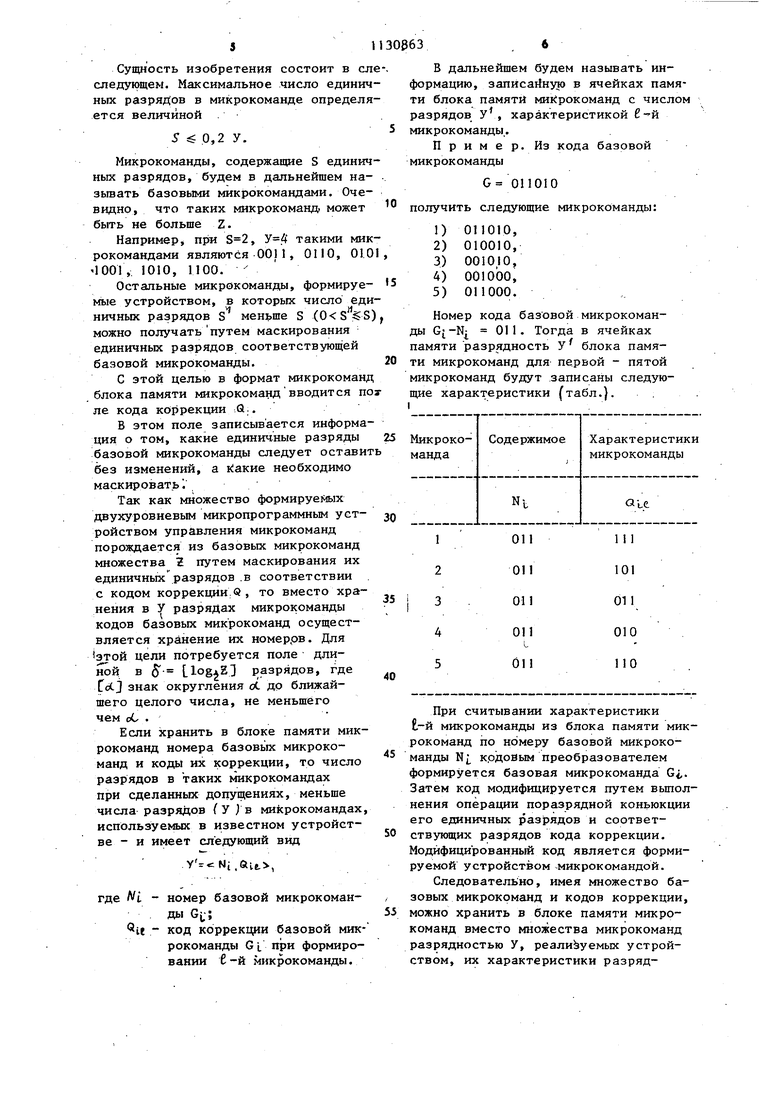

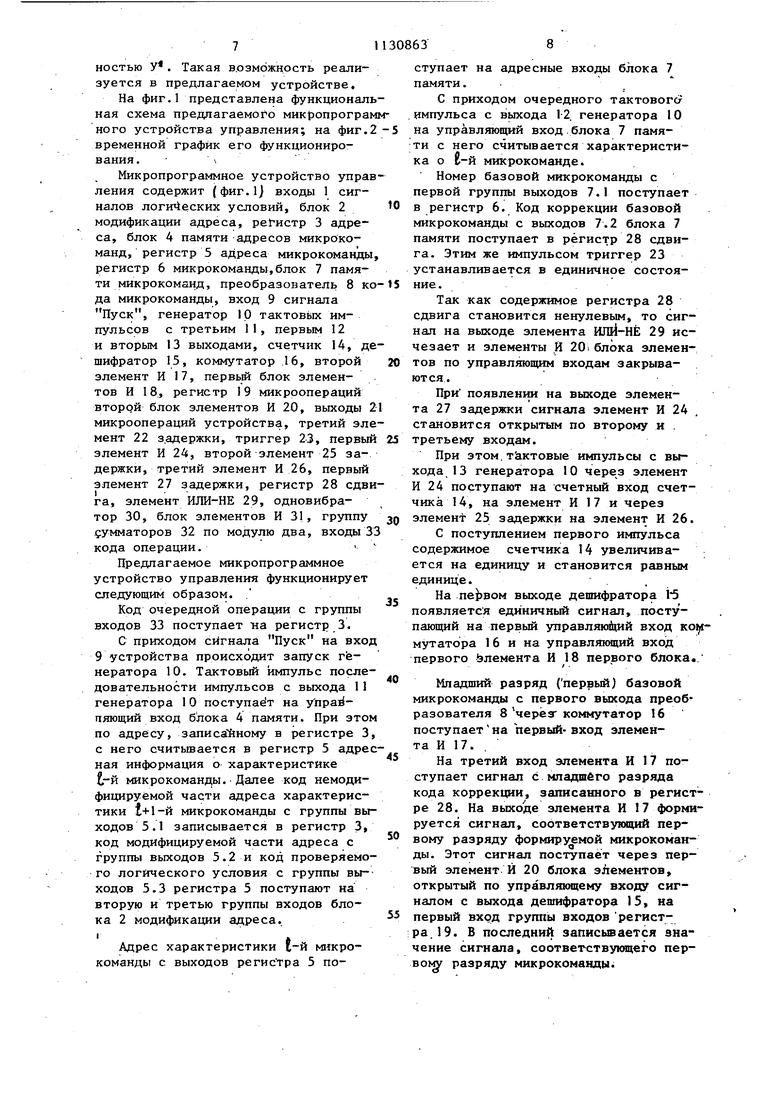

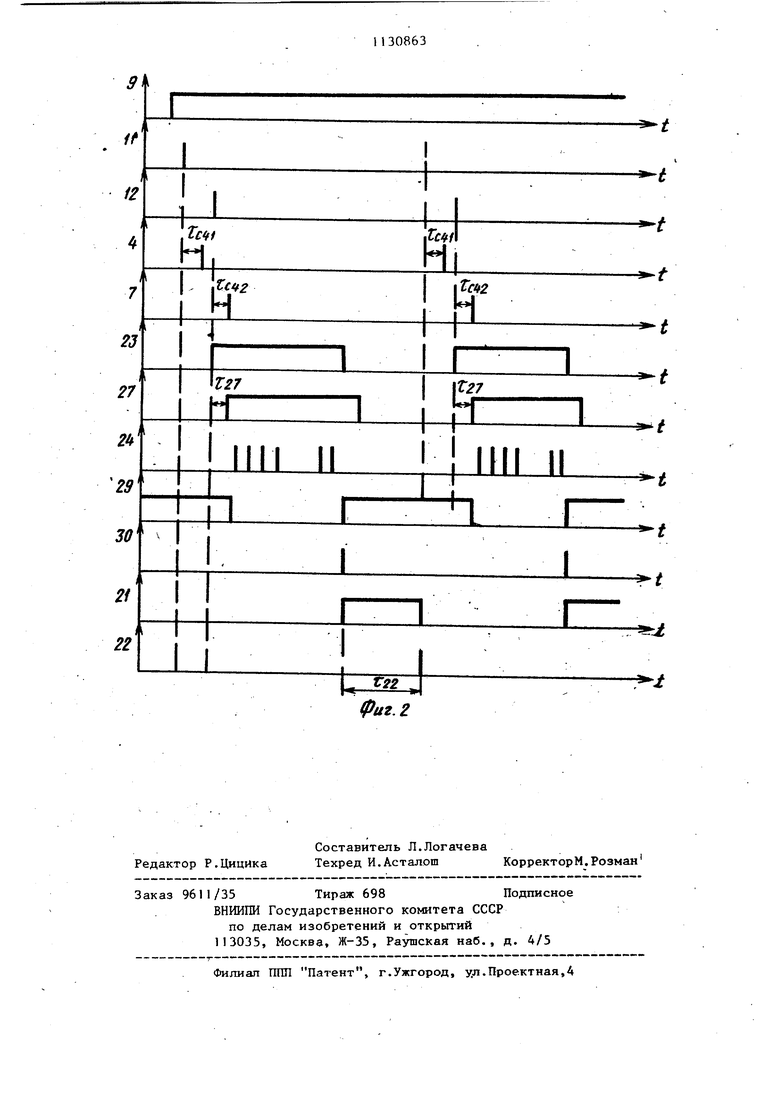

Большой объем оборудования обусловлен тем, что 10-20% разрядов микрокоманд, формируемых двухуровневым микропрограммным устр ойством управления j содержит полезную (значащую) информацию.В тО- же время 80-90% разрядов выполняемых микрокоманд не содержит полезной информации, т.е. 3 . являются информационно избыточными,, Поскольку в известном устройстве реализовано горизонтальное кодирова ние микрокоманд, когда каждой микрооперации соответствует отдельньГй разряд кода, то это приводит к тому, что в рассмотренном случае коз.ффициент информативного заполнения блока памяти также составит 0,18. . Таким образом,.большой объем обо рудования известного устройства обу ловлен реализованным в нем горизонтальным кодированием микрокоманд и отсутствием специальных технических средств, обеспечивающих декодирование микрокоманд при более эффективном методе кодирования, учитывающем малое содержание в них единиц. Цель изобретения - сокращение объема оборудования. . . В микропрограммное, устройство управления, содержащее блок модификации адреса, регистр адреса, блок памяти адресов микрокоманд., регистр адреса микрокоманды, блок памяти микрокоманд, регистр микро,команды, коммутатор, генератор тактовых импульсов, триггер, первый элемент И,, счетчик, дешифратор, регистр сдвига, причем входы сигналов логических условий устройства соединены с первой группой входов блока модификации адреса, выходы которого соединены с первой группой входов регистра адреса, выходы которого соединены с адресными входами блока памяти адресов микрокоманд, выходы которого соединены с входами регистра адреса микрокоманды, первая группа выходов которого соединена с второй группой входов регистра адреса, вторая и третья группы выходов - соответственно с второй и третьей группами входов блока модификации адреса, четвертая группа выходов - с адресными входами блока памяти микрокоманд, первая группа выходов которого соединена с входами регистра мик ,рокоманды, выходы счетчика соединены с входами дешифратора, выходы ко торого соединены с управляющими вхо дами коммутатора, входы кода операции устройства соединены с третьей группой входов регистра адреса, вхо сигнш1а Пуск устройства соединен 34 входом генератора тактовых импульсов, первый выход которого соеди- . нен с управляющим входом блока памяти микрокоманд, второй выход - с первым входом первого элемента И, дополнительно введены первый, второй, и третий элементы задержки, второй и третий элементы И, одновибратор, элемент ИЛИ-НЕ, первый и второй блоки элементов И, регистр микроопераций, преобразователь кода микрокоманды, причем выходы регистра микрокоманды соединены с входами, преобразователя кода микрокоманды, выходы которого соединены с информационными входами коммутатора, выход которого соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с первыми входами первого блока элементов И выходы которого соединены с входами регистра микроопераций, выходы которого соединены с первыми входами, второго блока элементов .И, выходы ко-. торого соединены с выходами микроопераций устройства, первый выход генератора тактовых импульсов соединен с единичным входом триггера, единичный выход которого Соединен с вторым входом первого элемента, И и через первьш элемент задержки - с третьим входом первого элемента И и управляющим входом регистра сдвига, выход первого элемента И соединен со счетным входом счетчика, вторым входом второго элемента И и через второй элемент задержки - с вторым входом третьего элемента И, выход которого соединен с входом синхронизации регистра сдвига, вторая группа выходов блока памяти микрокоманд соединена с информационными входами регистра сдвига, первый выход которого соединен с третьим входом второго элемента И, выходы регистра сдвига соединены соответственно с входами элемента ИЛИ-НЕ выход которого соединен с вторыми входами второго блока элементов И и с входом одновибратора, выход которого соединен с входами сброса счетчика и триггера и через третий элемент задержки - с входом сброса регистра микроопераций третий выход генератора тактовых импульсов соединен с управляющим входом блока памяти адресов микрокомайд,. выходы дешифратора соединены с вторыми входами первого блока элементов И соответственно. Сущность изобретения состоит в е следующем. Максимальное число едини ных разрядов в микрокоманде определ ется величиной . 5 г 0,2 У, Микрокоманды, содержащие S едини ных разрядов, будем в дальнейшем на зьшать базовыми микрокомандами. Оче видно, что таких микрокоманд, может быть не больше Z Например, при , такими ми рокомандами являютсяООП, 0110, 01 Ч 001, 1010, 1100. Остальные микрокоманды, формируе мые устройством, в которых число ед ничных разрядов S меньше S ( можно получатьпутем маскирования единичных разрядов соответствующей базовой микрокоманды. С этой целью в формат микрокоман блока памяти микрокомандвводится п ле кода коррекции Q . В этом поле записывается информа ция о том, какие единичные разряды базовой микрокоманды следует остави без изменений, а к:акие необходимо маскировать 1 Так как множество формируемых двухуровневым микропрограммным устройством управления микрокоманд порождается из базовых микрокоманд множества Z путем маскирования их единичных разрядов .в соответствии с кодом коррекции Q, то вместо хранения в У разрядах микрокоманды кодов базовых микрокоманд осуществляется хранение их номеррв. Для этой цели потребуется поле длиной в S- разрядов, где CoCJ знак округления оС до ближайшего целого числа, не меньшего чем оС . Если хранить в блоке памяти микрокоманд номера базовьк микрокоманд и коды их коррекции, то число разрядов в таких микрокомандах при сделанных допущениях, меньше числа разрядов (У )в микрокомандах, используемых в известном устройстве - и имеет следующий вид .ate., где A/i - номер базовой микрокоманды Gj;; - код коррекции базовой микрокоманды G t при формировании С-и микрокоманды. В дальнейшем будем называть информацию, записанную в ячейках памяти блока памяти микрокоманд с числом разрядов У, характеристикой микрокоманды. Пример, Из кода базовой микрокоманды G ОПОЮ получить следующие микрокоманды: 011010, 010010, 001010, 001000, 011000. Номер кода базовой микрокоманды GJ-NI 011. Тогда в ячейках памяти разрядность У блока памяти микрокоманд для первой - пятой микрокоманд будут записаны следующие характеристики (табл.). При считывании характеристики .-й микрокоманды из блока памяти микрокоманд по номеру базовой микрокоманды N крдовым преобразователем формируется базовая микрокоманда GI. Затем код модифицируется путем выполнения операции поразрядной коньюкции его единичных разрядов и соответствующих разрядов кода коррекции. Модифицированный код является формируемой устройством -микрокомандой. Следовательно, имея множество базовых микрокоманд и кодов коррекции, можно хранить в блоке памяти микрокоманд вместо множества микрокоманд разрядностью У, реализуемых устройством, их характеристики разряд7ностью у. Такая возможность реализуется в предлагаемом устройстве. На фиг.1 представлена функционал ная схема предлагаемого микропрогра ного устройства управления; на фиг. временной график его функционирования, Микропрограммное устройство упра ления содержит (фиг.1) входы 1 сигналов логиг)еских условий, блок 2 модификации адреса, регистр 3 адреса, блок 4 памяти адресов микрокоманд, регистр 5 адреса микрокоманды регистр 6 микрокоманды,блок 7 памяти микрокоманд, преобразователь 8 к да микрокоманды, вход 9 сигнала Пуск, генератор 10 тактоввк импульсов с третьим 11, первым 12 и вторым 13 выходами, счетчик 14, д шифратор 15, коммутатор .16, второй элемент И 17, первый блок элементов И 18., регистр 19 микроопераций второй блок элементов И 20, выходы микроопераций устройства, третий эл мент 22 з.адержки, триггер 23, первы элемент И 24, второй элемент 25 задержки, третий элемент И 26, первый элемент 27 задержки, регистр 28 сдв га, элемент ИЛИ-НЕ 29, одновибратор 30, блок элементов И 31, группу .умматоров 32 по модулю два, входы 3 кода операции. Предпагаемое микропрограммное устройство управления функционирует следующим образом. . Код очередной операции с группы входов 33 поступает на регистр 3. С приходом сигнала Пуск на вхо 9 устройства происходит запуск генератора 10. Тактовый импульс после довательности импульсов с выхода 11 генератора 10 поступает на упра: пяющий вход блока 4 памяти. При это по адресу, записайному в регистре 3 с него считьшается в регистр 5 адре ная информация о характеристике -й микрокоманды. Далее код немодифицируёмой части адреса характеристики t+1-й микрокоманды с группы вы ходов 5.1 записывается в регистр 3, код модифицируемой части адреса с группы выходов 5.2 и код проверяемо го логического условия с группы выходов 5.3 регистра 5 поступают на вторую и третью группы входов блока 2 модификации адреса. I Адрес характеристики 1-й микрокоманды с выходов регистра 5 по63ступает на адресные входы блока 7 памяти. С приходом очередного тактовогсг импульса с выхода 12. генератора 10 на управляющий вход.блока 7 памяти с него считывается характеристика о Е-Й микрокоманде. Номер базовой микрокоманды с первой группы выходов 7.1 поступает в регистр 6. Код коррекции базовой микрокоманды с выходов 7.2 блока 7 памяти поступает в регистр 28 сдвига. Этим же импульсом триггер 23 устанавливается в единичное состояние. Так как содержимое регистра 28 сдвига становится ненулевым, то сигнал на выходе элемента ИЛЙ-НЁ 29 исчезает и элементы И 20i блока элементов по управляющим входам закрываются. При появлении на выходе элемента 27 задержки сигнала элемент И 24 становится открытым по второму и . третьему входам. При этом, тактовые импульсы с выхода 13 генератора 10 через элемент И 24 поступают на счетный вход счетчика 14, на элемент И 17 и через элемент 25 задержки на элемент И 26. С поступлением первого импульса содержимое счетчика 14 увеличивается на единицу и становится равным единице. На пеЬвом выходе дешифратора Н появляется единичный сигнал, поступающий на первый управляюй ий вход ко мутатора 16 и на управлякиций вход первого {элемента И 18 первого блока.. Младший разряд (первый) базовой микрокоманды с первого выхода преобразователя 8 черезг коммутатор 16 поступаетна первый-вход элемента И 17. , На третий вход элемента И 17 поступает сигнал с мпадшбго разряда кода коррекции, записанного в регистре 28. На выходе элемента И 17 формируется сигнал, соответствунндий первому разряду формируемой микрокоманды. Этот сигнал поступает через первый элемент И 20 блока элементов, открытый по управляющему входу сигналом с выхода дешифратора 15, на первый вхдд группы входов регистра.19. В последний записьшается значение сигнала, соответствующего перBot разряду микрокоманды. Если значение сигнала на перчом преобразователя 8 ненулевое 9 It о выходной сигнал элемен та 25 задержки проходит через элемент И 26 на вход синхронизации регистра 28. Содержимое последнего сдвигается на один разряд вправо, и в младший разряд записьюается зна чение разряда кода коррекции. Если значение сигнала на первом выходе преобразователя 8 нулевое, то сигнал на выходе элемента И 2i6 отсутствует. При этом содержимое регистра 28 не изменяется. С по ступлением второго тактового импуль са содержимое счетчика 14 увеличива ется на единицу и становится равным двум. На втором выходе дешифратора 15 появляется единичный сигнал. Далее осуществляется формирование второго разряда микрокоманды аналогично опи санному алгоритму формирования первого рйзряда. . С поступлением -третьего им пульсов на элемент И 24 .аналогично описанному алгоритму формирования разрядов осуществляемся формировани остапьных разрядов микрокоманды и записи их значений в регистр 19. После формирования разряда микрокоманды, для которого содержимое К-го разряда базовой микрокоманды GJ ненулевое, а К+1 -h й разряды нулевые, содержимое регистра.28 становится нулевым. При этом на выходе элемента ИЛИ-НЕ 29- появляется высокий потенциал.. Элементы И 20 блока элементов от крьшаются по управляющему входу, и сигналы микроопераций микрокоманды с регистра 19 поступают на выходы 21. микроопераций устройства. Кроме того, сигнал с выхода элемента ИЛИ-НЕ 29 запускает однрвибра тор 30. Выходной импульс одновибра.тора 30 поступает наR-входы тригге ра 23, счетчика 14 и через элемент задержки на R-вход регистра 19 и переводит их в нулевое состояние. В процессе вьшолнения С-й микро команды в блоке 2 модификации адре осуществляется формирование модифи цированной части адреса кода адре-са характеристики е,+Ч-й микрокоманд 3 Формирование модифицированной части адреса осуществляется следующим образом. На первые входы элементов И 31 группы элементов блока 2 модификации адреса поступает код с группы выходов 5.3 регистра 3. На вторые входы группы элементов И 31 поступают сигналы логических условий с входов I логических условий. Выходные сигналы группы элементов И 31 поступают на первые входы соответствующих сумматоров 32 по модулю два группы сумматоров, на вторые входы которых поступает код с выходов 5.2 регистра 5. На выходах группы сумматоров 32 по модулю два формируется код модифицированной части адреса кода адреса характеристики S микрокоманды и через выходы с блока 2 модификации адреса поступает в регистр :3 адреса. С приходом очередцого .тактового импульса на управляющий вход блока 4 памяти в соответствии со значением адреса, записанного в регистре 3, из блока 4 памяти считываетйя код адреса характеристики 6+1-й микрокоманды и базовый адрес кода адреса характеристики С+2-й микрокоманды. Считанная информация записывается в регистр 5. Далее устройство функционирует аналогично алгоритму функционирования при формировании 5,-и микрокоманды. . Оценим технико-экономическую эффективность изобретения. Так как 90-95% сложности микропрограммных устройств управления составляет сложность блоков памяти микрокоманд и лишь 5-10% - сложность аппаратурного обрамления, то будем оценивать сложность микропрограммных устройств управления сложностью блоков памяти. С учетом этого допущения сложность известного микропрограммного устройства управления оценивается выражением 1 Д1 + 01 где Сд - сложность блока 4 памяти CQ - сложность блока 7 памяти. Соответственно СА KNA, где hi - множество реализуемых устройством микрокоманд-. A - число разрядов считываемой адресной информации; К - удельная стоимость элемента памяти (руб./бит); CQ KNy, где У - разрядность формируемой устройством микрокоманды. Сложность предлагаемого устройст ва -оценивается вьфажением Coi, С| - Сд2 где Сд2 сложность блока 4 памятиj Со2 сложность блока 7 памяти. Соответственно Сд2,-К-М-А СА1 Co2.KNlto lZ- 0 3 где Z - множество базовых микроко . манд G(,формируемыхустройст О. - разрядность кода коррекции. Так как число значащих разрядов кода микрокоманды (отличных от в реальных микрокомандах составляет 10-20% разрядности микрокоманды, то размерность формата кода коррекции I Q определяется выражением а. (0,1 - 0,2) Y. Размерность множества базовых ми рокоманд определится числом сочетаний из У разрядов по Q разрядов а у; Cy-q, /(,;. Сравним выражения С и CQJ ме ду собой, тогда. 4c KNy-KN(eo3tCy а) . Из анализа этого выражения следует, что iu С О при .а(0,25 - 0,3), что всегда имеет место на практике. , выигрыш в экономичности предлагаемого устройства по отношение к известному оценится величиной(y-(ec.gj,) (l6-e...))-,0.iSQo Следовательно, предлагаемое микропрограммное устройство управления существенно экономичнее, известного. Применение предлагаемого двухуровневого микропрограммного устройства управления в автоматике, вычисЬительной технике, системах передачи данных позволит сократить объем их оборудования и снизить стоимость. Объем оборудования двухуровневых микропрограммных устройств управления сокращается за счет хранения в блоке памяти микрокоманд вместо микрокоманд номеров их базовых микрокоманд и одов коррекции. Коэффициент использования блока памяти микрокоманд yвJeличивaeтcя за счет хранения в блоке памяти 6je3избыточной информа1щи о текущих микрокомандгис, формируемых устройством.

9

JL

iO /5

ac

yff

/« R

15

/r

KG

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство микропрограммного управления | 1972 |

|

SU482744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Геолецян А.Г | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| М., Статистика, 1975, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-12-23—Публикация

1982-10-06—Подача