(54) УСТРОЙСТВОдля КОНТРОЛЯ ЛОГИЧЕСКИХ РЛОКОВ

la с выходом - вход ключа, выход которого соединен с третьим входом компаратора и с выходом, устройства. Известное устройство под воздействи-. ем теста, поступающего от внешнего блока памяти, формирует стимулирующие сигналы, подаваемые на входы проверяемой цифровой схемы, получает от нее ответные сигналы, сравнивает их с эталоннь1ми сигналамий запомина ет результаты сравнения. Информация от внешнего блока памяти, в котором Хранится тест, передается в регистр данных, первый и второй блоки памяти по отдельным каналам. Причем, в регистр данных записывается информация о стимулирующих сигналах, в первый блок памяти - данные, определяющие какой из выводов цифровой схемы необходимо закоммутрровать как вход, а какой как выход. Во второй блок памяти устройства поступают эталонны данные ответных сигналов 3.

Недостаток известного устройства - ограниченная область применения и недостаточное быстродействие.Ограниченность применения обуслОвЯенаГ тем, что при контроле цифровых схем может использоваться только такой внешний блок памяти, в которсм. имеется по крайней мере три выходных канала, по которым данные о тесте передаются в регистр данных и первый и второй блоки памяти. Например, это устройство нельзя применять с такими внешними блоками памяти, в которых имеется лишь один выходной канал, а именно: с фотосчитывающими механизмами, накопителями на магнитной ленте и т.д. Если в качестве внешнего источника информации использовать ЭВМ, то дЛя подключения к ней известного устройства понадобится занять три выхрдных канала, которые не всегда могут быть в наличии. ..

Низкое быстродействие устройства обусловлено тем, что время считывакнй еста из регистра данных (время одного цикла) определяется количеством разрядов в регистре данных и не зависит от длины теста, так как в устройстве отсутствуют узлы, обесГгачявающие уменьшение длительности цикла при уменьшении длины теста. Длина же теста определяется сложностью проверяемой цифровой схемы, и регистр данных в известном устройстве должен содержать такое количество разрядов, чтобы поместить тест (Максимальной длины. Следовательно, в устройстве время проверки не зависит от длины теста и постоянно, так.как равно времени поочередного считывания информации из всех разрядов регистра данных. Это увеличивает/время проверки тех цифровых схем, у которых длина теста меньше /максимальной величины, т.е. снижает

быстродействие известного устройства и является его недостатком.

Цель изобретения - расширение области применения и повышение быстродейств ия устройства.

Поставленная цель достигается тем, что в устройство для контроля логических блоков, содержашее синхронизатор, соединенный первым.выходом с первым входом компаратора, соединенного выходом с первым входом первого блока памяти, соединенного вторым входом со вторым выходом синхронизатора, третий выход которого соединен с первым входом второго блока памяти, соединенного выходом через первый триггер со вторым входом компаратора и первым входом элемента И, со вторым входом которого соединен выход второго триггера, а с вйходом - вход ключа, выход которого соединен с третьим входом компаратора и с выходом устройства, введены блок сопряжения, первый, второй, третий, .четвертый, пятый и шестой регистры хранения, первый и BTopcrfl счетчики, первый и второй блоки срайнения и регистр сдвига, причем, вход устройства соединен с первым входом блока сопряжения, соединенного выходом с первыми входами первого, второго, третьего и четвертого регистров хранения,первые выход первого и второго регистров хранения соединены соответственно с первым и вторым входами синхронизатора, выход третьего регистра хранения соединен с первым.входом первого блока сравнения, соединенного вторым входом с выходом пятого регистра хранения и первым входом первого счетчика, соединенного выходом со входом пятого регистра хранения, с третьим входом первого блока памяти, вторым входом второго блока памяти и с третьим входом первого блока сравнения, соединенного выходом с третьим входом синхронизатора, соединенного четвертым выходом со вторым входом первого счетчика, пятым выходом - с первым входом второго счетчика, второй вход которого соединен с выходом шестого регистра хранения я первым входом второго блока сравнения, второй вход которого соединен с выходом второго счетчика и со входом шестого регистра хранения, а выход г с четвертым входом синхронизатора, соединенного шестым выходом с первым входом регистра сдвига,выход которого соединен со вторым входсм четвертого регистра хранения третьим входом второго блока памяти и входом второго триггера, второй вход - с выходом первого блока памяти, третий вход - с первым выходом четвертого регистра хранения соединенного эторым выходом со вторь входом блока сопряжения, а третьим

входом - с седьмым выходом синхронизатора, соединенного пятым входом со вторым выходом блока сопряжения.

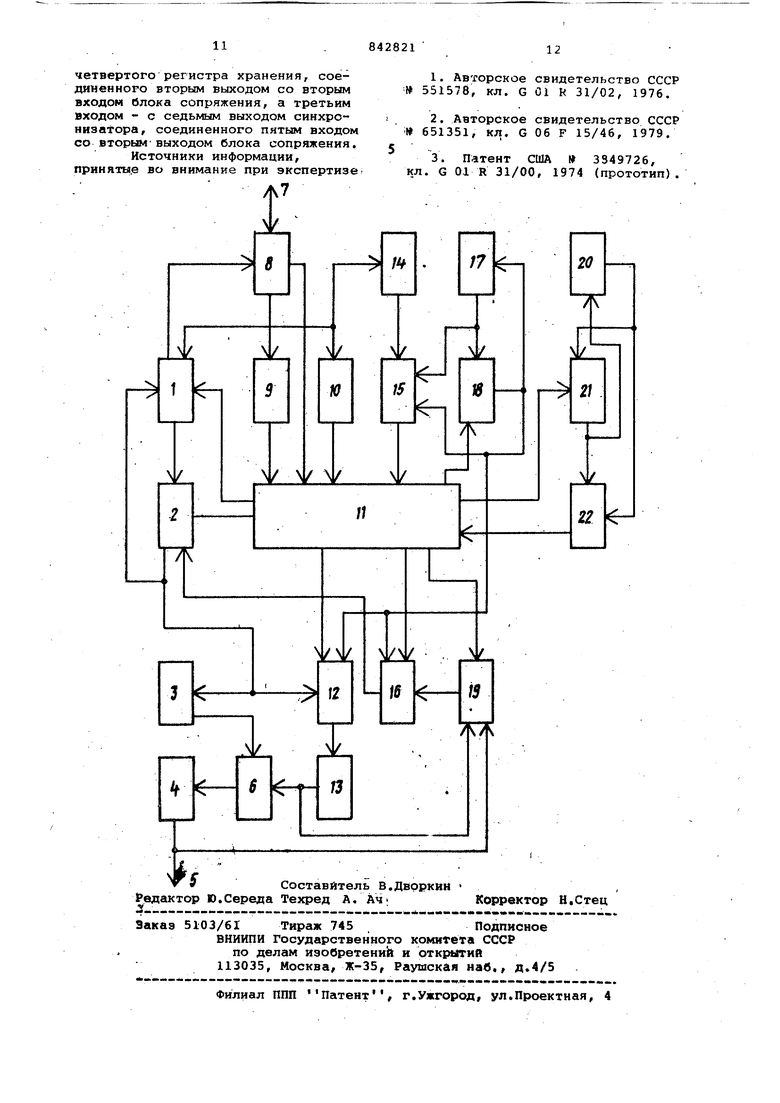

На чертеже дана структурная схема устройства.

Устройство для,контроля логических блоков содержит четвертый.регистр I хранения, регистр 2 сдвига, второй триггер 3, ключ 4, выход 5, элемент И 6, вход 7, блок 8 сопряжения, второй 9 и первый 10 регистры хранения, синхронизатор 11, второй блок 12 памяти, первый триггер 13, третий регистр 14 хранения, первый блок 15 сравнения, первый блок 16; памяти, пятый регистр 17 хранения, первый счетчик 18, компаратор 19, шестой регистр 20 хранения, второй счетчик .21, второй блок 22 сравнения

Устройство работает следующим об(разом.

Навход 7 устройства поступают информационные сообщения от внешнего блока памяти, например, от ЭВМ. Каждое сообщение состоит из трех служебных и нескольких информационных байтов. Количество информационных байтов определяется числом п выходных каналов устройства и равно п/6.

Под каналом понимается вывод проверяемого логического блока, независимо от того, является он входным ил выходным. На чертеже показан только один в ыходной канала устройства. Если устройство строится на п кана лов, то оно содержит по п компараторов 19, блоков 12 и 16, триггеров 3 и 13, элементов И 6, ключей 4 и выходов 5 и п-раэрядный регистр 2. При проверке логического блока каждый из его выводов подключается к одному из выходов 5 устройства.

Первый из служебных байтов определяет режим работы устройства,.второй - номер набора, на котором необходимо произвести останов .устройства, а третий - величину задержки выдачи ответных сигналов проверяемого блока.

Устройство работает в режимах коммутации, проверки коммутации, подачи на проверяемый блок контролирующего теста и приема от него логических сигналов в одноразовом и циклическом режимах. Останова по номеру кадра, измерения задержки распространения логических сигналов.

При поступлении первого служебног байта на вход 7. устройства блок 8 вырабатывает сигнал синхронизатору 11, который записывает этот байт в регистр 10. Первый байт первого сообщения определяет режим коммутации. Второй байт, приходящий на вход 7 устройства, поступает аналогичным образом в регистр14, третийв регистр 9. Затем поступает п/8байтов, определяющих программу коммутации, т.е. какой из каиашов устройства будет входным, а какой выходным. Каждый из этих п/8 байтов сначала по команде синхронизатора параллельно поступает в регистр 1. После этого синхронизатор 11 вырабатывает 8 импульсов сдвига и сдвигает принятый байт в регистр 2 на 8 разрядов, освобождая место для приема очередного байта. После приема всех п/8 байтов все п разрядов регистра 2 будут заполнены. Их содерoжимое переписывается.в триггеры 3 каждого канала таким образом, что первый разряд .регистра 2 переписывается в триггер 3 первого канала, второйразряд - в триггер 3 второго

S канала и т.д. Состояние триггера 3 определяе - режим канала на все время раВоты с проверяемым устройством. Если в триггер 3 поступает , что. определяет режим работы канала,как

0 выход устройства, то на второй вход элемента И 6 поступит разрешающий уровень.

Основной режим работы устройстваподача на проверяемый логический

блок и прием от него логических сиг5налов - режим тестовой проверки.

Блок 8 пр.инимает сообщения в этом режиме аналогично режиму коммутации. Колич:ест о сообщений, принимаемое блоком режиме тестового контро0ля, определяется длиной теста, т.е. количеством кадров информации, подаваемой на вход проверяемого блока. Под кадром Понимается период времени, в течение iкоторого выходные сигналы

5 устройства, поступающие на вход проверяемого блока, остаются неизменными . Каждому кадру соответствует одно сообщение. Тест строится таким образом, что каналы эакоммутированные,

0 как выходные, записываются стимулирующие сигналы, подаваемые на вход проверяемого блока, а в каналы, закоммутиррванные, как входные - информация об ответных сигналах, которяле должны поступить от проверяемого

5 блока.

При приеме теста первый байт, записываемый в регистр :10 в каждом сообщении, определяет режим тестовой проверки. При приеме информацион0ных байтов теста счетчик 18 подсчитывает количество байтов в кадре, а счетчик 21 - количество кадров. После приияа последнего кадра содержимое счетчика 18 переписывается

5 в регистр 17, а счетчика 21 в регистр 2О,после чего счетчики 18, 21 сбрасываются в нулевое состояние. Информация о тесте из регистра 2 под управлением синхронизатора 11 переписывается в блок 12. Причем информа0ция о первом кадре записывается по первому адресу блока 12, а втором кадре - по второму и т.д.Количество адресов блока 12 определяется количеством кадров. После приема

5

всех саобш,ений о тесте блок 8 вырабатывает -сигнал, под воздействием которбго и при наличии в регистре 10 байта, определяющего |зежим тестовой проверки, синхронизатор 11 считывает информацию из блока 12, начиная С первого адреса, определяемого счетчиком 18, Выходное число блока 12 записывается в триггер 13 и через элемент. И 6 поступает на ключ 4. Элемент И 6 не пропускает сигналов тех каналов., где в триггер 3 записан О, т.е. каналов, которые закоммутированы как входы. При последовательном чтении с блока 12 на выходах 5 устройство формирует последовательность логических сигнгшов, поступающую на входные выводы проверяемого блока/ ключ 4 задает величину уровней логической в зависимости от характеристик тех логических элементов, на которых построен контролируемый блок. В ответ на эти сигналы на выходных выводах контролируемого блока появлятся сигналы значения которых необходимо проверить . Они поступают на вход компаратора -19, где происходит логическое сравнение ответного сигнала с уровО

Нем логической

в

или

зависимости от значения ответного сигнала, записанного в блоке 12. При несоответствии ответных сигналов заданным уровнем логической i или или при их неравенстве ответным сигналам, записанным в блоке 12, компаратор 19 вырабатывает сигнал ошибки, который поступает в блок 16. Запись в блок 16 происходит по тому же адресу, что и в блок 12, так как адрес определяется счетчиком 18. При чтении блока 12 и записи сигналов ошибок в блок 16 счетчик 18 изменяет свой адрес на единицу младшего разряда до тех пор, пока значение адреса блоков 12 и 16 (т.е. счетчика 18) не станет равным коду, записанному в регистре 17. р момент равенства кодов регистра 17 и счетчика 18 блок 15 вырабатывает сигнал, во которому синхронизатор 11 прекращает изменять состояние счетчика 18, блоков 12 и 16. При этом блок 12 прекраадает подачу тестовых сигналов ка проверяемы блок, а блок 16 - запись ответных сигналов. Если служебным бдйтсад устройству был задан циклический режим, то работа его продолжается установкой счетчика 18 в нулевое состояние, а затем чтением с блока 12 и записью в &лоц 16, начиная с первого адреса и т.д.

Если служебным байтом устройству была задана одноразовая, проверка, то после прохождения одного цикла устройство переходит к передаче результатов проверки на внешний источник. При этом синхронизатор 11 на«чинаёт чтение с блока 16 с первого

адреса. Выходные числа с блока 16 поступают в регистр 2, а затем побайтно из него - в регистр 1 и через блок 8 на вход 7 устройства и поступают в ЭВМ для отображения результатов проверки на дисплее или распечатки на АЦПУ и т.д.

При считывании каждого байта информации из регистра 2 в регистр-1 синхронизатор 11 подает на вход счетчика 21 счетные импульсы после считывания байта. Передача байтов прекращается после того, как в счетчике 21 окажется число, равное числу байтов,, записанному в регистре 20. Блок 22 определяет момент равенства чисел. После передачи одного кадра информации счетчик 18 меняет значени адреса на единицу младшего разряда и начинает передачу следующего кадра

После считывания всех кадров информация из блока 16 в счетчик 18 со держит число, равное числу кадров, записанному в регистре 17, что определяет схема 15 сравнения, прекращая чтение с блока 16 и передачу информации на вхо.ц 7.

Таким образом, в предлагаемом устройстве время проверки логических блоков пропорционально количеству кадров теста, а время передачи результат в контроля пропорционально количеству байтов в кадре (количеству контролируемых каналов) и количеству кадров в тесте. В режиме одноразовой проверки устройство обеспечивает возможность определить, исправен или неисправен контролируемый блок и выявить ошибки в сигналах на его входных и выходных выводах. В циклическом режиме работы устройство производит диагностику логического блока,Т.е. локализует обнаруженную неисправность,.например, по сигналам на экране осциллографа. Благодаря циклическому режиму проверки на экране осциллографа можно наблюдать осцилограмкш сигналов, так как тест на контролируемый блок поступает периодически. В режиме проверки времени появления ответного сигнала на выходе контролируемого блока по отнОшению ко входным сигналам, в тре,тьем байте каждого сообщения теста 1содержится код величины задержки выдачи ответных сигналов контролируемого блока. Записанный в регистр 9, этог байт определяет в синхронизаторе 11 время задержки сигнала записи результатов контроля в блоке 16 по Отношению ко времени подачи стимулирую1В1И}С сигналов на контролируемый .

В ежиме останова по номеру -кадра на зноя контролируемого блока поступают постоянные Логические уровни, а результаты проверки записываются в блок 1:6. Для этого при передаче (Теста 3 регистр 10 поступает байт,

пределяющий режим останова по номеу кадра, а в регистр. 14 - байт, пределяющий номер кадра, на котором олжен произойти останов.

Устройство в этом режиме работает ак в режиме тестовой проверки. Однако в момент, когда блок 15 фиксиует равенство кодов в счетчике 18 и регистре 14, счетчик 18 прекращает задавать новые адреса блока 12, вследствие чего в триггере 13 и клюе 4 остаются неизменные логические сигналы, которые поступают на вход контролируемого блока. Результаты контроля поступают в блок 16 и с него через блок 8 на вход 7 устройства, как и в режиме тестовой провер-, ки с той разницей, что на вход 7 nocTynatoT результаты проверки только по кадру, на котором произошел останов. Для перехода к проверке на следующем кадре в регистр 14 необходимо записать код очередного кадра и т.д.

Режим проверки коммутации следует после коммутации и необходим, как контрольный режим. При коммутации и проверке коммутации контролируемый блок к устройству не подключается.

В режиме проверки коммутации в регистр 10 поступает байт, определяющий этот режим. В качестве теста на вход устройства передается кадр из п/8 байтов, во всех разрядах которых записаны единицы. Как и в режиме тестовой проверки, этот кадр поступает по первому адресу в блок 12 и через триггеры 13 и элементы И б - на ключи 4. При этом единичные сигналы появлятся на выходе тех каналов, которые закоммутированы как выходы, а на входных каналах будут логические нули, так как логическая проходит через элемент И 6 только того канала, в котором в триггер 3 была при коммутации записана . Логическая 1 с выхода 5 устройства поступает на вход компаратора 19, сравнивается с ним с , записанной в триггере 13 и результат сравнения проверки коммутации поступает и регистр 2 и побайтно передается на вход 7 устройства лля определения правильности коммутации и исключения ложных ошибок при контроле блоков.

Таким образом, предлагаемое устройство за счет введения в его состав блока 8, регистров 2,9,10,14,20 обеспечивает связь с внешним блоком памяти по одному каналу, что обеспечивает его применение с произвольным блоком памяти, каналом связи и т.д., что расширяет его область применения,

С другой стороны, предлагаемое устройство характеризуется высоким быстродействием, так как ар&ля контроля логических блоков в нем

определяется количеством кадров в тесте.

Формула изобретения

Устройство для контроля логических, блоков, содержащее синхронизатор, соединенный первым выходом с первым входом компаратора, соециненного выходом с первым входом

0 первого блока памяти, соединенного вторым входом со вторым выходом Ьинхронизатора, третий выход которого соеди 1ен с первым входом второго блока памяти, соединенного выходом че5ре первый триггер со вторым входом компаратора и первым входом элемента И, со вторым входом которого соединён выход второго триггера, а с выходом-- вход ключа, выход которого

0 соединен с третьим входом компаратора и с выходом устройства, отличающееся тем, что, с целью расширения области применения и повышения быстродействия, в него введены блок сопряжения,первый,второй,

5 третий, четвертый, пятый и шестой регистры хранения, первый и второй счетчики, первый и второй блоки сравнения и регистр сдвига, причем вход устройства соединен с первым

0 входом блока сопряжения, выходом соединенного с первыми входами первого, второго, третьего и. четвертого регистров хранения, первые выходы первого и второго регистров хранения

5 соединены соответственно с первым и вторые входами синхронизатора, выход третьего регистра хранения соединен с первым входом первого . блока сравнения, соединенного вто0Ежлм входом с выходом пятого регистра хранения и первым входом первого счетчика, соединенного выходом со входом пятого регистра хранения, третьим входом первого блока памяти, вторым входом второго блока памяти

5 и с TpiSTbHM входом первого блока сравнения, соединенного выходом с третьим входом синхронизатора,соединенного четвертым выходом сО вторым входом первого счетчика, пятым вы0ходом - с первым входом второго счетчика, второй вход которого соединен с выходом шестого регистра хранения и первым входом второго блока сравнения, второй вход которого соединен с выходом второго счетчика и со входом шестого регистра хранения, а выход - с четвертым входом синхронизатора, соединенного шестым выходом с первым входом регистра сдвига,

0 выход KOTOiPoro соединен со вторым входом четвертого регистра хранения, третьим входом второго блока памяти и входом второго триггера, второй ьход .- с выходом первого блока памяти, третий вход - с первым выходом

четвертого регистра хранения, соединенного вторвлм выходом со вторым входом блока сопряжения, а третьим входом - с седьмым выходом синхронизатора, соединенного пятым входом со вторым выходом блока сопряжения.

Источники информации, прнняты.е во внимание при экспертизе г

1.Авторское свидетельства СССР 551578, кл. G 01 Н 31/02, 1976.

2.Авторское свидетельство СССР 651351, кл. G 06 F 15/46, 1979.

3.Патент США 3349726, кл. G 01 R 31/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

Авторы

Даты

1981-06-30—Публикация

1979-10-22—Подача