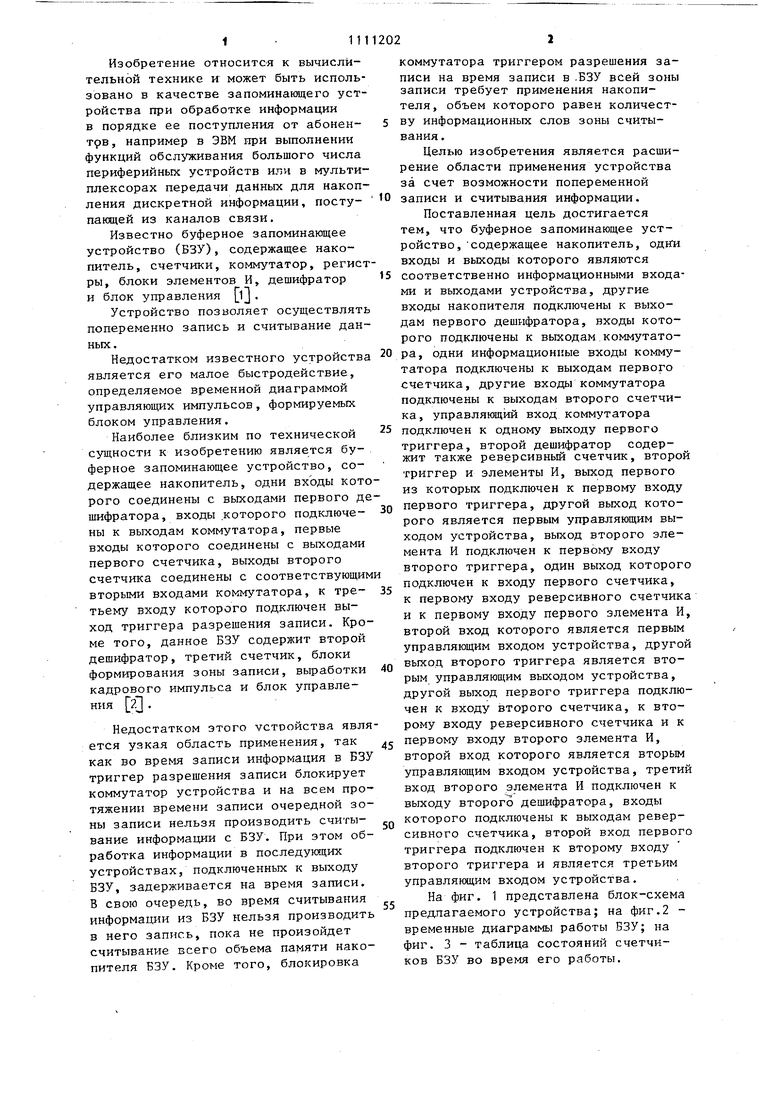

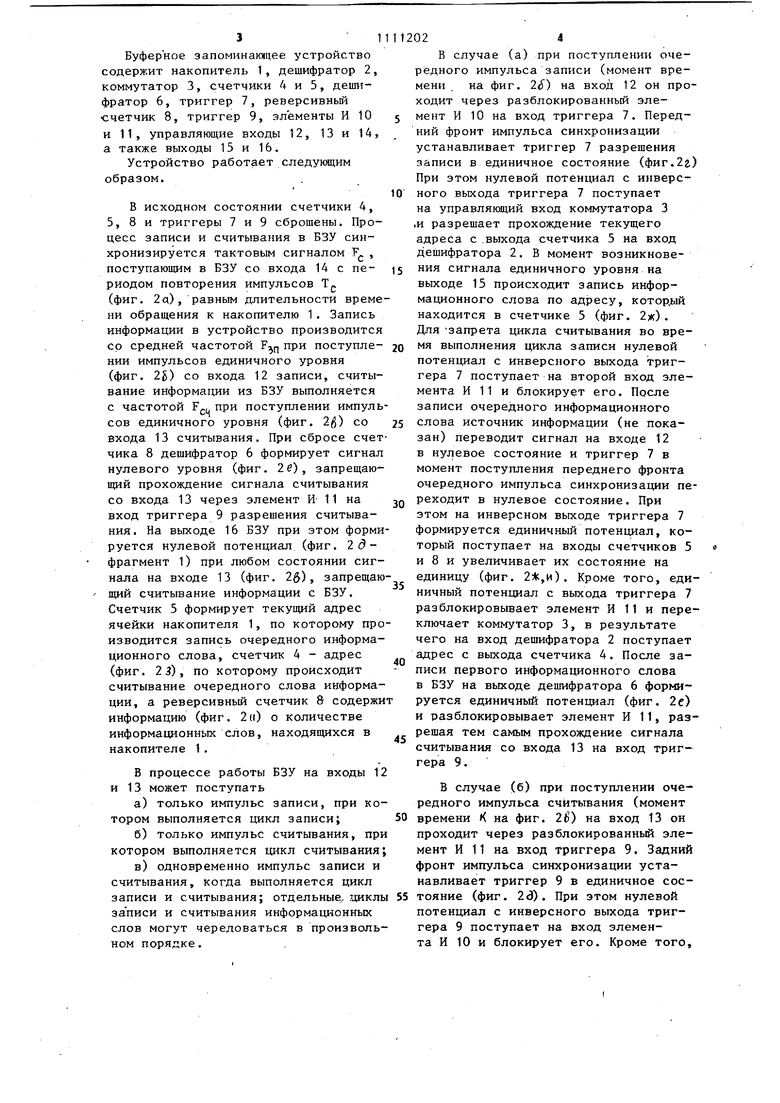

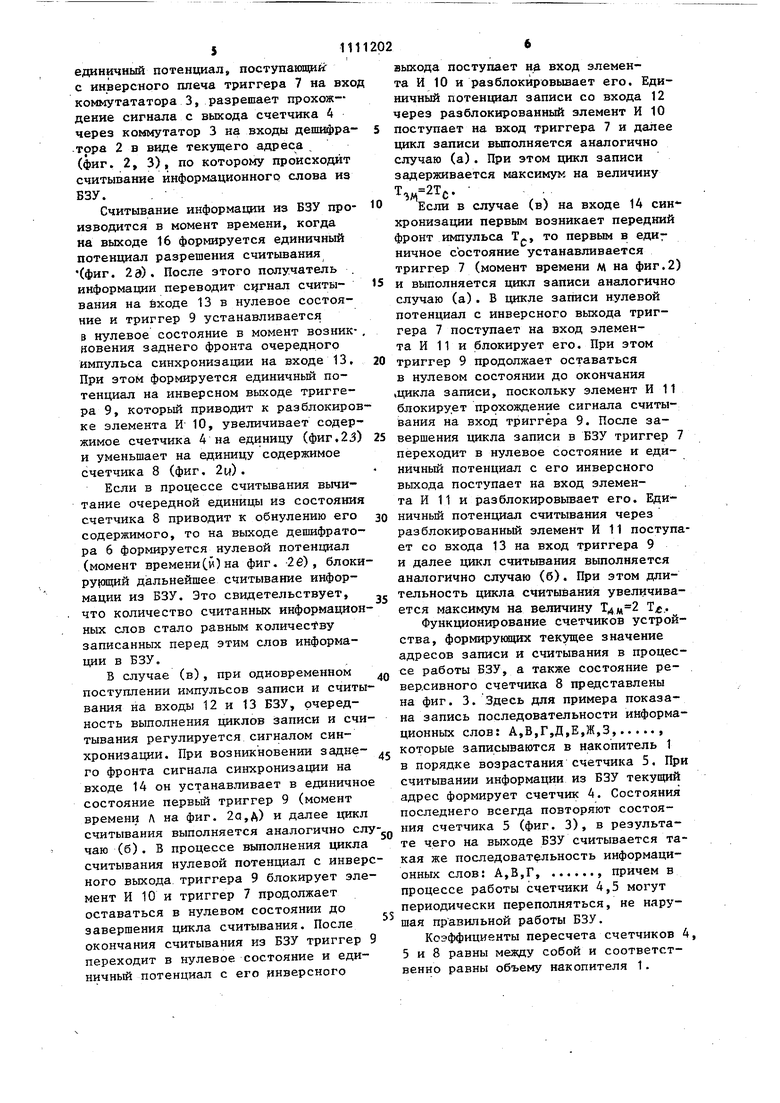

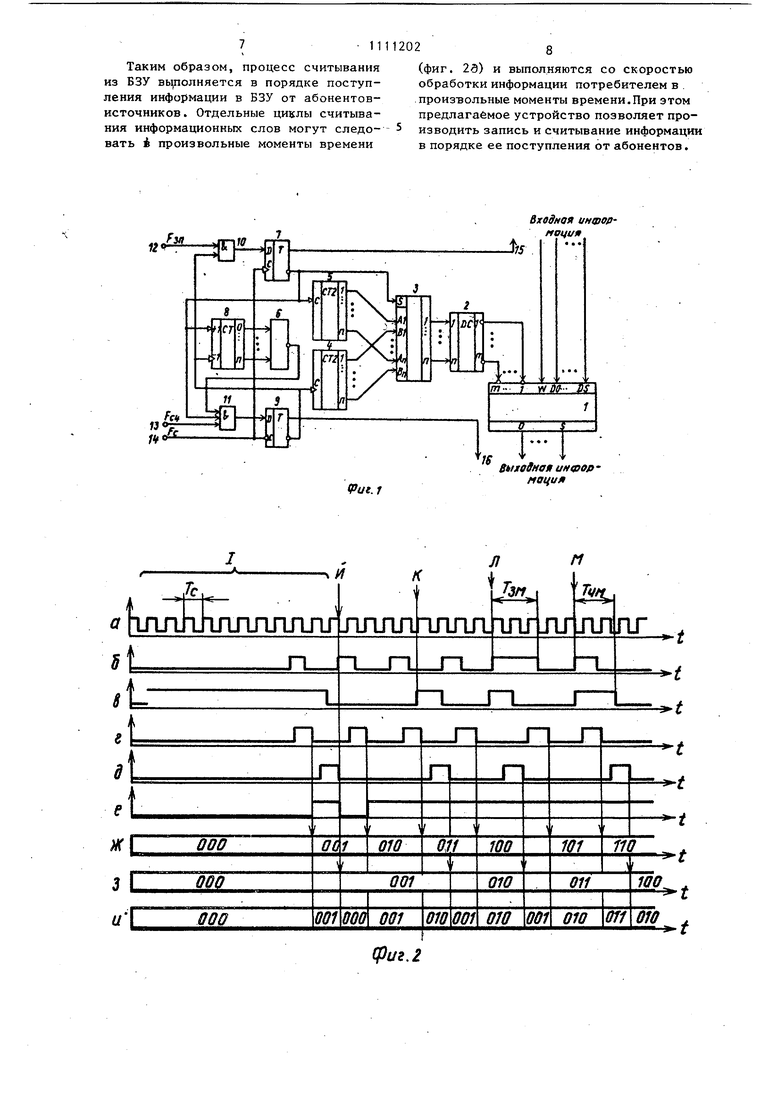

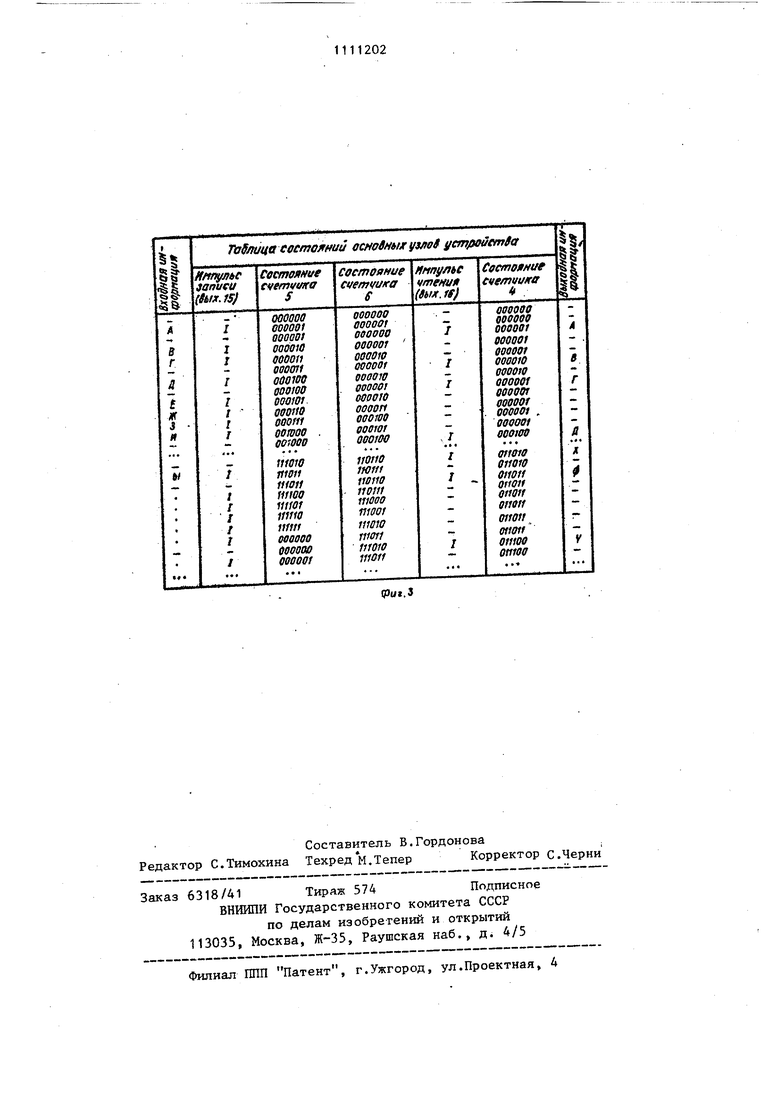

Изобретение относится к вычислительной технике и может быть исполь зовано в качестве запоминающего уст ройства при обработке информации в порядке ее поступления от абонентрв, например в ЭВМ при выполнении функций обслуживания большого числа периферийных устройств или в мульти плексорах передачи данных для накоп ления дискретной информации, поступающей из каналов связи. Известно буферное запоминающее устройство (БЗУ), содержащее накопитель, счетчики, коммутатор, регис ры, блоки элементов И, дешифратор и блок управления ij . Устройство позволяет осуществлят попеременно запись и считывание дан ных . Недостатком известного устройств является его малое быстродействие, определяемое временной диаграммой управляющих импульсов, формируемых блоком управления. Наиболее близким по технической сущности к изобретению является буферное запоминающее устройство, содержащее накопитель, одни входы кот рого соединены с выходами первого д шифратора, входы .которого подключены к выходам коммутатора, первые входы которого соединены с выходами первого счетчика, выходы второго счетчика соединены с соответствующим вторыми входами коммутатора, к третьему входу которого подключен выход триггера разрешения записи. Кро ме того, данное БЗУ содержит второй дешифратор, третий счетчик, блоки формирования зоны записи, вьгработки кадрового импульса и блок управления Г| . Недостатком этого устройства явля ется узкая область применения, так как во время записи информация в БЗУ триггер разрешения записи блокирует коммутатор устройства и на всем протяжении времени записи очередной зоны записи нельзя производить считывание информации с БЗУ. При этом обработка информации в последующих устройствах, подключенных к выходу БЗУ, задерживается на время записи. В свою очередь, во время считывания информации из БЗУ нельзя производить в него запись, пока не произойдет считывание всего объема памяти накопителя БЗУ. Кроме того, блокировка коммутатора триггером разрешения записи на время записи в .БЗУ всей зоны записи требует применения накопителя, объем которого равен количеству информационных слов зоны считывания. Целью изобретения является расширение области применения устройства за счет возможности попеременной записи и считывания информации. Поставленная цель достигается тем, что буферное запоминающее устройство, содержащее накопитель, одн1и входы и выходы которого являются соответственно информационными входами и выходами устройства, другие входы накопителя подключены к выходам первого дешифратора, входы которого подключены к выходам коммутатора, одни информационные входы коммутатора подключены к выходам первого счетчика, другие входы коммутатора подключены к выходам второго счетчика, управляющий вход коммутатора подключен к одному выходу первого триггера, второй дешифратор содержит также реверсивный счетчик, второй триггер и элементы И, выход первого из которых подключен к первому входу первого триггера, другой выход которого является первым управляющим выходом устройства, выход второго элемента И подключен к первому входу второго триггера, один выход которого подключен к входу первого счетчика, к первому входу реверсивного счетчика и к первому входу первого элемента И, второй вход которого является первым управляющим входом устройства, другой выход второго триггера является вторым управляющим выходом устройства, другой выход первого триггера подключен к входу второго счетчика, к второму входу реверсивного счетчика и к первому входу второго элемента И, второй вход которого является вторым управляющим входом устройства, третий вход второго элемента И подключен к вьпсоду второго дешифратора, входы которого подключены к выходам реверсивного счетчика, второй вход первого триггера подключен к второму входу второго триггера и является третьим управляющим входом устройства. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг.2 временные диаграммы работы БЗУ; на иг. 3 - таблица состояний счетчиков БЗУ во время его работы. Буферное запоминающее устройство содержит накопитель 1, дешифратор 2, коммутатор 3, счетчики 4 и 5, дешифратор 6, триггер 7, реверсивный счетчик 8, триггер 9, элементы И 10 и 11, управляющие входы 12, 13 и 14, а также выходы 15 и 16. Устройство работает следующим образом. В исходном состоянии счетчики 4, 5, 8 и триггеры 7 и 9 сброшены. Процесс записи и считывания в БЗУ синхронизируется тактовым сигналом F , поступаюшлм в БЗУ со входа 14 с периодом повторения импульсов Т (фиг. 2а), равным длительности време ни обращения к накопителю 1. Запись информации в устройство производится со средней частотой при поступлеНИИ импульсов единичного уровня (фиг. 2J) со входа 12 записи, считывание информации из БЗУ выполняется с частотой F при поступлении импуль сов единичного уровня (фиг. 2) со входа 13 считывания. При сбросе счет чика 8 дешифратор 6 формирует сигнал нулевого уровня (фиг. 2е), запрещающий прохождение сигнала считывания со входа 13 через элемент И 11 на вход триггера 9 разрешения считывания. На выходе 16 БЗУ при этом форми руется нулевой потенциал (фиг. 2дфрагмент 1) при любом состоянии сигнала на входе 13 (фиг. 2), запрещаю щий считывание информации с БЗУ. Счетчик 5 формирует текущий адрес ячейки накопителя 1, по которому пр изводится запись очередного информа ционного слова, счетчик 4 - адрес (фиг. 23), по которому происходит считывание очередного слова информа ции, а реверсивный счетчик 8 содерж информацию (фиг. 2 (i) о количестве информадаонных слов, находяпщхся в накопителе 1 . В процессе работы БЗУ на входы 1 и 13 может поступать а)только импульс записи, при ко тором выполняется цикл записи; б)только импульс считывания, пр котором выполняется считывания в)одновременно импульс записи и считывания, когда выполняется цикл записи и считывания; отдельные цикл записи и считывания информационных слов могут чередоваться в произволь ном порядке. В случае (а) при поступлении очередного импульса записи (момент времени на фиг. 2) на вход 12 он проходит через разблокированный элемент И 10 на вход триггера 7. Передний фронт импульса синхронизации устанавливает триггер 7 разрешения записи в единичное состояние (фиг.2г.) При этом нулевой потенциал с инверсного выхода триггера 7 поступает на управляющий вход коммутатора 3 ,и разрешает прохождение текущего адреса с .выхода счетчика 5 на вход дешифратора 2. В момент возникновения сигнала единичного уровня на выходе 15 происходит запись информационного слова по адресу, котор,ый находится в счетчике 5 (фиг. 2ж). Для запрета цикла считывания во время выполнения цикла записи нулевой потенциал с инверсного выхода триггера 7 поступает на второй вход элемента И 11 и блокирует его. После записи очередного информационного слова источник информации (не показан) переводит сигнал на входе 12 в нулевое состояние и триггер 7 в момент поступления переднего фронта очередного импульса синхронизации переходит в нулевое состояние. При этом на инверсном выходе триггера 7 формируется единичный потенциал, который поступает на входы счетчиков 5 и 8 и увеличивает их состояние на единицу (фиг. 2,и). Кроме того, единичный потенциал с выхода триггера 7 разблокировывает элемент И 11 и переключает коммутатор 3, в результате чего на вход дешифратора 2 поступает адрес с выхода счетчика 4. После записи первого информационного слова в БЗУ на выходе дешифратора 6 формируется единичный потенциал (фиг. 2е) и разблокировывает элемент И 11, разрешая тем самым прохождение сигнала считывания со входа 13 на вход триггера 9. В случае (б) при поступлении очередного импульса считывания (момент времени К на фиг. 2fc) на вход 13 он проходит через разблокированный элемент И 11 на вход триггера 9. Задний фронт импульса синхронизации устанавливает триггер 9 в единичное состояние (фиг. 26). При этом нулевой потенциал с инверсного выхода триггера 9 поступает на вход элемента И 10 и блокирует его. Кроме того. $11 единичный потенциал, поступаюпщйг с инверсного плеча триггера 7 на вхо коммутататора 3, разрешает прохождение сигнала с выхода счетчика 4 через коммутатор 3 на входы дешифра.тора 2 в виде текущего адреса (фиг. 2, 3), по которому происходит считывание информационногр слова из БЗУ. . Считывание информации из БЗУ производится в момент времени, когда на выходе 16 формируется единичный потенциал разрешения считывания (фиг. 2э). После этого получатель . информации переводит считывания на ёходе 13 в нулевое состояние и триггер 9 устанавливается в нулевое состояние в момент возникновения заднего фронта очередного импульса синхронизации на входе 13. При этом формируется единичный потенциал на инверсном выходе триггера 9, который приводит к разблокиро ке элемента И 10, увеличивает содер жимое счетчика 4 на единицу (фиг.23 и уменьшает на единицу содержимое счетчика 8 (фиг, 2и). Если в процессе считывания вычитание очередной единицы из состояния счетчика 8 приводит к обнулению его содержимого, то на выходе дешифратора 6 формируется нулевой потенщ1ал (момент времени(й)на фиг. 26), блоки ру(ощий дальнейшее считывание информации из ВЗУ. Это свидетельствует, что количество считанных информацион ных слов стало равным количеству записанных перед этим слов информации в БЗУ. В случае (в), при одновременном поступлении импульсов записи и считы вания на входы 12 и 13 БЗУ, очередность выполнения циклов записи и счи тывания регулируется сигналом синхронизации. При возникновении заднего фронта сигнала синхронизации на входе 14 он устанавливает в единично состояние первьй триггер 9 (момент времени Л на фиг. 2а,А) и далее цикл считывания выполняется аналогично сл чаю (б). В процессе выполнения цикла считывания нулевой потенциал с инвер ного выхода триггера 9 блокирует эле мент И 10 и триггер 7 продолжает оставаться в нулевом состоянии до завершения цикла считывания. После окончания считывания из БЗУ триггер переходит в нулевое состояние и единичный потенциал с его инверсного выхода поступает на вход элемента И 10 и разблокировьшает его. Единичный потенциал записи со входа 12 через разблокированный злемент И 10 поступает на вход триггера 7 и далее цикл записи выполняется аналогично случаю (а). При этом цикл записи задерживается максимум на величину . . Если в случае (в) на входе 14 син хронизации первым возникает передний фронт импульса Т., то первым в еди ничное состояние устанавливается триггер 7 (момент времени м на фиг.2) и выполняется цикл записи аналогично случаю (а). В цикле записи нулевой потенциал с инверсного выхода триггера 7 поступает на вход элемента И 11 и блокирует его. При этом триггер 9 продолжает оставаться в нулевом состоянии до окончания ,цикла записи, поскольку элемент И 11 блокирует прохождение сигнала считывания на вход триггера 9. После завершения цикла записи в БЗУ триггер 7 переходит в нулевое состояние и единичный потенциал с его инверсного выхода поступает на вход элемента И 11 и разблокировьшает его. Единичньш потенциал считывания через разблокированный элемент И 11 поступает со входа 13 на вход триггера 9 и далее цикл считьюания выполняется аналогично случаю (б). При этом длительность цикла считывания увеличивается максимум на величину IAH Т,. Функционирование счетчиков устройства, формирукйцих текущее значение адресов записи и считывания в процессе работы БЗУ, а также состояние реверсивного счетчика 8 представлены на фиг. 3. Здесь для примера показана запись последовательности информационных слов: А,В,Г,Д,Е,Ж,3,, которые записываются в накопитель 1 в порядке возрастания счетчика 5. При считывании информации из БЗУ текущий адрес формирует счетчик 4. Состояния последнего всегда повторяют состояния счетчика 5 (фиг. 3), в результате чего на выходе БЗУ считывается такая же последовательность информационных слов: А,В,Г, , причем в процессе работы счетчики 4,5 могут периодически переполняться, не нарушая правильной работы БЗУ. Коэффициенты пересчета счетчиков 4, 5 и 8 равны между собой и соответственно равны объему накопителя 1.

7 11112028

Таким образом, процесс считывания(фиг. 28) и выполняются со скоростью

из БЗУ вцполняется в порядке поступ-обработки информации потребителем в .

пения информации в БЗУ от абонентов-произ-вольные моменты времени,При этом

источников. Отдельные циклы считыва-предлагаемое устройство позволяет прония информационных слов могут следо-5 изводить запись и считывание информации

вать i произвольные моменты временив порядке ее поступления от абонентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048515A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1991 |

|

SU1789986A1 |

| Буферное запоминающее устройство | 1976 |

|

SU583478A1 |

| Устройство для сопряжения процессоров | 1982 |

|

SU1053097A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, одни входы и выходы которого являются соответственно информационными входами и выходами устройства, другие входы накопителя подключены к выходам коммутатора, одни информационные входы коммутатора подключены к выходам первого счетчика, другие входы коммутатора подключены к эыходам второго счетчика, управляющий вход коммутатора подключен к одному выходу первого триггера, второй дешифратор, отличающееся тем, что, с целью расширения области применения устройства за счет возможности попеременной записи и считывания информации, оно содержит реверсивный счетчик, второй триггер и элементы И, выход первого из которых подключен к первому входу первого триггера, другой выход которого является первым управляющим выходсгм устройства, выход второго элемента И подключен к первс у входу триггера, один выход которого подключен к. входу первого счетчика, jc первому входу реверсивного счетчика-и первому входу первого элемента И, второй вход которого является первым управляющим входом устройства, другой выход второго триггера является вторым управляющим выходом устройства, другой выход первого триггера подключен к входу второго счетчика, к второму входу реверсивного счетчика, j и первому входу второго элемента И, второй вход является вторым управляювщм входом устройства, третий вход второго элемента И подключен к выходу второго дешифратора, входы которого подключены к выходам реверсивного счетчика, второй вход первоК) го триггера подключен к второму вхор ду второго триггера и является третым управляющим входом ycfpoйSD ства.

Входная инфор почия

JS

BbixoSHOU инфор нация

tPut. f

f1

Л

(риг, 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1974 |

|

SU515154A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-08-30—Публикация

1982-11-26—Подача