элемента И подключен к выходу первого элемента ИЛИ и первому входу четвертого элемента И, а выход - к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход подключен к входам первого триггера и элемента НЕ, выход которого соединен с одним из входов второго триггера, другие входы которого подключены к выходу четвертого элемента И, второй вход которого и вторые входы элементов 2И-ИЛИ подключены к первому выходу второго формирователя сишалов, второй выход которого coejEQffleH с первыми входами шестого и седьмого элементов И, вторые входы второго и седьмого элементов 1 и третьи входы элементов 2И-ИЛИ подключены к прямому выходу первого триггера, инверсный выход которого соединен с вторыми входами третьего и шестого элементов И и четвертыми входами элементов

96692

2И-ИЛИ, пятые входы которых и третьи входы четвертого, шестого и седьмого элементов И подключены к инверсному выходу второго триггера, первый и второй вход первого элемента ИЛИ, третий вход первого элемента И и вход первого формирователя сигналов являются соответственно входами с первого по четвертьга блока, вход второго формирователя сигналов и первый вход пятого элемента И объединены и являются пятым входом блока, шестым входом которого является второй вход пятого элемента И, другой выход первого формирователя сигналов, выходы второго и третьего элементов И и выходы первого и второго элемен;ТОВ 2И-ИЛИ являются соответственно выходами с первого по пятый блока, выходами с шестого по восьмой которого являются выходы шестого и седьмого элементов И и третий выход второго формирователя сигналов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1522220A1 |

| Устройство для ввода информации | 1979 |

|

SU911500A2 |

| Буферное запоминающее устройство | 1984 |

|

SU1226530A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

Изобретение относится к вычислительной технике и может использоваться в устройствах передачи данных. Известно устройство, содержашее блок управления, генератор импульсов,,входной регистр, элементы И, матрицу оперативной памяти, выходной регистр, счетчики адресов записи и считывания, элемент ИЛИ и дешифратор адресов 1. Недостатками устройства являются его сложность и недостаточное быстродействие. Наиболее близким техническим решением к предлагаемому является буферное запоминаюшее устройство, содержашее регистр вход. ного слова, входные элементы И, счетчики адресов, дешифраторы адресо два накопителя, выходные элементы И, элементы ИЛИ, регистр выходного слова, дешифратор маркер конца сообщений и блок управления, причем информационные входы первого и второго накопителей подключены к выходам элементов И соответственно первой и второй группы, а адресные входы - соответственно к вы ходам первого и второго дешифраторов, упра ляЮидае входы которых подключень к соответствующим выходам блока управления, информационные входы первого и второго деш фраторов подключены соответственно к выходам первого и второго счетчиков, управляющие входы которых подключены к соответствующим выходам блока управления, ий-, формационные выходы первого и второго , накопителей подключены к одним входам элементов И соответственно третьей и четвертой групп, другие входы которых подключены к соответствующим выходам блока управления, выходы элементов И третьей группы подключены к одним входам элементов ИЛИ группы, другие входы которых подключены к выходам элементов И четвертой группы, одни входы элементов И первой и второй групп подключены к выходам первого регистра, управляющий вход которого подключен к соответствующему выходу блока управления, другие входы элементов И первой и второй групп подключены к соответствующим выходам блока управления, выходы элементов ИЛИ группы подключены к инфррмащюнным входам второго регистра, первый управляющий вход которого подключен к соответству ющему выходу блока управления, элемен 2И-ИЛИ, первые входы которого подключены к соответствующим выходам первого и второго дешифраторов, а вторые входы - к соответствующим выходам блока зправления, выход элемента 2И-ИЛИ подключен к второму управляющему входу второго регистра, входы третьего дешифратора подключейы к выходам первого регистра, выход третьего дешифратора и соответствующие

выходы первого и второго дешифраторов подключены к входам блока управления 2.

Недостатком устройства является невысокая достоверность информации при считывании, обусловленная тем, что БЗУ ие позволяет фиксировать сообщение, в момент считывания которого в источнике сообщений произошел отказ.

Цель изобретения - повышение достоверности считываемой информации за счет возможности фиксации сообщения при необратимой сбойной ситуаций в источнике сообще ний и передачи его в приемник сообщений.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее дешифраторы, регистры, счетчики, группы злементов И, элементы ИЛИ, элемент И-ИЛИ, блок .управления, первый и второй иакопитепи, информационные входы которых подключены соответственно к выходам элементов И первой и второй групп, адресные входы - соответственно к одним из выходов первого и второго дешифраторов, информационные входы которых соединены с выходами первого и второго счетчиков соответственно, причем выходы первого и второго накопителей подключены к nejb вым входам элементов И третьей и четвертой групп соответственно, выходы элементов И третьей группы соединены с первыми входами элементов ИЛИ, вторые входы которых подключены к выходам элементов И четвертой группы, выходы первого регистра соединены с первыми входами элементов И первой и второй групп и входами третьего дешифратора, выхой которого соединен с первым входом блока управления, выходы элементов ИЛИ подключены к информационным входам второго регистра, вход считьтаипя которого соединен с выходом элемента И-ИЛИ, первый вход которого подключен к другому выходу первого дешифратора и . второму входу блока управления, третий вход которого соединен с другим выходом второго дешифратора и вторым входом элемента И-ИЛЙС третий и четвертый входы которого подключены к вторым входам элементов И третьей и четвертой групп соответственно, вход записи первого регистра вторые входы элементов И первой и втррой групп соответственно соединены с выходами с первого по третий блока управления, четвертый и пятый выходы которого подключены соответственно к управляющим входам первого счетчика и первого дешифратора и к управляющим входам второго счетчика и второго дешифратора, выходы с шестого по восьмой блока управле-.

ния соединены соответственно с третьим и . с четвертым входами элемента И-ИЛИ и с входом записи второго регистра, выходы которого являются выходами устройства, информационными входами которого являются информационные входы первого регист- . ра, а входами синхронизации записи и считывания являются соответственно четвертый и пятый входы блока управления, введены

третий счетчик и четвертый дешифратор, входы которого подключены к выходам третьего счетчика, установочный вход которого соединен с выходом третьего дешифратора, а счетный вход - с пятым входом блока управления, адестой вход которого подключен к. выходу четвертого дешифратора. Кроме того, блок управле1шя содержит формирователи сигналов, триггеры, первый и второй элементы 2И-ИЛИ, элементы ИЛИ,

элемент НЕ, элементы И, причем одни из выходов первого формирователя сигналов соединены с первыми входами первого элемента И и элементов 2И-ИЛИ и с первыми входами второго и третьего элементов И, второй вход первого элемента И подключен к выходу первого элемента ИЛИ и первому входу четвертого элемента И, а выход - к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход подключен к входам первого триггера и элемента НЕ, выход которого соединен с одним из входов второго триггера, другие выходы которого подключены к выходу четвертого элемента И, второй

вход которого и вторые входы элементов

2И-ИЛИ подключены к первому выходу формирователя сигналов, второй вход которого соединен с первыми входами шестого и седьмого элементов И, и третьи входы элементов

:2И-ИЛИ подключены к прямому выходу первого триггера, инверсный выход которого соединен с вторыми входами третьего и шестого элементов И и четвертыми входами элементов 2И-ИЛИ, пятые входы которых и

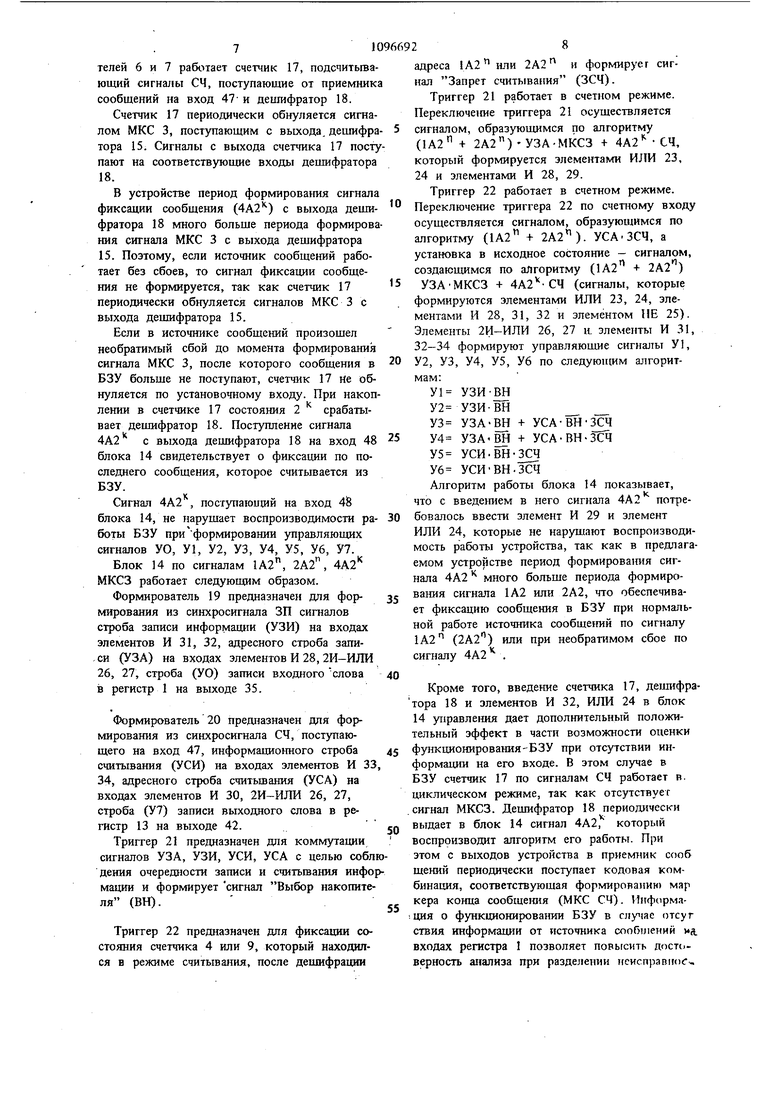

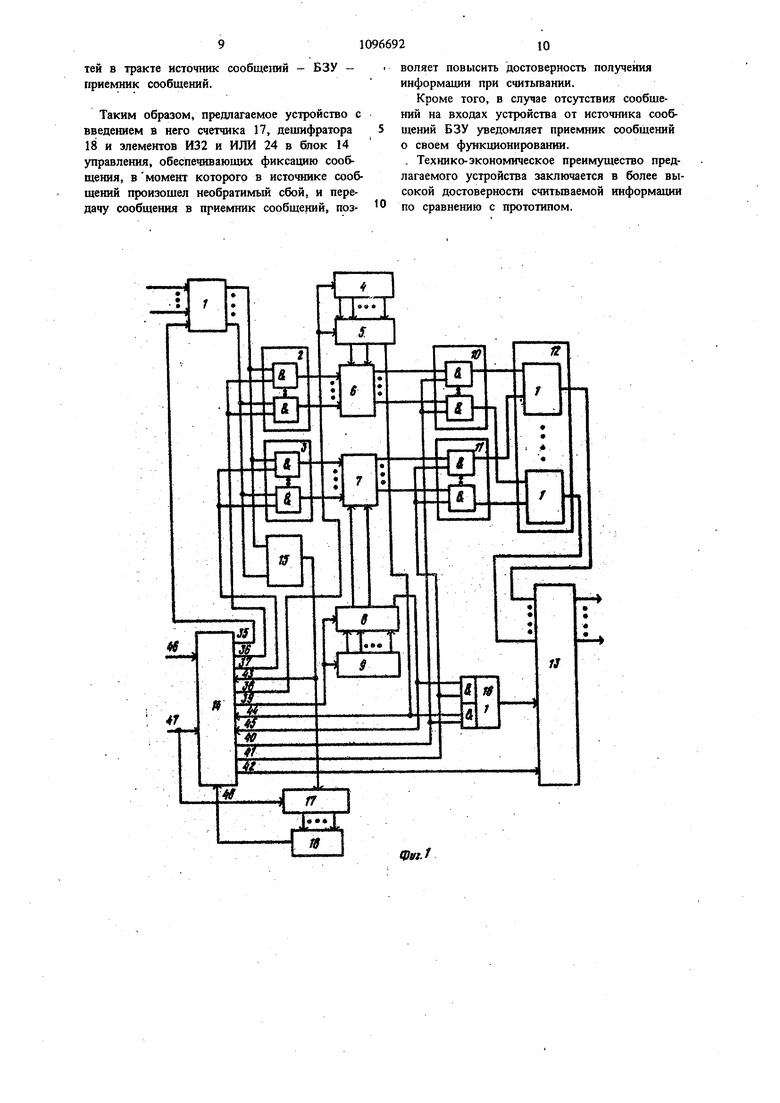

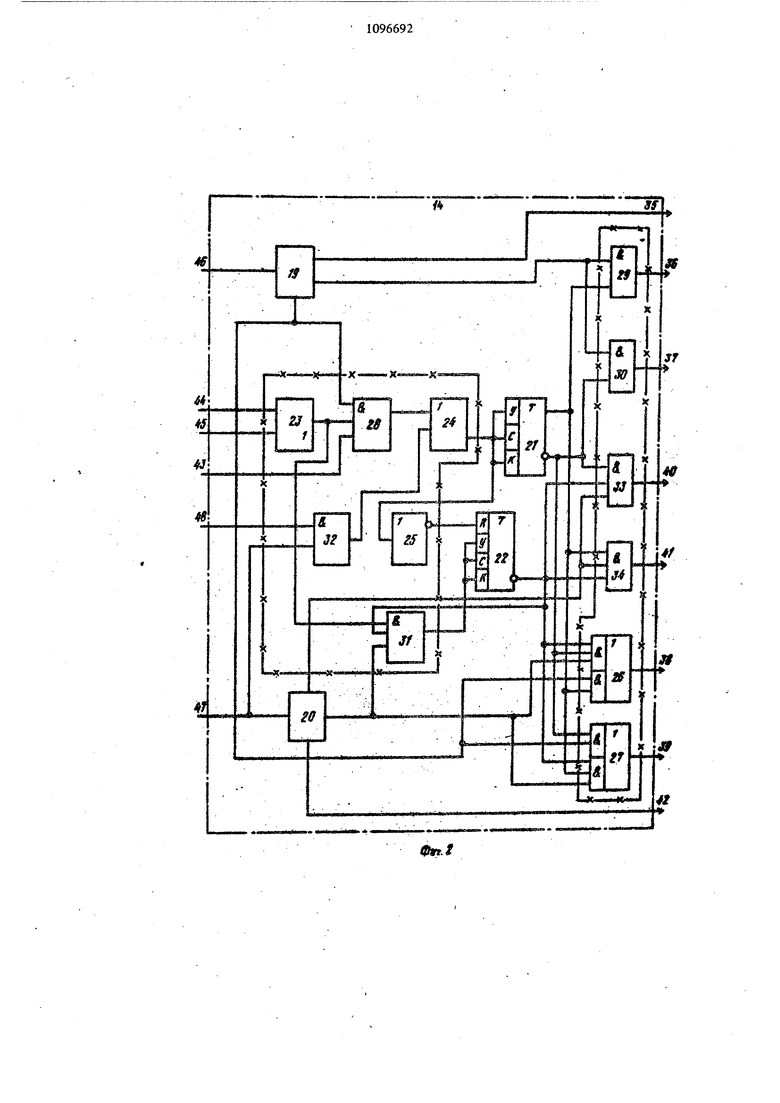

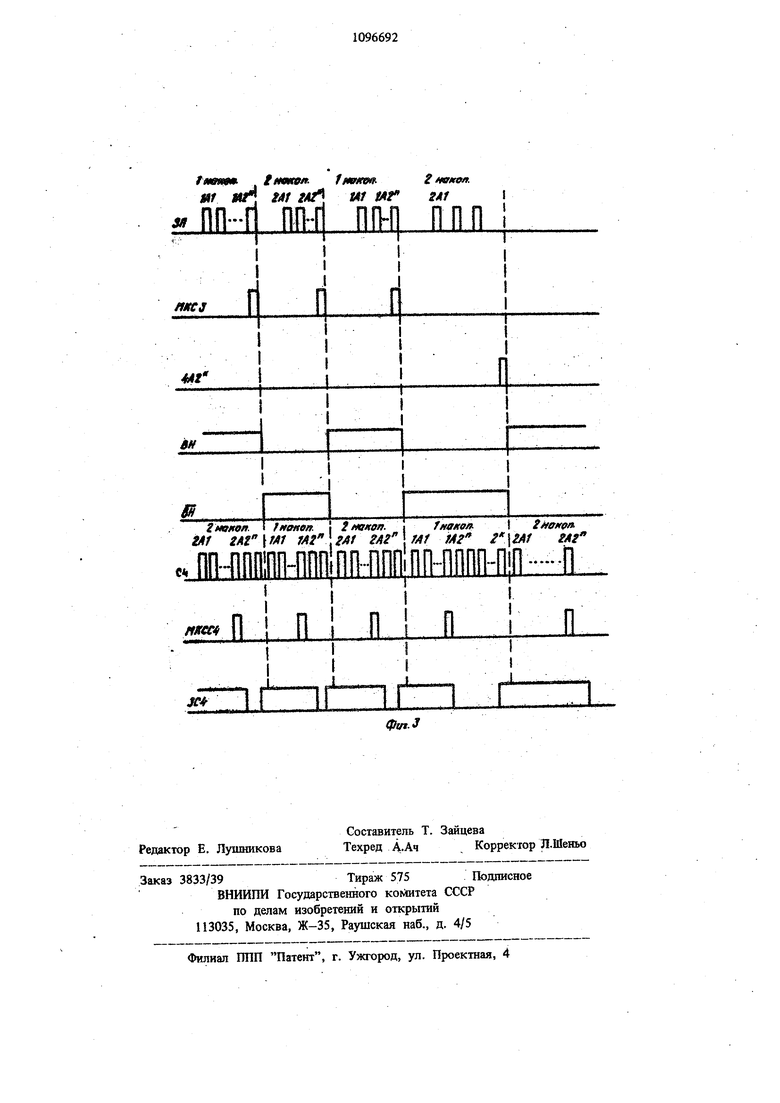

третьи входы четвертого, шестого и седьмого элементов И подключены к инверсному выходу второго триггера, первый и бторой вход первого элемента ИЛИ, третий вход элемента ИЛИ и вход первого формирователя сиг-налов являются соответственно входами с первъго по четвертый блока, вход второго формирователя сигналов и первый вход пятого элемента И объединены и являются пятым входом блока, ш,естым входом которого является второй вход первого формирователя сигналов, выходы второго и третьего элементов И и выходы первого и второго элементов 2И-ИЛИ являются соответственно выходами с -Первого по пятый блока, выходами с шестого по восьмой которого являются выходы шестого и седьмого элементов И и третий выход второго формирователя сигналов соответственно. На фиг. 1 представлена функшюнальиая схе ма устройства; на фиг. 2 - функциональная схема блока управления, на фиг. 3 - временная диаграмма работы устройства. Устройство содержит (фиг. 1) первый регистр 1, первую 2 и вторую 3 группы элементов И,. первый счетчик 4, первый дешифра тор 5, первый б и второй. 7 накопители, второй дешифратор 8, второй счетчик 9, третью 10 и четвертую 11 группы элементов И, эле; менты ИЛИ 12, второй регистр 13, блок 14 управления, третий дешифратор 15, элемент И-ИЛИ 16, третий счетчик 17 и четвертый дешифратор 18. Блок 14 управления содержит (фиг. 2) пер вый 19 и второй 20 формирователи сигналов, первый 21 и второй 22 триггеры, первый 23 и второй 24 элементы ИЛИ, элемент НЕ 25, первый 26 и второй 27 элементы 2И-ИЛИ, первый-седьмой элементы И 28-34. На фиг. 1 и фиг. 2 обозначены выходы с первого по восьмой 35-42 и входы с первого по шестой 43-48 блока управления. Счетчик 17 может быть выполнен на интегральных схемах серии 134ИБ5, а дешифратор 18 - на интегральных схемах серии 134ЛБ2, 134ЛБ1. На фиг. 3 обозначены адресные сигналы 1А1-1А2 (где п - разрядность счетчиков 4, 9), сигналы МКСЗ маркера конца сообше4А2фиксации сообше ния по записи, сигнал ния (где к - разрядность счетчика 17), прямые ВН и инверсные ВН сигналы Выбор накопителя, формируемые триггером 21, сигналы С4 считывания, сигналы МКСС4 маркера конца сообщения по считыванию и сигналы ЗС4 Запрет считывания, формируемые на . выходе триггера 22. Устройство работает следующим образом. Слова сообщения, сопровождаемые синхроимпульсами записи (ЗП), поступают параллель но-последовательно от источника сообщений и информационные входы регистра 1 (фиг. 1). Блок 14 формирует из синхроимпульсов ЗП сигналы УО, У1, УЗ на выходах 35, 36, 38 соответственно, если запись осуществляется в накопитель 6, или сигналы УО, У2, У4 на выходах 35, 37, 39, если запись осушествляется в накопитель 7. По сигналу УО входное слово записывается в регистр 1. Сиг нал У1 разрешает перезапись входного слова в накопитель 6, а сигнал У2 - в накопитель 7. Последовательная выборка адресов накопителей б и 7 осуществляется соответственно с помошью счетчиков 4, 9 и дешифраторов 5 и 8. Выборка адреса разрешается сигналом УЗ для накопителя 6 и сигналом У4 для накопителя 7. Изменение состояния счетчика 4 осушествляется по заднему фронту сигнала УЗ, а счетчик 9 - по заднему фронту сигнала У4. Каждому состоянию любого из счетчиков 4 и 9 соответствует определенная ячейка связанного с ним накопителя 6 и 7 соответственно, за исключением последнего состояния. Последнее слово сообшения в накопители б и 7 не записывается. При записи в регистр 1 входного слова, содержашегО кодовую комбинацию, соответствуюшую последнему состоянию счетчика 4 или 9, дешифратором 15 формируется сигнал маркера конца сообшения по записи (МКСЗ), поступающий в блок 14. Совпадение сигнала МКСЗ с соответствуюшим из сигналов адреса последнего состояния 1А2 (2А2), формируемых дешифрато рами 5 и 8 при записи информации, свидетельствует о фиксации сообшения в соответствующем накопителе 6 или 7, куда проводилась запись. Если запись проводилась в накопитель 6, то по совпадению сигналов МКСЗ и 1А2 блок 14 дает разрешение на считывание информации из накопителя 6 и запись информации в накопитель 7 от источника сообщений. Считывание информации из БЗУ осушествляется синхроимпульсами считывания (СЧ), поступающими на вход 47 от приемника сооб щений непрерывно. Блока 14 формируют из сиюсроимп}льсов СЧ сигнала У4, У6, У7 на выходах 39, 41, 42 соответственно во время считывания информации из накопителя 7 или сигналы УЗ, У5, У7 на выходах 38, 40, 42, если считывание осуществляется из накопителя 6. По сигналу У7 осушествляется запись выходного слова в регистр 13. Если любой из счетчиков 4 или 9, работающий на считьгеание, находится в последнем состоянии, то на выходе деитфратора 5 (или 8) появляется сигнал 1А2 (или 2А2), прохождение которого на установочный вход регистра 13 через элемент И-ИЛИ 16 разрешается сигналом У5 при считывании информации из , накопителя 6 или сигнагюм У6 при считыва НИИ сообщения из накопителя 7. Сигнал с выхода элемента И-ИЛИ 16 поступает на тановочный вход регистра 13 и обеспечивает появление на его выходах кодовой комбина щи маркера конца сообшения по считыванию (МКС СЧ). Одновременно с поочерещгым процессом за1гаси и считьгаания информаши из накопи телей 6 и 7 работает счетчик 17, подсчитьгеа ющий сигналы СЧ, поступающие от приемник сообщений на вход 47- и дешифратор 18. Счетчик 17 периодически обнуляется сигна лом МКС 3, поступающим с выхода, дешифр тора 15. Сигналы с выхода счетчика 17 пост пают на соответствующие входы дещифратора 18. В устройстве период формирования сигнала фиксации сообщения (4А2) с выхода деши фратора 18 много больще периода формиров ния сигнала МКС 3 с выхода дешифратора 15. Поэтому, если источник сообщений работает без сбоев, то сигнал фиксации сообщения не формируется, так как счетчик 17 периодически обнуляется сигналов МКС 3с выхода дешифратора 15. Если в источнике сообщений произошел необратимый сбой до момента формирования сигнала МКС 3, после которого сообщения в БЗУ больше не поступают, счетчик 17 не обнуляется по установочному входу. При накоп лении в счетчике 17 состояния 2 срабатывает дешифратор 18. Поступление сигнала 4А2 с выхода дешифратора 18 на вход 48 блока 14 свидетельствует о фиксации по последнего сообщения, которое считьшается из БЗУ. Сигнал 4А2 , поступающий на вход 48 блока 14, не нарушает воспроизводимости работы БЗУ приформировании управляющих сигналов УО, У1, У2, УЗ, У4, У5, У6, У7. Блок 14 по сигналам 1А2, 2А2, 4А2 МКСЗ работает следующим образом. Формирователь 19 предназначен для формирования из синхросигнала ЗП сигналов строба записи информащш (УЗИ) на входах элементов И 31, 32, адресного строба запи,си (УЗА) на входах элементов И 28, 2И-ИЛИ 26, 27, строба (УО) записи входного слова в регистр 1 на выходе 35. Формирователь 20 предназначен для формирования из синхросигнала СЧ, постзшающего на вход 47, информацио1шого строба считывания (УСИ) на входах элементов И 33 34, адресного строба считьшания (УСА) на входах элементов И 30, 2И-ИЛИ 26, 27, строба (У7) записи выходного слова в регистр 13 на выходе 42. Триггер 21 предназначен для коммутации сигналов УЗА, УЗИ, УСИ, УСА с целью соблю дения очередности записи и считьшания инфор мации и формирует сигнал Выбор накопителя (ВН). Триггер 22 предназначен для фиксации состояния счетчика 4 или 9, который находился в режиме считывания, после дешифрации адреса 2А2 и формирует сигнал Запрет считывания (ЗСЧ). Триггер 21 работает в счетном режиме. Переключение триггера 21 осуществляется сигналом, образующимся по алгоритму (1А2 + 2А2)-УЗА-МКСЗ + 4А2-СЧ, который формируется элементами ИЛИ 23, 24 и элементами И 28, 29. Триггер 22 работает в счетном режиме. Переключение триггера 22 по счетному входу осуществляется сигналом, образующимся по алгоритму (1А2 + 2А2). УСА.ЗСЧ, а установка в исходное состояние - сигналом, создающимся по алгоритму (1А2 + 2А2 ) УЗ АМКСЗ + (сигналы, которые формируются элементами ИЛИ 23, 24, элементами И 28, 31, 32 и элементом НЕ 25). Элементы 2И-ИЛИ 26, 27 а элементы И 31, 32-34 формируют управляющие сигналы У1, У2, УЗ, У4, У5, У6 по следующим алгоритмам:У1 УЗИ-ВН У2 УЗИ-ВН У3 УЗА-ВН + УСА-ВНЗСЧ У4 УЗА-ВН + УСА-ВН-ЗСЧ У5 УСИ.ВН-зет У6 УСИВН.ЗСЧ Алгоритм работы блока 14 показывает, что с введе1гаем в него сигнала 4А2 потребовалось ввести элемент И 29 и элемент ИЛИ 24, которые не нарушают воспроизводимость работы устройства, так как в предлагаемом устройстве период формирования сигнала 4А2 много больше периода формирования сигнала 1А2 или 2А2, что обеспечивает фиксацию сообщения в БЗУ при нормальной работе источника сообще1тй по сигналу 1А2 (2А2) или при необратимом сбое по сигналу 4А2 . Кроме того, введение счетчика 17, депшфратора 18 и элементов И 32, ИЛИ 24 в блок 14 управлещш дает дополнительный положительный эффект в части возможности оценки фу1жционированияБЗУ при отсутствии информации на его входе. В этом случае в БЗУ счетчик 17 по сигналам СЧ работает в. циклическом режиме, так как отсутствует сигнал МКСЗ. Дешифратор 18 периодически выдает в блок 14 сигнал 4А2, который воспроизводит алгоритм его работы. При этом с выходов устройства в приемник сооб щений периодически поступает кодовая комбинация, соответствующая формированию мяр кера конца сообщега1я (МКС СЧ). Иифсфмация о функционировании БЗУ в сл 11ае отсуг ствия информации от источника сооб1леиий ид. входах регистра 1 позволяет повысить достсверность анализа при разделении неиспрзшгос

тей в тракте источник сооб1це1шй - БЗУ гфиемник сообщений.

Таким образом, предлагаемое устройство с введением в него счетчика 17, дешифратора 18 и элементов И32 и ИЛИ 24 в блок 14 управления, обеспечивающих фиксацию сообщения, вмомент которого в источнике сообщений произошел необратимый сбой, и передачу сообщения в приемник сообщений, позволяет повысить достоверность получения информации при считывании.

Кроме того, в случае отсутствия сообщений на входах устройства от источника сообщений БЗУ уведомляет приемник сообщений о своем функционировании. . Технико-экономическое преимущество предлагаемого устройства заключается в более высокой достоверности считьгоаемой информации по сравнению с прютотипом.

Гдюж /MMV/r. //«imvteiгнагю.

i «И w/ /дг ш гх/

r| Щ п п п

ж

г и тг

J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1974 |

|

SU515154A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-06-07—Публикация

1983-03-10—Подача