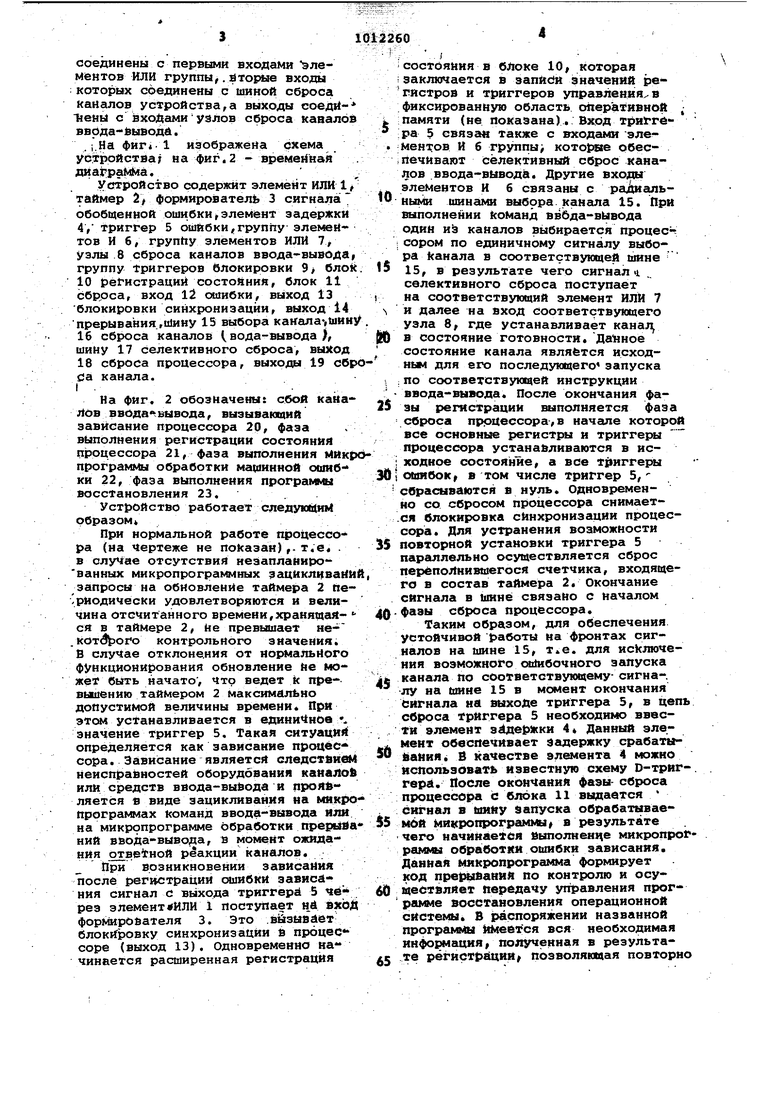

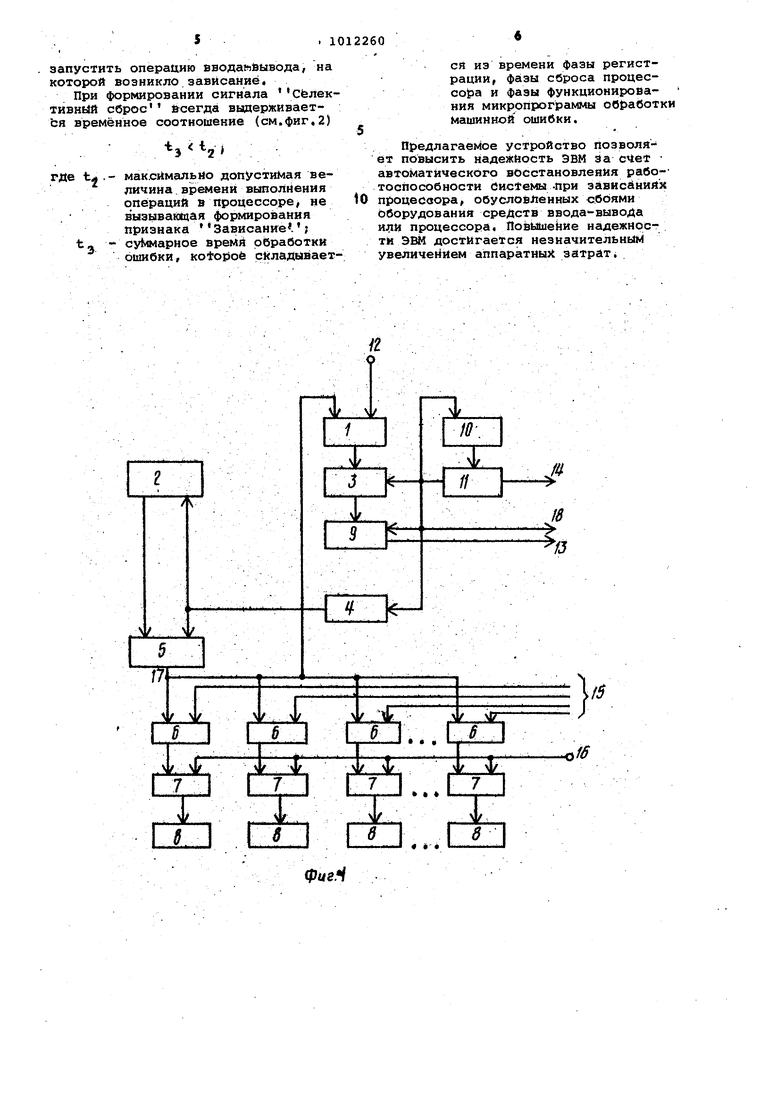

Изобретение относится к област вычислительной техники и может быть использовано в ЭВМ, включаиед процессоры и каналы ввода-вывода. Известно диагностическое устройство, содержащее блок контроля и диагностики и блок интервальног таймера, который соединен с блоком центрального управления и с блоком управления памятью. Устрой во автоматически обрабатывает ошибки, фиксируемые схемами контроля процессора, т.е. производится аппаратное повторение сеойной ситуации и выполняется расширенная регистрация состояния процессора I для последующего программного повто ния на уровне операционной системл.Н ряду с этим устройство позволяет опр делить дя:1ибки,не фиксируемые схемам контроля процессора, которые приводят к зависанию процессора на неопределенное время 1 Недостаток известного устройства заключается в невозможности автоматической обработки ошибок данного типа (ошибок зависания). Наиболее близким по технической сущности к предлагаемому является диагностическое устройство , системы обработки данных, содержащее блок контроля и диагностики, блок интервального таймера, триггер ошибки зависания, шину управления памятью, ши ну запроса на обновление, шину сброса, шину аппаратных ошибок про цессора, шину запуска обрабатывающей микропрограммы, шины выбора канала, шину сброса системы, причем первый вход блока контроля и диагностики соединен с шиной аппаратных ошибок процессора, первый выход блока контроля и диагностики соединен с шиной запуска обрабатывающей микропрограммы, первый вход блока интервального таймера соединен с шиной сброса, первый выход блокаинтервального таймера соединен с шиной управления памятью, вт рой выход блока интервального таймера соединен с шиной запроса на обновление, третий выход блока интервального таймера соединен с установочным входом триггера ошибки зависания 2. Данное устройство автоматически обраба тывает ошибки, фиксируемые схемами контроля процессора, и определяет ошибки зависания. Зависание может быть обусловлено как неисправностями оборудования . процессора (менее вероятная причина) , так и неисправностями оборудования средств ввода-вывода более вероятная причинЪ) . Под средствами ввода-вывода понимаются каналы и устройства ввода-вывода. Если ошибка зависания вызвана сбоем оборудования средств вводавывода, то для устранения причины зависания требуется ручное вмешательство обслуживающего персонала, при котором нарушается непрерывность вычислительного процесса. Причем время, затрачиваемое на восстановление работоспособности системы, может быть значительным, поскольку зависит от квалификации персонала. Если ошибка зависания вызвана сбоем оборудования процессора, то в этом случае также не обеспечивается возможность автоматического восстановления работоспособности, системы. Недостатком устройства является невозможность автоматически обрабатывать ошибки зависания и . восстанавливать работоспособность системы обработки данных без участия обслуживающего персонала. Цель изобретения - повышение надежности ЭВМ за счет автоматического восстановления работоспособности в случаях зависания процессора. Поставленная цель достигается тем, что в устройство, содержащее узлы сброса каналов ввода-вывода, таймер, формирователь сигнала обобщенной ошибки, группу тригеров блокировки, блок регистрации состояния, блок сброса и триггер ошибки, причем выход таймера соединен с первым входом триггера ошибки, первый выход блока сброса соединен с первыми входами формирователя сигнала обобщенной ошибки, трйГ геров блокировки группы и входом блока регистрации состояния, а второй выход является выходом пре рывания устройства вход блока сброса соединен с. выходом блока регистрации состояния, выход формирователя сигнала обобщенной ошибки соединен с вторыми входами триггеров блокировки группы, выходы которых являются выходами блокировки синхронизации устройства, введены элемент ИЛИ, элемент задержки, группа элементов Ни группа элементов ИЛИ, причем первый и второй входы элемента ИЛИ соединены соответственно с выходом триггера ошибки .и входом ошибки устр9йства, а выход соединен с вторым входом формирователя сиг-; нала обобщенной ошибки, первый выход блока сброса через элемент задержки соединен с входом таймера и вторым входом триггера ошибки, выход которого соединен с первыми входами элементовИ группы, вторые входы которых соединены с шиной выбора канала устройства, а выходы соединены с первыми входами элементов ИЛИ группы,.иторые входы которых соединены с шиной сброса каналов устройства,а выходы соедй Немы узлов сброса кавало ввода выводи. . i.Ha иэображейа схема устройства; на фиг,2 - временная диатраШа. Устройство содержит элемейт ИЛИ 1 таймер 2/ формирователь 3 сигнала обобщенной ошибки -, элемент задержки 4/ триггер 5 ошибки,группу элементов И 6, rpyntiy элементов ИЛИ 1, УЗЛЫ 8 сброса каналов ввода-вывода группу Триггеров блокировки 9 бло 10 регистрации состойния, блок 11 ебррса, вход 12 ошибки, выход 13 блокировки синхронизации, выход 14 прерывания.,Шину 15 выбора канала-,1иин 16 сброса каналов i вода-вывода ), шину 17 селективного сброса, выход 18 сброса процессора, выходы 19 сб Са канала. На фиг. 2 обозначены: сбой кана лов вводв вывода, вызывающий зависание процессора 20, фаза . выполнения регистрации состояния процессора 21, фаза выполнения Мик программы обработки машинной ошибки 22, фаза выполнения программы восстановления 23. , . Устройство работает следующим образом При нормальной работе процессора (ма чертеже не показан),. т.е . в случае отсутствия незапланированных микропрограммных зацикливан запросы на обновление таймера 2 пе рИодически у довлетворяются и величина отсчитанного времени,хранящаяся в тайМере 2, Не превьшает не- . контрольного значения. В случае отклонения от мормальйого функционирования обновление йе може быть начато , что ведет k превыиению таймером 2 максимально допустимой величины времени При этом устанавливается в едини 1нов % значение Триггер 5. Такая ситуаций определяется как зависание процес сора. Зависание является следствием Иеисправностей оборудования канало или средств ввода-выйода и проявляется в виде зацикливания на MMRp программах команд ввода-вывода или на микропрограмме обработки npepbts НИИ ввода-вывода, в момент ожидания ответной реакции каналов. При возникновении зависания Ъосле регистрации ошибки зависания сигнал с выхода триггера 5 чё рез элемент ИЛИ 1 поступает н вхо формирователя 3. Это вйзывйет блокировку синхронизации S процес соре (выход 13). Одновременно начинается расширенная регистрация состояния в блоке 10, которая заключается в запйсШ значений регистров и триггеров управления в фиксированную область оперативной ;памяти (не показана). Вход тризгге;ра 5 связав также с входами элементов И б группы которые обесi печивагот селективный сброс каналов .ввода-вывода. Другие входы элементов И 6 связаны с ра альныкн шинами выбора канала 15. При выполнении Команд ввЬда-вЦвода один из кангшов выбирается процес ;сором по единичному сигналу выбора Канала в соответствующей шине 15, в результате чего сигнала селективного сброса поступает на соответствующий элемент ИЛИ 7 и далее на вход соответствующего узла 8, где устанавливает KaHaj в состояние готовности. Да))ноё состояние канала является исходньм для его последующего запуска ;по соответствующей инструкции ввода-вывода. После окончаиия фазы регистрации выполняется фаза сброса процессора,в начале которой все основные регистры и триггеры процессора устанавливаются в исходное состояНТ1е, а все Т|1иггеры О1|Лбок в том числе триггер 5, сбрасываются в нуль. Одновременно со сбросом процессора снимается блокировка синхронизации процессора. Для устранения возможности повторной установки триггера 5 параллельно осуществляется сброс переполнившегося счетчика, входящего в состав таймера 2. Окончание Сигнала в шине связано с началом фазы сброса процессора. Таким образом, для обеспечения устойчивой работы на фронтах сигналов на шине 15, т.е. для исключения возможного сяйибочного запуска канала по соответствующему-сигна-. лу на шине 15 в момент окончания сигнала на выходе триггера 5, в цепь сброса триггера 5 необходимо вввстй элемент Зе1де| жки 4 Данный элемент обеспечивает задержку срабатыйайия 8 качестве элемента 4 можно использовать известную схему D-триг-. гера. После окончания фазы сброса процессора с блока 11 выдается сигнал в щину запуска обрабатываембй микропрограммы в результате чего начинаемся выполненце микропрог раммы обработки ошибки зависания. Данная микропрограмма формирует код пре{)ыбаний по контролю и осущеотвляет передачу управления прогргшлме восстановления операционной Системы. В {хаспоряжении названной программы йМеется вся необходимая информация, получеииая в результате регистрации, позволяющая повторно

запустить операцию вводарзвывода, на которой возникло зависание.

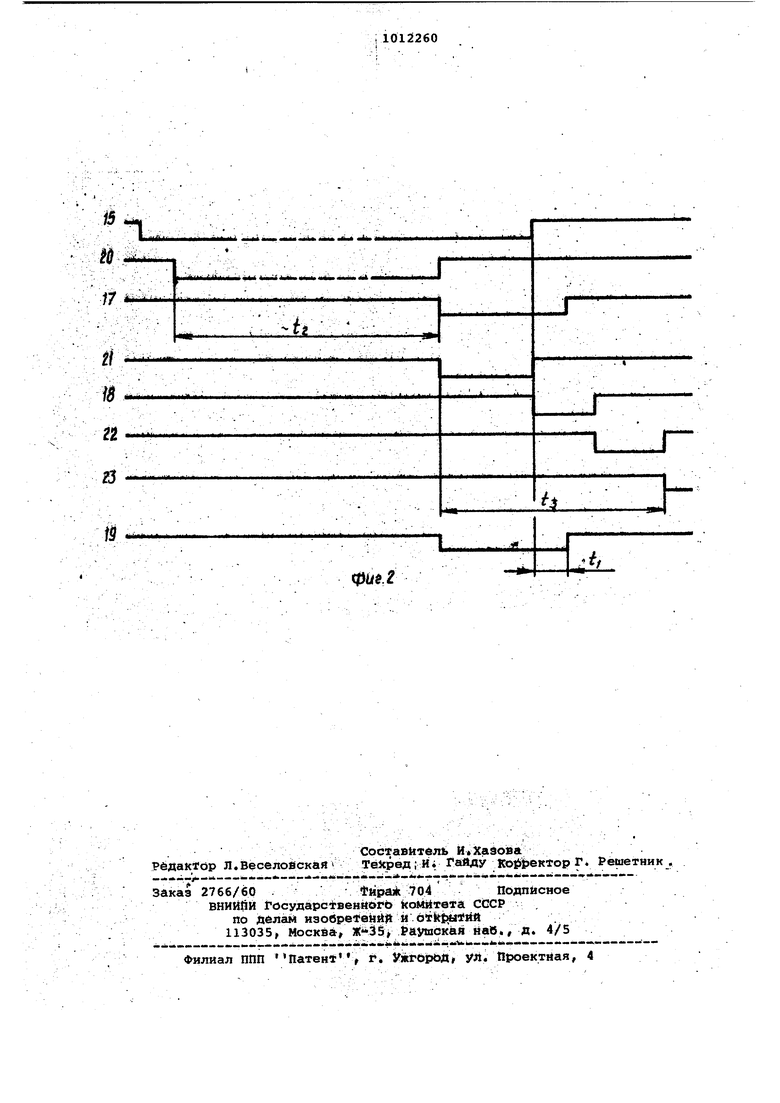

При формировании сигнала сёлективнЫй сброс в сегда выдерживаетЬя временное соотношение (см.фиг,2)

где t . - мак.сймальйо допустимая величина, времени выполнения операций в процессоре, не выэывакхцдя формирования

признака Зависание ; t - cykiMapHoe времй обработки

ошибки, Kotoiioe сйладывается из времени фазы регистрации, фазы сброса процессора и фазы функционирования микропрограммы об)аботк Машинной ошибки.

Предлагаемое устройство позволяет повысить надежность ЭВМ за автоматического восстановления работоспособности Системы -При зависйнийх процессора, обусловленных сбоями оборудования средств ввода-вывода HJiH процессора. ПойЫШейие надежности ЭВМ достигается незначительным увеличеййем аппаратных затрё1Т4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВОЙ АППАРАТУРЫ | 2000 |

|

RU2191422C2 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для контроля канала ввода-вы-ВОдА ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU840869A1 |

| Многоканальное устройство для сбора и предварительной обработки данных при испытаниях электроподвижного состава | 1980 |

|

SU928366A1 |

| Устройство для обнаружения ошибок в блоках контроля процессора | 1980 |

|

SU903886A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

УСТРОЙСТВО ДЛИ ДИАГНОСТИКИ ОШИБОК ЭВМ f содержащее узлы сбро- . са каналов ввода-вывода, таймер, . формирователь сигняла обобщенной. ошибки, группу Триггеров блокировки , бЛок регйстрёщии Состояний, блок сброса и триггер сжшбки, причем выход Таймера соединен с первым входом триггера сниибкй, первый выход блока сброса соединен с первыгми входами формирователя сигнале обобщенной оьшбки, триггеров блокировки группы и входом блока регистрации состояния, а второй выход является выходом прер1:1вани) ует- ройства, вход блока сброса соединен с вшодом блока регистрации состоян, выход формирователи сигНала об6б1ценной ошибки соединен с .вторыми входами триггеров блокиров ки группы, выходы которьЬс являются выходами блокировки синхронизации устройства, о т л и ч а ю щ е с я тем, что, с целью ПОВЕЯИС.ШЯ надежности ЭВМ за счет автоматиЧесIkoro восстановления работоспособн9Стк в случаях зависания процессора, в него ёведены элемент ИЛИ, элемент задержки, группа элементов И и группа элементов ИЛИ,- причем первый и второй входы элемента ИЛИ соединены соответственно с выходом триггера сяоибки и входом ошибки устройства/г а выход соединен с вторым входом формиров.ателя сигнала обобщенной ошибки, первый выход блока сброса через элемент задержки соеДинен с входом таймера и вторым входом триггера ошибки, выход которого соединен с первыми вхопами элементов И группы, вторые входы которых соединены с шиной выбора канала устройства, а выходы соединены с первыми входами эле-, ментов ИЛИ группы, вторые входы которых соединены с шиной сброса . каналов устройства, а выходы соединены d входами узлов сброса канаЛов вводаг вывода.

Фие.

/5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для электрической телескопии | 1924 |

|

SU2050A1 |

| Фехйи еское описание | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Техннчедkoe описание | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

Авторы

Даты

1983-04-15—Публикация

1980-12-24—Подача