(54) УСТРОЙСТВО СОПРЯЖЕНИЯ КОНТРОЛИРУЕМОГО ПРОЦЕССОРА С ОСНОВНОЙ ПАМЯТЬЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1246108A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для управления каналами | 1984 |

|

SU1372329A2 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1316053A1 |

| Устройство для контроля оперативной памяти | 1988 |

|

SU1531177A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1290426A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Устройство для контроля управляющей вычислительной машины | 1990 |

|

SU1815645A1 |

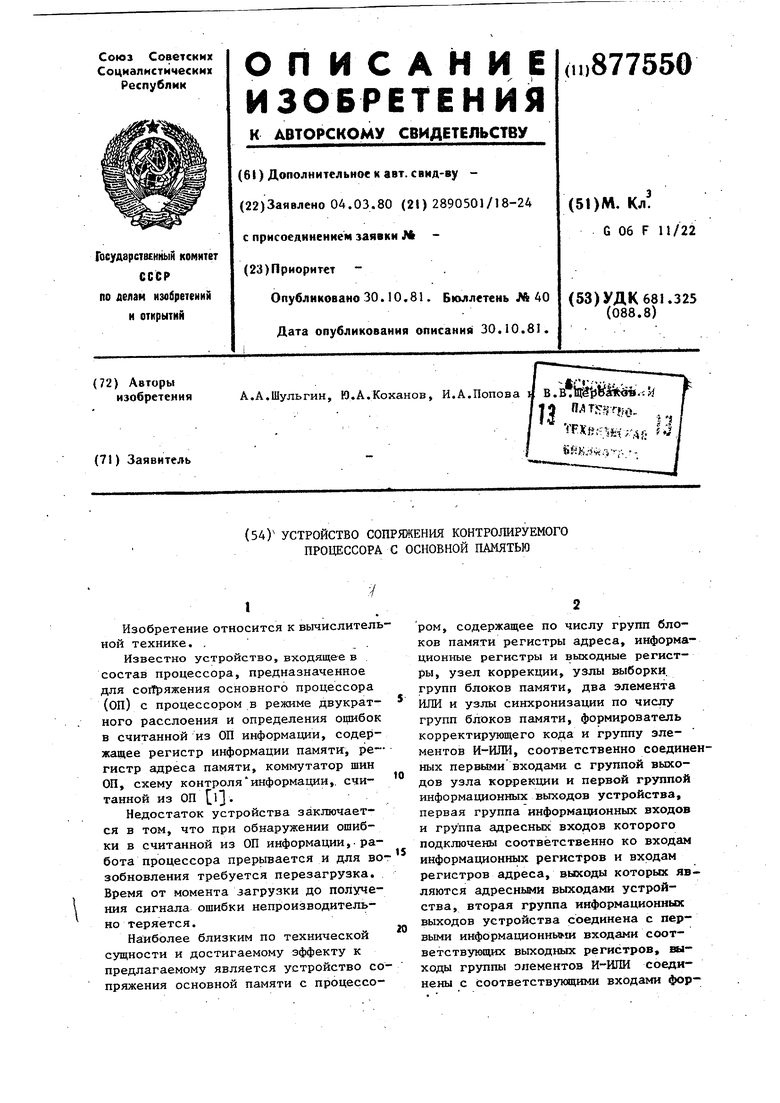

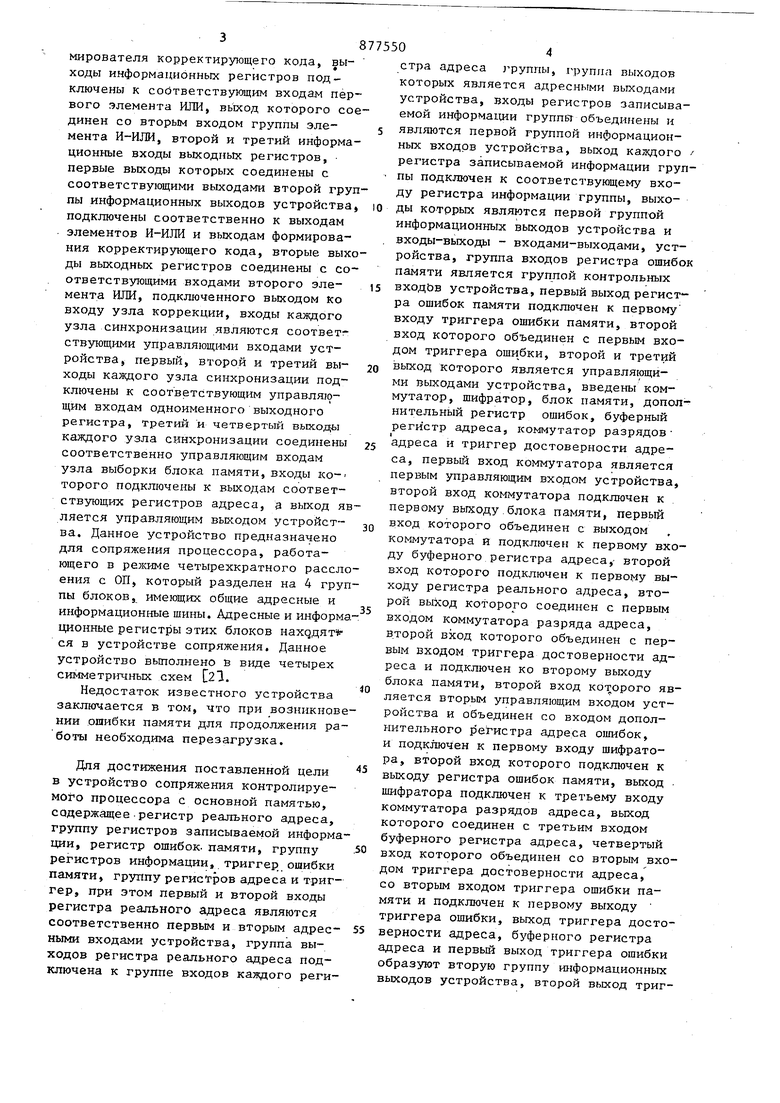

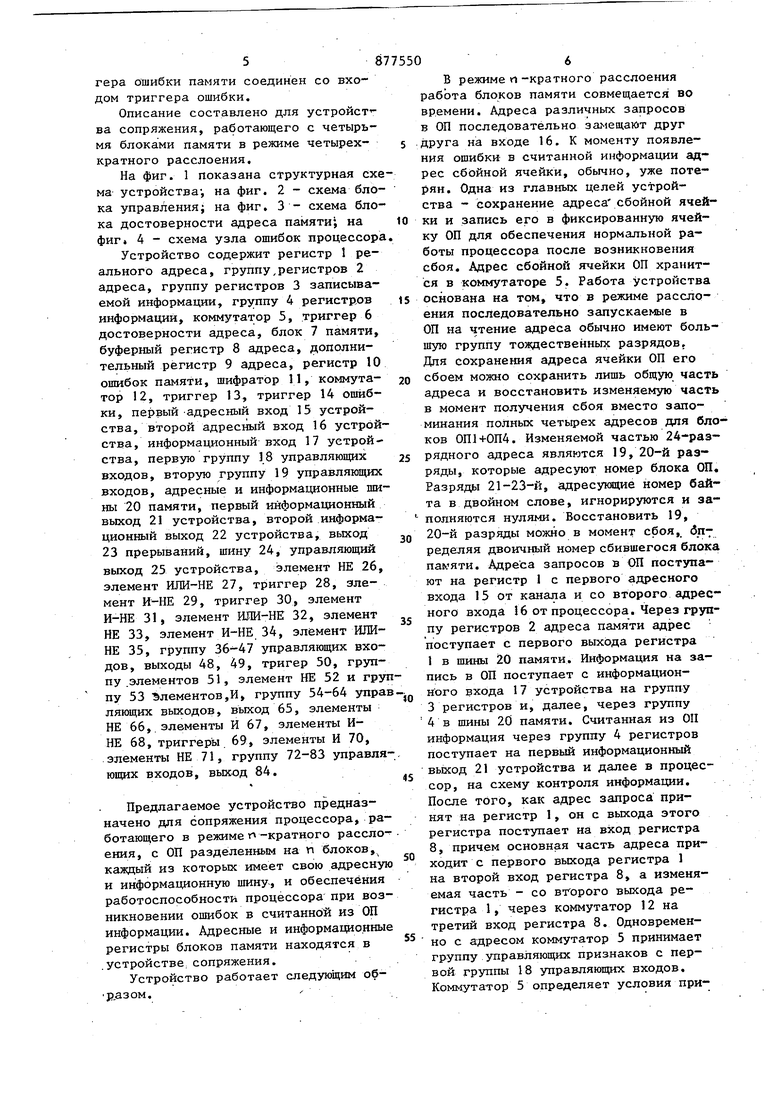

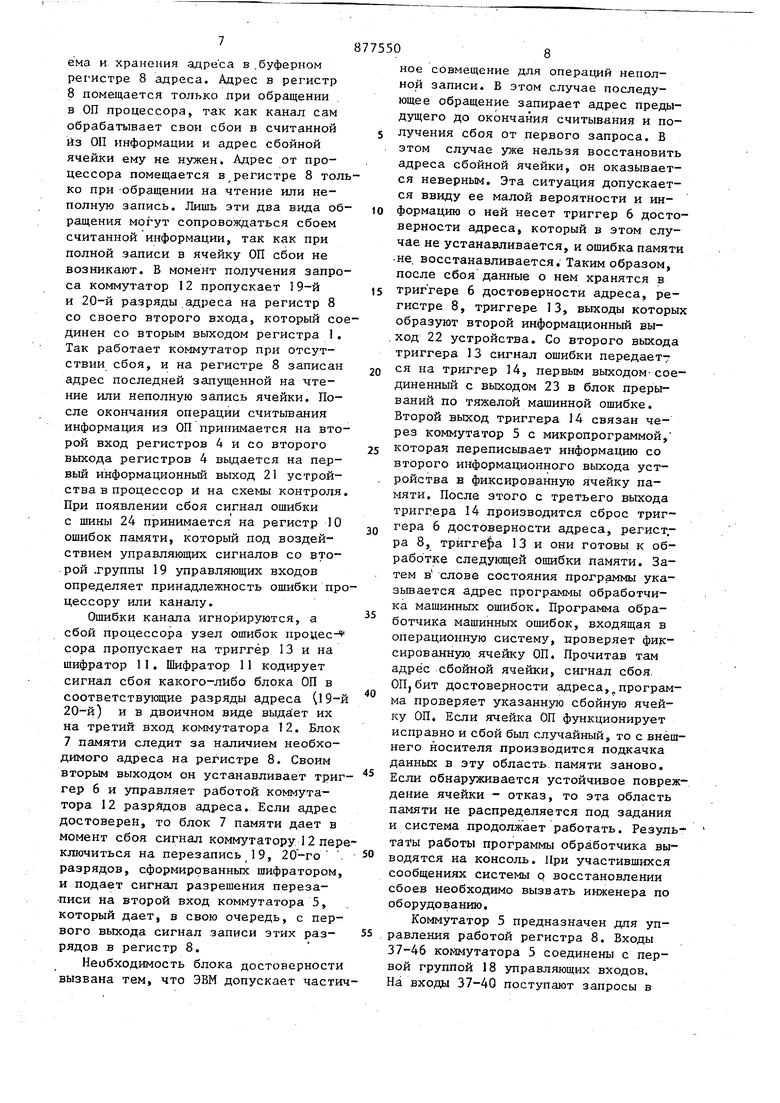

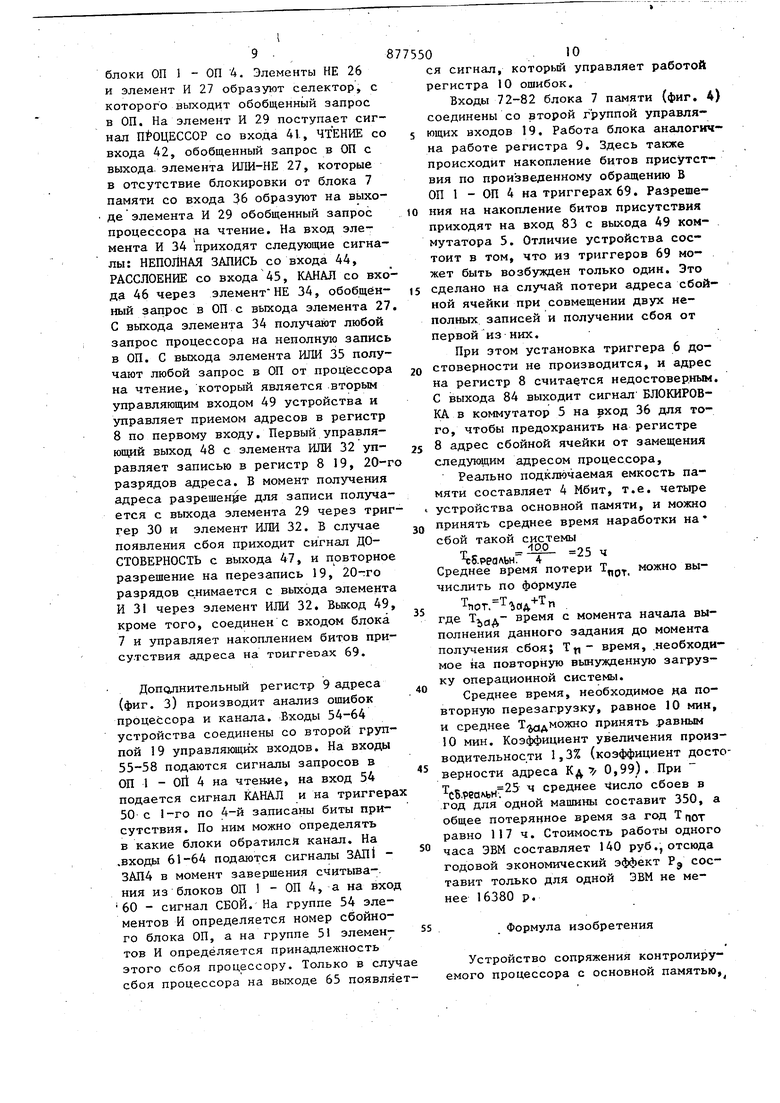

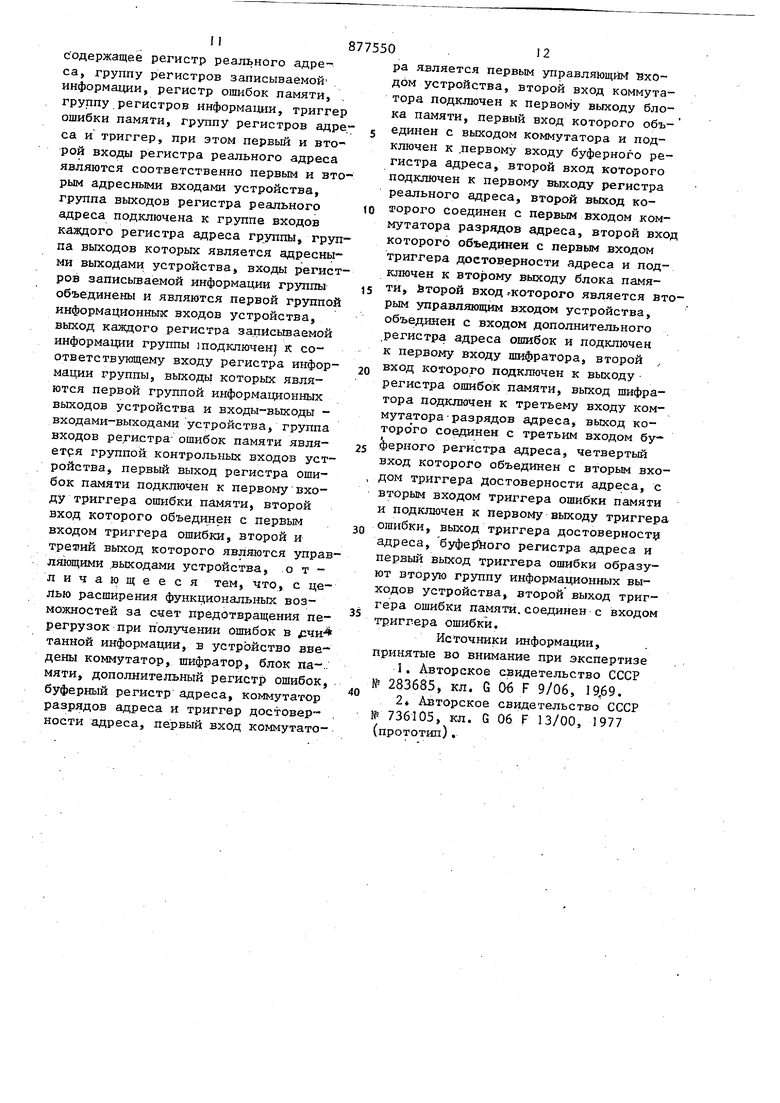

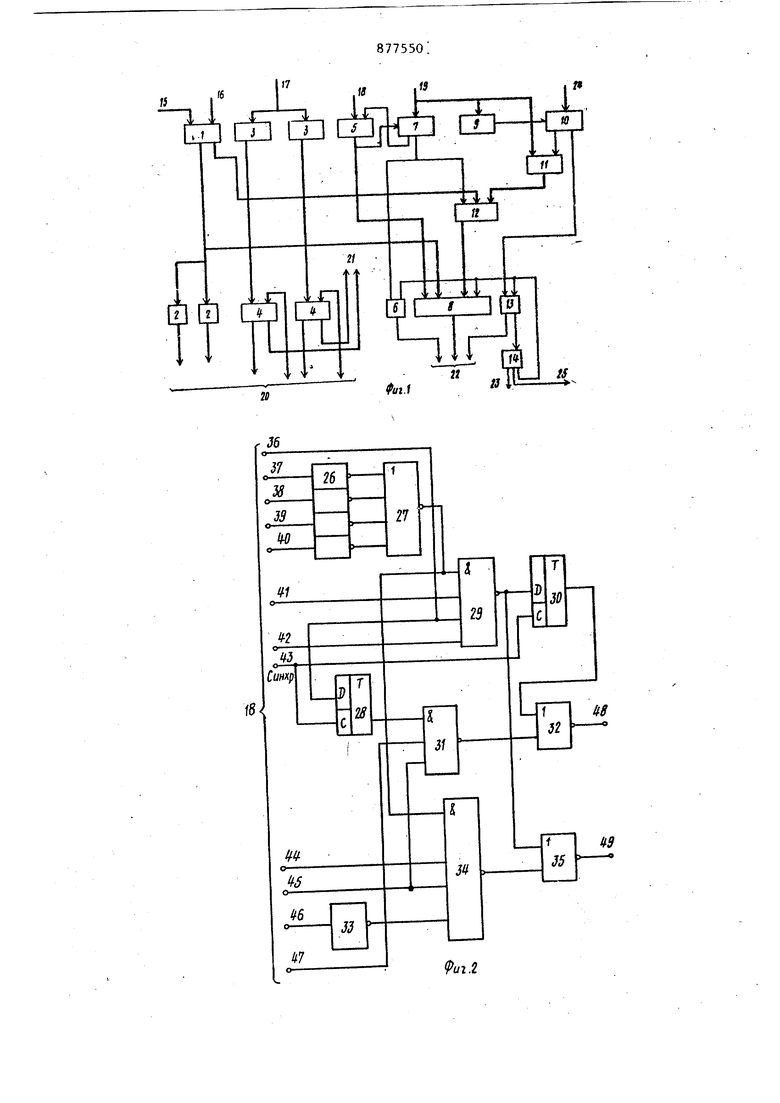

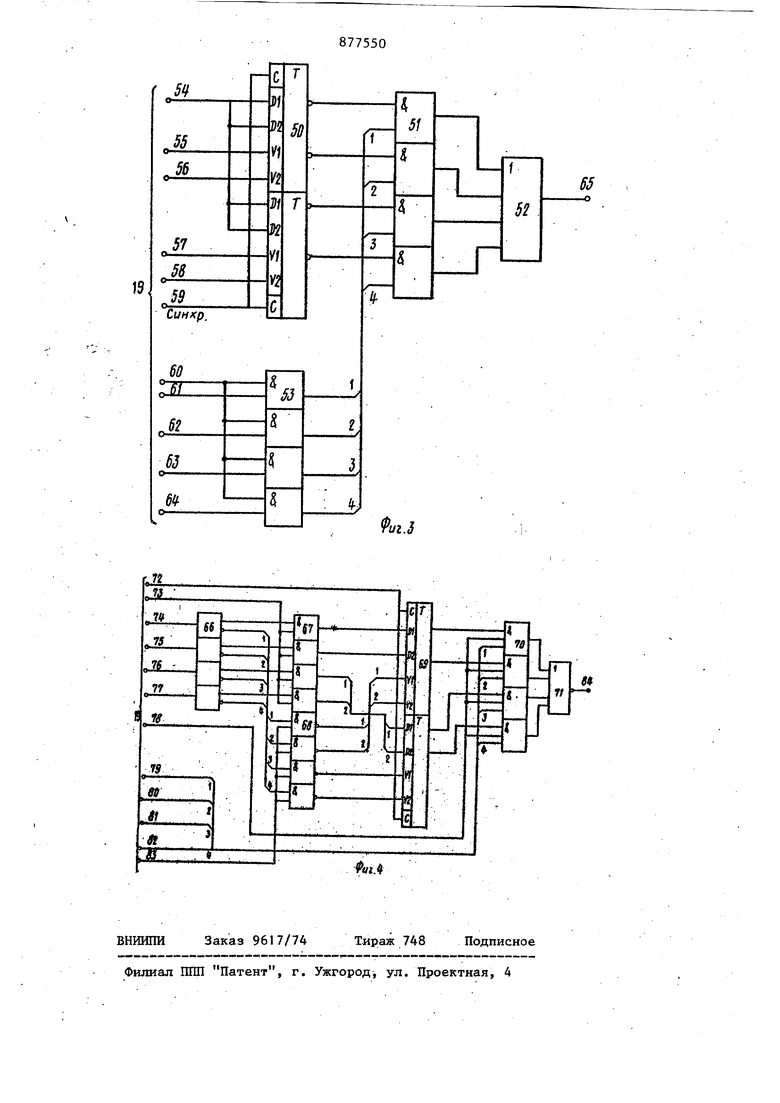

Изобретение относится к вычислитель ной технике. . Известно устройство, входящее в состав процессора, предназначенное для со111 яжения основного процессора (ОП) с процессором в режиме двукратного расслоения и определения ошибок в считанной из ОП информации, содержащее регистр информации памяти, регистр адреса памяти, коммутатор шин ОП, схему контроля информации,, считанной из ОП иЗ Недостаток устройства заключается в том, что при обнаружении ошибки в считанной из ОП информации,. работа процессора прерывается и для во зобновления требуется перезагрузка. Время от момента загрузки до получения сигнала ошибки непроизводительно теряется. Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому является устройство со пряжения основной памяти с процессором, содержащее по числу групп блоков памяти регистры адреса, информационные регистры и выходные регистры, узел коррекции, узлы выборки, групп блоков памяти, два элемента ИЛИ и узлы синхронизации по числу групп блоков памяти, формирователь корректирующего кода и группу элементов И-ИЛИ, соответственно соединенных первыми входами с группой выходов узла кор:рекции и первой группой информационных выходов устройства, первая группа информационных входов и группа адресных входов которого подключены соответственно ко входам информационных регистров и входам регистров адреса, выходы которых являются адресньми выходами устройства, вторая группа информационных выходов устройства соединена с первыми информационными входами соответствующих выходных регистров, выходы rpynitti элементов И-Ш1И соединены с соответствующими входами фор- мирователя корректирующего кода, выходы информационных регистров подключены к соответствующим входам пер вого элемента ИЛИ, выход которого со динен со вторым входом группы элемента И-ИЛИ, второй и третий информа ционные входы выходных регистров, первые выходы которых соединены с соответствующими выходами второй гру пы информационных выходов устройства подключены соответственно к выходам элементов И-ИЛИ и выходам формирования корректирующего кода, вторые вых ды выходных регистров соединены с со ответствующими входами второго элемента ИЛИ, подключенного выходом ко входу узла коррекции, входы каждого узла синхронизации являются соответг ствующими управляющими входами устройства, первый, второй и третий выходы каждого узла синхронизации подключены к соответствующим управляющим входам одноименного выходного регистра, третий и четвертый выходы каждого узла синхронизации соединены соответственно управляющим входам узла выборки блока памяти, входы которого подключены к выходам соответствующих регистров адреса, а выход я ляется управляющим выходом устройства. Данное устройство предназначено для сопряжения процессора, работающего в режиме четырехкратного рассл ения с ОП, который разделен на 4 гру пы блоков, имеющих общие адресные и информационные шины. Адресные и информ ционные регистры этих блоков нахддятт ся в устройстве сопряжения. Данное устройство вьтолнено в виде четырех симметр1гчных схем 21. Недостаток известного устройства заключается в том, что при возникнов нии ошибки памяти для продолжения ра боты необходима перезагрузка. Для достижения поставленной цели в устройство сопряжения контролируемого процессора с основной памятью, содержащее регистр реального адреса, группу регистров записываемой информа ции, регистр ошибок, памяти, группу регистров информации, триггер ошибки памяти, группу регистров адреса и триггер, при этом первый и второй входы регистра реального адреса являются соответственно первым и вторым адресными входами устройства, группа выходов регистра реального адреса Подключена к группе входов каждого регистра адреса jpynm.i, группа выходов которых является адресными выходами устройства, входы регистров записываемой информагши группы объединены и являются первой группой информационных входов устройства, выход каждого / регистра записываемой информации группы подключен к соответствующему входу регистра информации группы, выходы котррых являются первой группой информационных выходов устройства и входы-выходы - входами-выходами, устройства, группа входов регистра ошибок памяти является группой контрольных входив устройства, первый выход регистра ошибок памяти подключен к первому входу триггера ошибки памяти, второй вход которого объединен с первым входом триггера , второй и третий выход которого является управляющими выходами устройства, введены коммутатор, шифратор, блок памяти, дополнительный регистр ошибок, буферный регистр адреса, коммутатор разрядовIадреса и триггер достоверности адреса, первьвЧ: вход коммутатора является первым управляющим входом устройства, второй вход коммутатора подключен к первому выходу.блока памяти, первый вход которого объединен с выходом коммутатора и подключен к первому входу буферного регистра адреса,- второй вход которого подключен к первому выходу регистра реального адреса, второй выход которого соединен с первым входом коммутатора разряда адреса, второй вход которого объединен с первым входом триггера достоверности адреса и подключен ко второму выходу блока памяти, второй вход которого является вторым управляющим входом устройства и объединен со входом дополнительного ре истра адреса ошибок, и подклтючен к первому входу шифратора, второй вход которого подключен к выходу регистра ошибок памяти, выход . шифратора подключен к тpeтьe fy входу коммутатора разрядов адреса, выход которого соединен с третьим входом буферного регистра адреса, четвертый вход которого объединен со вторым входом триггера достоверности адреса, со вторым входом триггера ошибки памяти и подключен к первому выходу триггера ошибки, вьпсод триггера достоверности адреса, буферного регистра адреса и первый выход триггера ошибки образуют вторую группу информационных выходов устройства, второй выход триггера ошибки памяти соединен со входом триггера ошибки. Описание составлено для устройства сопряжения, работающего с четырьмя блоками памяти в режиме четырехкратного расслоения. На фиг. 1 Показана структурная сх ма устройства; на фиг. 2 - схема бло ка управления; на фиг. 3 - схема бло ка достоверности адреса памяти; на фиг 4 - схема узла ошибок процессор Устройство содержит регистр 1 реального адреса, группу,регистров 2 адреса, группу регистров 3 записываемой информации, группу 4 регистров информации, коммутатор 5, триггер 6 достоверности адреса блок 7 памяти, буферный регистр 8 адреса, дополнительный регистр 9 адреса, регистр 10 ошибок памяти, шифратор 11, коммутатор 12, триггер 13, триггер 14 ошибки, первый -адресный вход 15 устройства, второй адресный вход 16 устрой ства, информационный вход 17 устройства, первую группу 18 управляющих входов, вторую группу 19 управляющих входов, адресные и информационные ши ны 20 памяти, первый информационный выход 21 устройства, второй информационный выход 22 устройства, выход 23 прерываний, шину 24, управляющий выход 25 устройства, элемент НЕ 26, элемент ИЛИ-НЕ 27, триггер 28, элемент И-ИЕ 29, триггер 30, элемент И-НЕ 31, элемент ИЛИ-НЕ 32, элемент НЕ 33, элемент И-НЕ 34, элемент ИЛИНЕ 35, группу 36-47 управляющих входов, выходы 48, 49, тригер 50, группу .элементов 51, элемент НЕ 52 и гру пу 53 Элементов,И, группу 54-64 упра ляющих выходов, выход 65, элементы НЕ 66,. элементы И 67, элементы ИНЕ 68, триггеры. 69, элементы И 70, элементы НЕ 71, группу 72-83 управля ющих входов, выход 84. Предлагаемое устройство предназначено для сопряжения процессора, работающего в режиме п-кратного расслоения, с ОП разделенным на п блоков, каждый из которьк имеет свою адресную и информационную шину, и обеспечения работоспособности процессора при возникновении ошибок в считанной из ОП информации. Адресные и информацио.нные регистры блоков памяти находятся в .устройстве, сопряжения. Устройство работает следующим образом.В режиме п-кратного расслоения работа блоков памяти совмещается во времени. Адреса различных запросов в ОП последовательно замещают друг друга на входе 16. К моменту появления ошибки в считанной информации адрес сбойной ячейки, обычно, уже потерян. Одна из главных целей устройства - сохранение адреса сбойной ячейки и запись его в фиксированную ячейку ОП для обеспечения нормальной работы процессора после возникновения сбоя. Адрес сбойной ячейки ОП хранится в коммутаторе 5. Работа устройства основана на том, что в режиме расслоения последовательно запускаемые в ОП на чтение адреса обычно имеют большую группу тождественных разрядов, Для сохранения адреса ячейки ОП его сбоем можно сохранить лишь общую часть адреса и восстановить изменяемую часть в момент получения сбоя вместо запоминания полных четырех адресов для блоков ОП1+ОП4. Изменяемой частью 24-разрядного адреса являются 19, 20-й разряды, которые адресуют номер блока ОП, Разряды 21-23-й, адресуняцие номер байта в двойном слове, игнорируются и заполняются нулями. Восстановить 19, 20-й разряды можно в момент сбоя, дпределяя двоичный номер сбившегося блока памяти. Адреса запросов в ОП поступают на регистр 1 с первого адресного входа 15 от канала и со второго адресного входа 16 от процессора. Через группу регистров 2 адреса памяти адрес поступает с первого выхода регистра 1 в шины 20 памяти. Информация на запись в ОП поступает с информационного входа 17 устройства на группу 3регистров и, далее, через группу 4в шины 20 памяти. Считанная из ОП информация через группу 4 регистров поступает на первый информационный выход 21 устройства и далее в процессор, на схему контроля информации. После того, как адрес запроса принят на регистр 1, он с выхода этого регистра поступает на вход регистра 8, причем основная часть адреса приходит с первого выхода регистра 1 на второй вход регистра 8, а изменяемая часть - со второго выхода регистра 1, через коммутатор 12 на третий вход регистра 8. Одновременно с адресом коммутатор 5 принимает группу управляющих признаков с первой группы 18 управляющих входов. Коммутатор 5 определяет условия ёма и хранения адреса в .буферном регистре 8 адреса. Адрес в регистр 8 помещается только при обращении . в ОП процессора, так как канал сам обрабатывает свои сбои в считанной из Oil информации и адрес сбойной ячейки ему не нужен. Адрес от процессора помещается в регистре 8 тол ко при обращении на чтение или неполную запись. Лишь эти два вида об ращения могут сопровождаться сбоем считанной информации, так как при полной записи в ячейку ОП сбои не возникают. В момент получения запро са коммутатор 12 пропускает 19-й и 20-й разряды адреса на регистр 8 со своего второго входа, который со динен со вторым выходом регистра 1. Так работает коммутатор при отсутствии сбоя, и на регистре 8 записан адрес последней запущенной на чтение или неполную запись ячейки. После окончания операции считывания информация из ОП принимается на вто рой вход регистров 4 и со второго выхода регистров 4 выдается на первый информационный выход 21 устройства в процессор и на схемы контроля При появлении сбоя сигнал ошибки с шины 24 принимается на регистр 10 ошибок памяти, который под воздействием управляющих сигналов со второй .группы 19 управляющих входов определяет принадлежность ошибки пр цессору или каналу. Ошибки канала игнорируются, а сбой процессора узел ошибок процес- сора пропускает на триггер 13 и на шифратор 11. Шифратор I1 кодирует сигнал сбоя какого-либо блока ОП в соответствующие разряды адреса (1920-й) и в двоичном виде выда;ет их на третий вход коммутатора 12. Блок 7 памяти следит за наличием необходимого адреса на регистре 8. Своим вторым выходом он устанавливает три гер 6 и управляет работой коммутатора 12 разрйдов адреса. Если адрес достоверен, то блок 7 памяти дает в момент сбоя сигнал коммутатору 1 2 пер ключиться на перезапись 19, 20-го разрядов, сформированных шифратором и подает сигнал разрешения перезаписи на второй вход коммутатора 5, который дает, в свою очередь, с пер вого выхода сигнал записи этих разрядов в регистр 8. Необходимость блока достоверност вызвана тем, что ЭВМ допускает част ное совмещение для операций неполной записи. В этом случае последующее обращение запирает адрес предыдущего до окончания считывания и получения сбоя от первого запроса. В этом случае уже нельзя восстановить адреса сбойной ячейки, он оказывается наверньпу. Эта ситуация допускается ввиду ее малой вероятности и информацию о ней несет триггер 6 достоверности адреса, который в этом случае не устанавливается, и ошибка памяти не. восстанавливается. Таким образом, после сбоя данные о нем хранятся в триггере 6 достоверности адреса, регистре 8, триггере 13, выходы которых образуют второй информационный выход 22 устройства. Со второго выхода триггера 13 сигнал ошибки передает7 ся на триггер 14, первым выходом-соединенный с выходом 23 в блок прерываний по тяжелой машинной ошибке. Второй выход триггера 14 связан через коммутатор 5 с микропрограммой, которая переписьшает информацию со второго информационного выхода устройства в фиксированную ячейку памяти. После этого с третьего выхода триггера 14 производится сброс триггера 6 достоверности адреса, регистра 8, триггера 13 и они готовы к обработке следующей ошибки памяти. Затем в слове состояния программы указьгоается адрес программы обработчика машинных ошибок. Программа обработчика машинных ошибок, входящая в операционную систему, проверяет фиксированную, ячейку ОП. Прочитав там адрес сбойной ячейки, сигнал сбоя. достоверности адреса,программа проверяет указанную сбойную ячейку ОП. Если ячейка ОП функционирует исправно и сбой бьш случайный, то с внешнего носителя производится подкачка данных в эту область памяти заново. Если обнаруживается устойчивое повреждение ячейки - отказ, то эта область памяти не распределяется под задания и система продолжает работать. Результаты работы программы обработчика выводятся на консоль. При участившихся сообщениях системы Q восстановлении сбоев необходимо вызвать инженера по оборудованию. Коммутатор 5 предназначен для управления работой регистра 8. Входы 37-46 коммутатора 5 соединены с первой группой 18 управляющих входов. На входы 37-40 поступают запросы в блоки on 1 - on -4. Элементы HE 26 и элемент И 27 образуют селектор, с которого выходит обобщенный запрос в СП. На элемент И 29 поступает сигнал ПРОЦЕССОР со входа 41., ЧТЕНИЕ со входа 42, обобщенный запрос в ОП с выхода, элемента ИЛИ-НЕ 27, которые в отсутствие блокировки от блока 7 памяти со входа 36 образуют на выходе элемента И 29 обобщенный запрос процессора на чтение. На вход элемента И 34 приходят следующие сигналы: НЕПОЛНАЯ ЗАПИСЬ со входа 44, РАССЛОЕНИЕ со входаЧЗ, КАНАЛ со вхо да 46 через элемент НЕ 34, обобщённый запрос в ОП с выхода элемента 27 С выхода элемента 34 получают любой запрос процессора на неполную запись в ОП. С выхода элемента ИЛИ 35 получают любой запрос в ОП от процессора на чтение, который является вторым управляющим входом 49 устройства и управляет приемом адресов в регистр 8 по первому входу. Первый управляющий выход 48 с элемента ИЛИ 32 управляет записью в регистр 8 19, 20-г разрядов адреса. В момент получения адреса разрешен зе для записи получается с выхода элемента 29 через триг гер 30 и элемент ИЛИ 32. В случае появления сбоя приходит сигнал ДОСТОВЕРНОСТЬ с выхода 47, и повторное разрешение на перезапись 19, 20-:го разрядов снимается с выхода элемента И 31 через элемент ИЛИ 32. Выкод 49, кроме того, соединен с входом блока 7 и управляет накоплением битов прису.тствия адреса на тоиггевах 69. Дополнительный регистр 9 адреса (фиг. З) производит анализ ошибок процессора и канала. Входы 54-64 устройства соединены со второй группой 19 управляющих входов. На входы 55-58 подаются сигналы запросов в ОП 1 - Olt 4 на чтение, на вход 54 подается сигнал КАНАЛ и на триггера 50 с 1-го по 4-й записаны биты присутствия. По ним можно определять в какие блоки обратился канал. На .входы 61-64 подаются сигналы ЗШ ЗАП4 в момент завершения считыва-. ния из блоков ОП 1 - ОП 4, а на вход 60 - сигнал СБОЙ. На группе 54 элементов И определяется номер сбойного блока ОП, а на группе 51 элементов И определяется принадлежность этого сбоя процессору. Только в случ сбоя процессора на выходе 65 появляе 0. 10 ся сигнал, который управляет работой регистра 10 ошибок. Входы 72-82 блока 7 памяти (фиг. 4) соединены со второй группой управля- ющих входов 19. Работа блока аналогична работе регистра 9. Здесь также происходит накопление битов присутствия по произведенному обращению Б ОП 1 - ОП 4 на триггерах 69. Раэрешения на накопление битов присутствия приходят на вход 83 с выхода 49 ком- . мутатора 5. Отличие устройства сос тоит в том, что из триггеров 69 может быть возбужден только один. Это сделано на случай потери адреса сбойной ячейки при совмещении двух неполных записей и получении сбоя от первой из них. При этом установка триггера 6 достовериости не производится, и адрес на регистр 8 считается недостоверным. С выхода 84 выходит сигнал БЛОКИРОВКА в коммутатор 5 на вход 36 для того, чтобы предохранить на регистре 8 адрес сбойной ячейки от замещения следующим адресом процессора. Реально подключаемая емкость памяти составляет 4 Мбит, т.е. четьфе устройства основной памяти, и можно принять среднее время наработки на сбой такой системы т - -IPO -91; U 5.реальн7 Л 2 Среднее время потери Т, можно вычислить по формуле ТТ,,,„Д+ТП где Тхдд- время с момента начала выполнения данного задания до момента получения сбоя; время, .необходимое на повторную вьшужденную загрузку операционной системы. Среднее время, необходимое на повторную перезагрузку, равное 10 мин, и среднее т/ ддможно принять .равным 10 мин. Коэффициент увеличения производительности 1,3% (коэффициент достоверности адреса Кд 0,99). При Tj. ч среднее Число сбоев в год для одной машины составит 350, а общее потерянное время за год Т гют равно 117 ч. Стоимость работы одного часа ЭВМ составляет 140 руб., отсюда годовой экономический эффект Р составит только для одной ЭВМ не менее 16380 р. Формула изобретения Устройство сопряжения контролируемого процессора с основной памятью.

содержащее регистр реального адреса, группу регистров записываемой информахщи, регистр ошибок памяти, , группу регистров информации, триггер ошибки памяти, группу регистров адре,са и триггер, при этом первый и второй входы регистра реального адреса являются соответственно первым и вторым адресными входами устройства, группа выходов регистра реального адреса подключена к группе входов каждого регистра адреса группы, группа выходов которых является адресными выходами устройства, входы регистров записываемой информации группы объединены и являк1тся первой группой информационных входов устройства, выход каждого регистра записываемой информации группы jподключен) к соответствующему ВХОДУ регистра информации группы, выходы которых являются первой группой информационных выходов устройства и входы-выходы входами-выходами устройства, группа входов регистра- ошибок памяти явля- етря группой контрольных входов устройства, первый выход регистра ошибок памяти подключен к первому входу триггера ошибки памяти, второй вход которого объединен с первым входом триггера ошибки, второй и третий выход которого являются управляняцими выходами устройства, .отличающееся тем, что, с целью расширения функциональных возможностей за предотвращения перегрузок при получении ошибок в :чи танной информации, в устройство введены коммутатор, шифратор, блок па-.. мяти, дополнительный регистр ошибок, буферный регистр адреса, коммутатор разрядов адреса и триггер достовер ности адреса, первый вход коммутатора является первым управляющим входом устройства, второй вход коммутатора подключен к первому выходу блока памяти, первый вход которого объ- единен с выходом коммутатора и подключен к .первому входу буферного регистра адреса, второй вход которого подключен к первому выходу регистра реального адреса, второй выход которого соединен с первым входом коммутатора разрядов адреса, второй вхо которого объединен с первым входом триггера достоверности адреса и подключен к второму выходу блока памяти, Итерой вход fKOToporo является втрым управляющим входом устройства, объединен с входом дополнительного регистра адреса ошибок и подключен к первому входу шифратора, второй , вход которого подключен к вьсходу регистра ошибок памяти, выход шифратора подключен к третьему входу коммутатора разрядов адреса, выход которого соединен с третьим входом буi epHoro регистра адреса, четвертый вход которого объединен с вторым входом триггера достоверности адреса, с вторым входом триггера ошибки памяти и подключен к первому выходу триггер ошибки, выход триггера достоверности адреса, буфе1Яного регистра адреса и первый выход триггера ошибки образуют вторую группу информационных выходов устройства, второй выход триггера ошибки памяти.соединен с входом триггера ошибки.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 283685, кл. G 06 F 9/06, 19,69.

2 Авторское свидетельство СССР №736105, кл. G 06 13/00, 1977 (прототип).

ft

« «иь «.f -

Авторы

Даты

1981-10-30—Публикация

1980-03-04—Подача