(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Устройство для контроля логических схем | 1981 |

|

SU1013956A2 |

| Логический анализатор | 1980 |

|

SU890396A1 |

| Устройство для анализа информационной последовательности | 1978 |

|

SU746529A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1982 |

|

SU1084864A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

Изобретение относится к вычислительной технике и может быть использовано для поиска неисправностей и ошибок в аппаратных и программных средствах электронного цифрового оборудования. Известно устройство для диагностики неисправности в логических схемах, содержащее тактовый генератор, счетчик импульсов, блок вычисления синдрома, дешифратор, элементы ИЛИ, счетчики неисправностей, коммутатор, элементы И, дополнительный генератор импуль сов 1. Недостатком известного устройства является невозможность анализа логаческих временны диаграмм. Наиболее близким Тс изобретению по техни ческой сущности и достигаемому результату является устройство для обнаружения ошибок, содержащее входной регистр , запоминающее устройство, блок управления устройством отображения, устройство отображения, Щ1фровой компаратор, блок цифровой задержки и блок управления запоминающим устройством, при этом выходы входного регистра подключе

cifKi-iKi:isf.,.

WiaAAiB«il-iiiiAwA ;4ut ii ii :

V -loiilai -iii K Xt fetti ы к исследуемому объекту, синхронизирующие входы регистра подключень к входной тине синхронизации его анализатора, синхрошзирующие входы блока пифровой задержки подключены к входной шине синхронизации анализатора, входы блока )гщ авления запоминающего устройства соединены с входами анализатора 2. Недостатком известного устройства является то, что оно не обеспечивает возможность анализа временных диаграмм синхронных и аоюхронных схем. Цель изобретения - повьщ1ение надежности устройства. Для достижения поставленной цели в устройство для контроля логических схем, содержащее регистр, цифровой компаратор, блок задержки, блоки зшравления, блок памяти, блок индикации, причем первый и второй входы регистра являются входами устройства, выходы регистра подключены к соответствующим входам блока памяти и к соответствующим входам цифрового компаратора, выход:. которого соединен . с первым входом блока задержки, второй вход которого соединен с третьим входом регистра и с управляющим входом первого блока управления, второй вход которого подключен к выходу блока задержки, выход первого блока управления соединен со входом . блока памяти и с управляющим входом второго блока управления, выход которого соединен с блоком индикации, введены блок синхронизации, генератор импульсов, преобразователь кодов, блок выработки временной диаграммы блок выработки знаковой информации, причем первый вход блока синхронизации является синхронным входом устройства, выход блока синхронизации соединен со входом регистра, второй вход блока синхронизации пбдключен к выходу генератора импульсов, выход блока памяти соединен со входом преобразователя кодов, первый выход которого подключен ко входу блока выработки знаковой информации, второй вход преобразователя кодов соединен с блоком выработки временной диаграммы,

ВЫХОД которого подключен ко второму входу блока индикации, третий вход которого соеди. нен с выходом блока выработки знаковой информации.

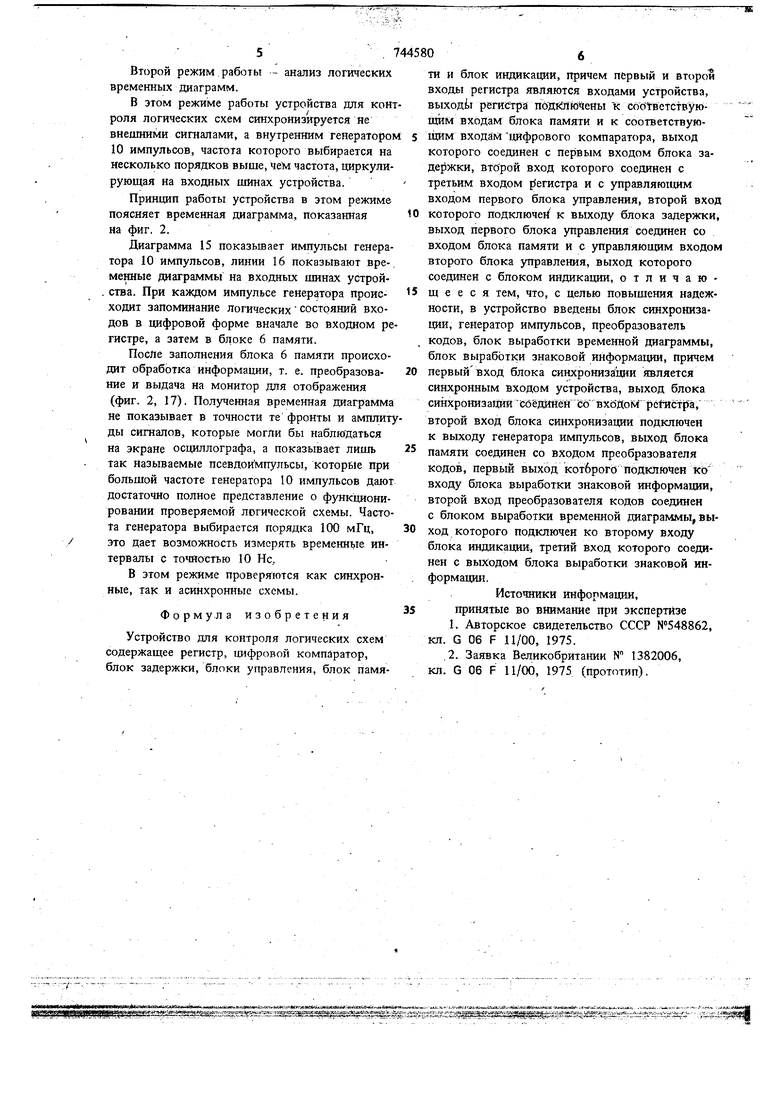

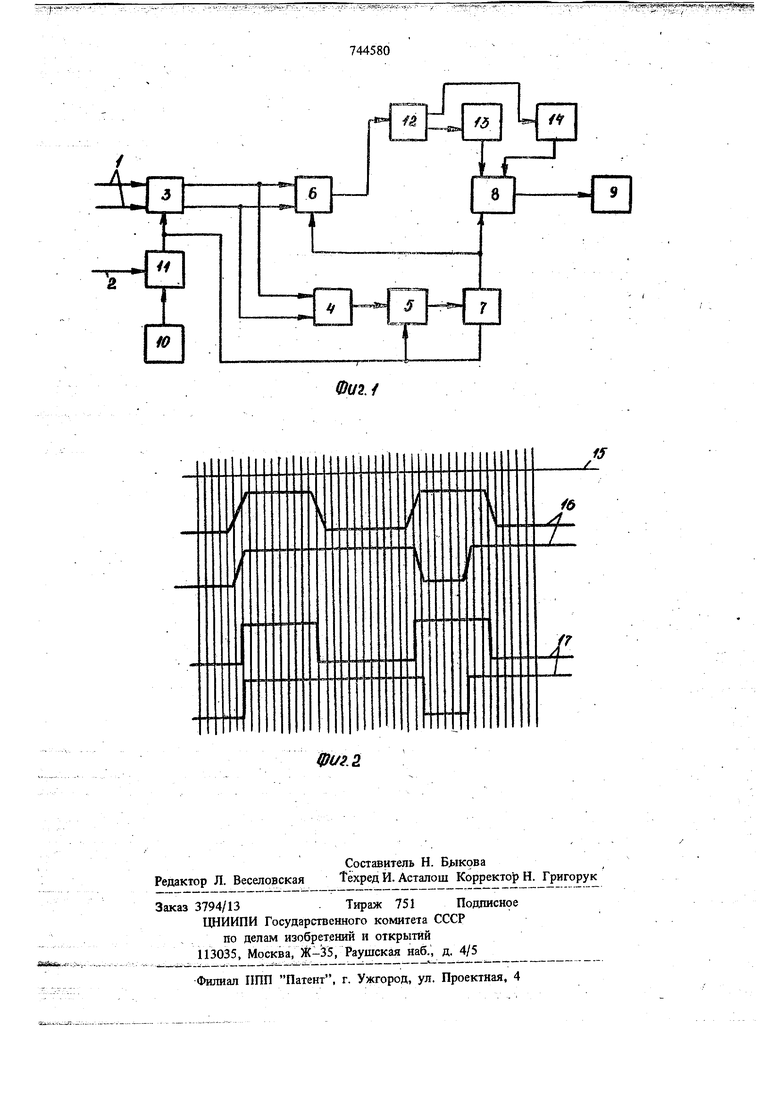

На фиг. 1 приведена блок-схема устройст ва; на фиг. 2 - временная диаграмма, объясняющая принцип работы устройства при анализе логической временной диаграммы.

Устройство для контроля логических схем содержит входы 1 устройства, вход 2 внешней синхронизации, регистр 3, цифровой компаратор 4, блок 5 задержки, блок 6 памяти, первый блок 7 управления, второй блок 8 управления, блок 9 индикации, генератор 10 импульсов, блок 11 синхронизации, блок 12 преобразования информации, блок 13 выработки временной диаграммы, блок 14 выработки знаковой информации.

Устройство для контроля логических схем работает в двух режимах следующим образом. Первый режим работы - анализ логических состояний.

В этом режиме вход 2 синхронизации устройства подключается к синхронному синхросигналу исследуемого объекта, а входы данных - к проверяемым точкам объекта. При каясДом поступлении синхроимпульса во входном регистре 3 происходит запоминание логических состояний входов объекта, а затем та же информация переписывается в блок 6 памяти. При откладке программ часто возникает необходийОстЬ 1 ОйтроЛироВ1ать массив данньи , в районе какого-либо ключевого слова. В этом случае опёратором с помощью блока управления заносится требуемое слово в цифровой компаратор 4 в двоичном формате. Когда входное слово. из массива входных данных сравик Жетей с ключёвьтм crtotoM, з правлёнйё пёрё дается к блокам 7, 8 управления и блоку 9 ин445804

дикации таким, образом, что если требуется контролировать данные, предшествующие ключевому слову, то тогда происходит прекращение процесса непрерывной записи в блок 6 паJ мяти и устройство переходит в режим отображения информации, а если требуется массив данных, последующих ключевому слову, то в этом случае сигнал из цифрового компаратора 4 дает разрешение з аписи в блок 6 памяти 0 до ее заполнения, после чего информация отображается. При желании оператор может задержать сбор данных на определенное число перио, дов синхросигнала. В этом случае оператор заносит в блок 5 задержки требуемую величину 5 задержки. После прихода сигнала сравнения из цифрового компаратора 4 в блок 5 задержки запускается счетчик синхроимпульсов, и как только счетчик сосчитает требуемое оператором число импульсов, управление передается

0 к блокам 7, 8 управления вышеуказанным способом.

После заполнения блока 6 памяти данными начинается процесс обработки информации для отображения.

5 Для индикации логических временных диаграмм, состоящих из 16 линий, применены участки под определенными номерами, а в каждом участке выделяются фиксированные развертки для проведения линий, обозначаю0 щих логические уровни 1 и О, например, первая развертка предназначается для проведения линии логической 1, а двенадцатая Для логического О. Для отображения цифровой информации принимается участок под но5 мером 3.

Информация, считанная из блока 6 памяти, передается в блок 12 преобразования кодов, где происходит ее преобразование в форме, удобной для работы блоков 13 и 14. Например

0 для блока 13 блок 12 преобразования кодов осуществляет коммутацию разрядов от 16-разрядных слов разряд за разрядом. По значениям логических состояний данного разряда в блоке, 13 происходит выработка управляющего сигна5 ла засвечиванием пуча в соответствующих развертках. Для блока 14 блок 12 осуществляет преобразование информации в двоичной, восьмеричной или шестнадцатиричной формах. В блоке 14 Помещается знаковый генератор, ко,, торый в соответствии с полученной информацией осуществляет выработку управляющего сигнала засвечением луча в требуемых развертках и точках.

Цифровая информация соответствует только

одной ячейке памяти, тогда как временная диаграмма содержит информацию как с этой ячейки палЛяти, так и несколько битов информащй по каждому каналу в сторону возрастания номера ячеек блока памяти. 5. 7 Второй режим работы - анализ логических временных диаграмм. В этом режиме работы устройства для конт роля логических схем синхронизируется не внешними сигналами, а внутренним генератором 10 импульсов, частота которого выбирается на несколько порядков выше, чем частота, циркулирующая на входных шинах устройства. Принцип работы устройства в этом режиме поясняет временная диаграмма, показанная на фиг. 2. Диаграмма 15 показьшает импульсы генератора 10 импульсов, линии 16 показывают вре-. меяные диаграммы на входных шинах устрой. ства. При каждом импульсе генератора происходит запоминание логических состояний входов в цифровой форме вначале во входном ре гистре, а затем в блоке 6 памяти. После заполнения блока 6 памяти происходит обработка информации, т. е. преобразова ние и выдача на монитор для отображения (фиг. 2, 17). Полученная временная диаграмма не показывает в точности те фронты и амплиту ды сигналов, которые могли бы наблюдаться на экране осциллографа, а показывает лишь так называемые псевдоимпульсь, kotoptie при большой частоте генератора 10 импульсов дают достаточно полное представление о функционировании проверяемой логической схемы. Частота генератора выбирается порядка 100 мГц, это дает возможность измерять временные интервалы с точностью 10 Не, В этом режиме проверяются как синхронные, так и асинхронные схемы. Формула изобретения Устройство для контроля логических схем содержащее регистр, цифровой компаратор, блок задержки, блоки управления, блок памяtiУ-J;У- -J,Лf.af. : ri1 - - :tfFr- --r f - f -J f -f---ifffi frf:i itfiasnA-aJ.M iiooAt

««jwfge SSS ffl SsSasS-SrK J JK-SScri 0 ти и блок индикации, причем первый и второй входы регистра являются входами устройства, выходит регистра пбД сЛк5чеНы к сш ветствующиМ входам блока памяти и к соответствую1цим входам цифрового компаратора, выход которого соединен с первым входом блока задержки, второй вход которого соединен с третьим входом {Регистра и с управляющим входом первого блока управления, второй вход которого подключен к выходу блока задержки, выход первого блока управления соединен со входом блока памяти и с управляющим входом второго блока управления, выход которого соединен с блоком индикации, отличающееся тем, что, с целью повышения надежности, в устройство введены блок синхронизации, генератор импульсов, преобразователь кодов, блок выработки временной диаграммы, блок выработки знаковой информации, причем первыйвход блока синхронизации является синхронным входом устройства, выход блока синхрониза1даиСбёДиНён(Сб ВХОДОМ pcfHctpa, второй вход блока синхронизации подключен к выходу генератора импульсов, выход блока памяти соединен со входом преобразователя кодов, первый выход котброго подключен ко входу блока выработки знаковой информации, второй вход преобразователя кодов соединен с блоком выработки временной диаграммы, выход которого подключен ко второму входу блока индикации, третий вход которого соединен с выходом блока выработки знаковой информации. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №548862, кл. G 06 F 11/00, 1975. .2. Заявка Великобритании N 1382006, кл. G 06 F 11/00, 1975 (прототип).

Авторы

Даты

1980-06-30—Публикация

1978-03-27—Подача