щих регистров соединен с третьим информационным входом блока памяти и вторыми информационными входами коммутатора часов и коммутатора таймера процессора-, управляющий вход блока памяти является управляющим входом 116330 9 устройства и соединен с управляющими входами блока сдвигающих регистров , коммутатора часов , коммутатора таймера процессора , коммутатора блока сдвигающих регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе средств отсчета времени ЭВМ.

Известно устройство таймеров в ЭВМ ЕС 1035, содержащее регистры часов, компаратора и таймера процессора, сумматоры часов и таймера процессора, формирователи запроса на прерывание от компаратора и таймера П4 оцессора, в котором пересчет информации .таймеров осуществляется параллельным способом на сумматоре, разрядность которого совпадает с разрядностью информации Q . Такое устройство имеет большое быстродействие, однако требует больших затрат оборудования.

Наиболее близким к изобретению является устройство таймеров в ЭВМ ЕС 1060, содержащее блок памяти, включающий регистры часов, компаратора и таймера процессора, выходные селекторы часов, компаратора и таймера процессора, причем выход регистра часов блока памяти соединен с входом выходного селектора часов и первым входом выходного селектора устройства таймеров; выход выходного селектора часов соединен с входом сумматора часов, выход которого соединен с первьм формирователя запросов на прерывание от компаратора и с первым входом входното селектора часов, выход которого

соединен с г :одом регистра часов блока памяти, выход регистра таймера

процессора блока памяти соединен с

входом выходного селектора таймера процессора, втором входом выходного

селектора устройства таймеров и входом триггера запроса на прерывание от таймера процессора, выход которого подключён к выходу устройства, выход выходного селектора таймера процессора является входом устройства, выход выходного селектора таймера процессора соединен с входом сумматора таймера процессора, выход которого соединен с первым входом входного селектора таймера процессора; выход входного селектора таймера процессо.ра соединен с входом регистра таймера процессора блока памяти, выход регистра компаратора блока пат .мяти соединен с входом вькоднего селектора компаратора и третьим входом выходного селектора устройства таймеров, выход которого являетг ся выходом устройства; выход выходного селектора компаратора соединен с входом выходного регистра компаратора, выход которого соединен с вторым входом формирователя запросов на прерывание от компаратора; выход формирователя запросов на прерывание от компаратора является выходом устройства, вторые входы входных селекторов часов и таймера процессора соединены с входом регистра компаратора блока памяти и являются входом устройства таймеров. В известном устройстве реализован последовательнопараллельный способ обработки информации таймера - пересчет 52-х разрядов информации часов и таймера процессора ведется частями по 16 разрядов. Работа устройства в состав.е ЭВМ осуществляется от автономного высокостабильного генератора 2.

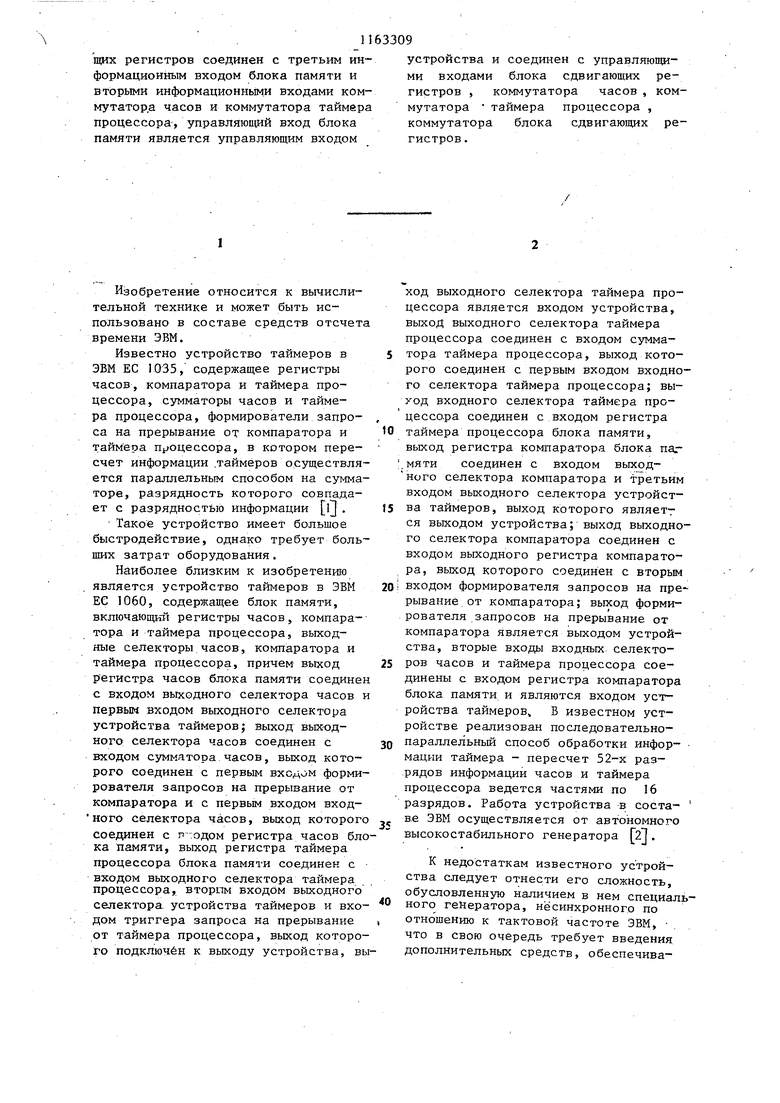

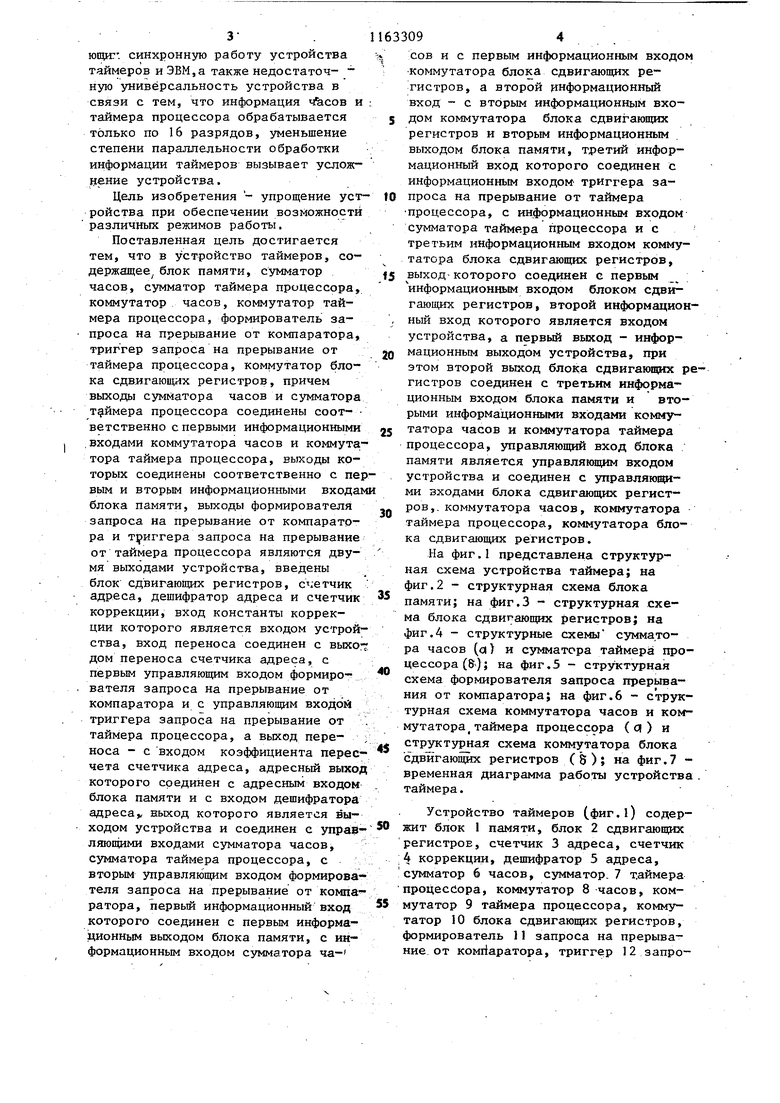

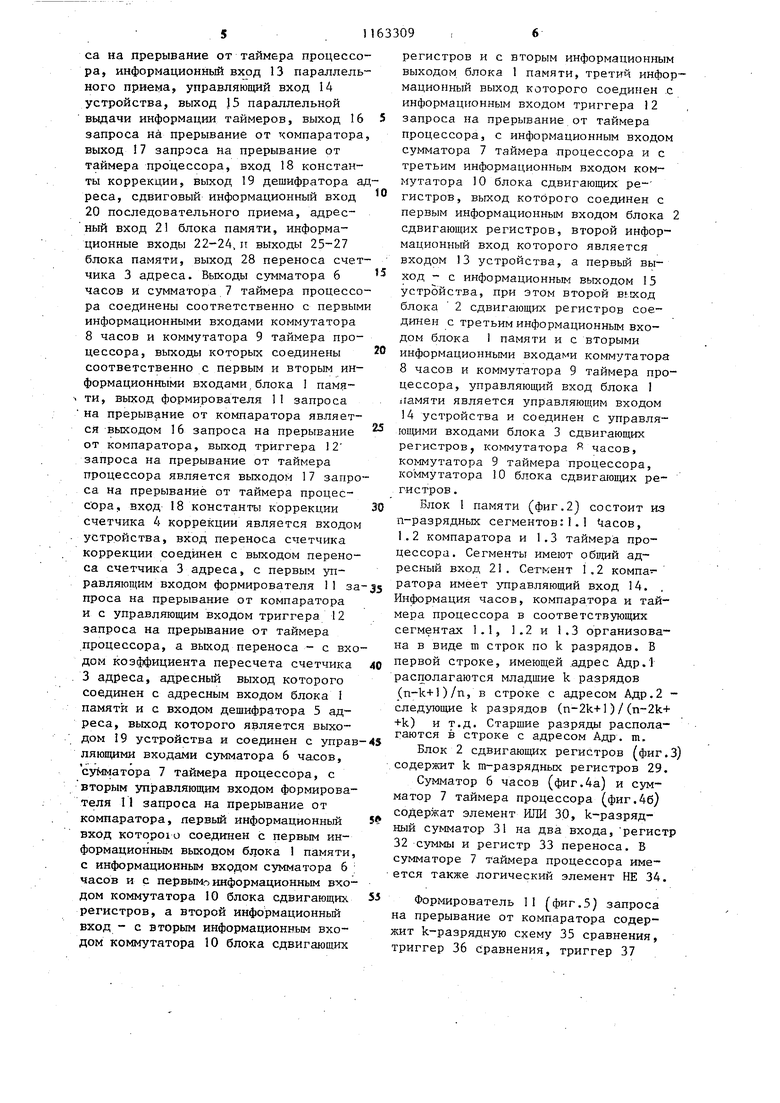

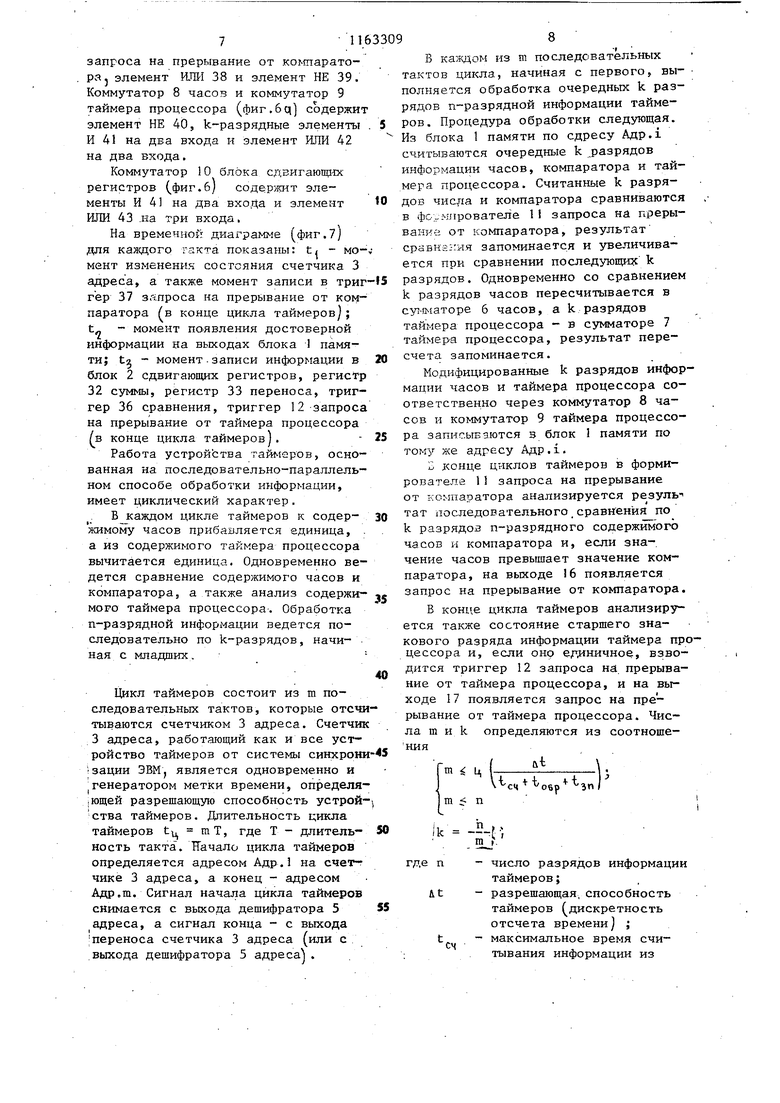

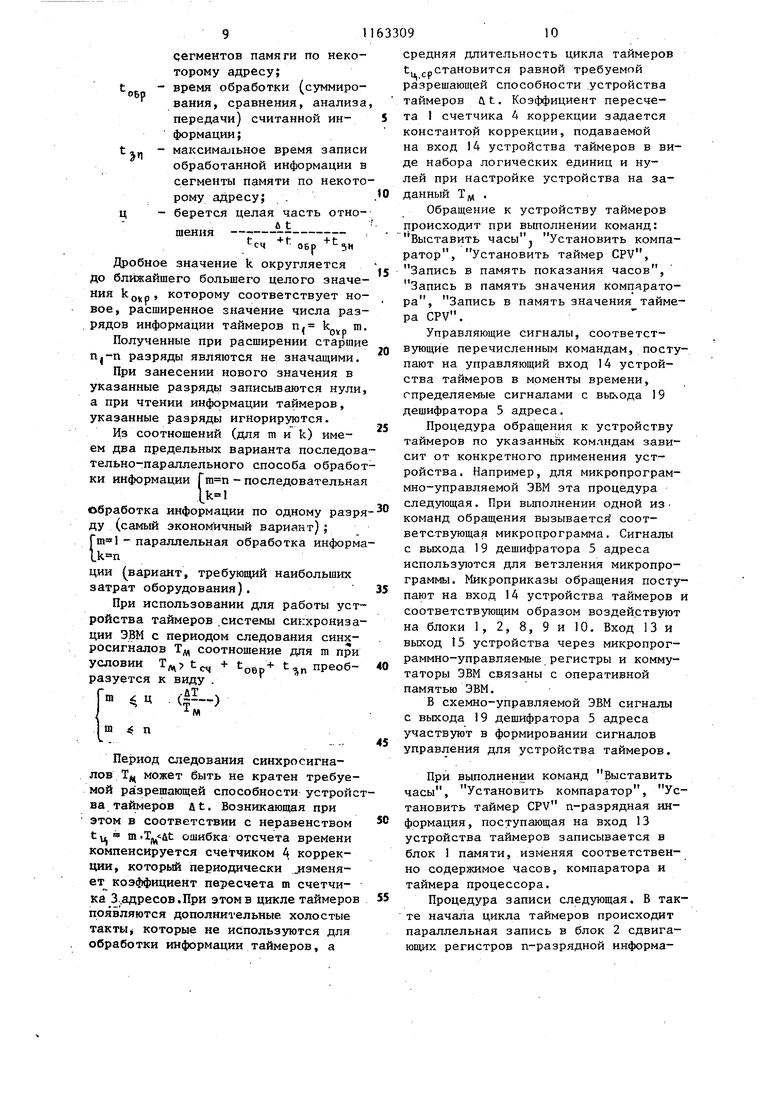

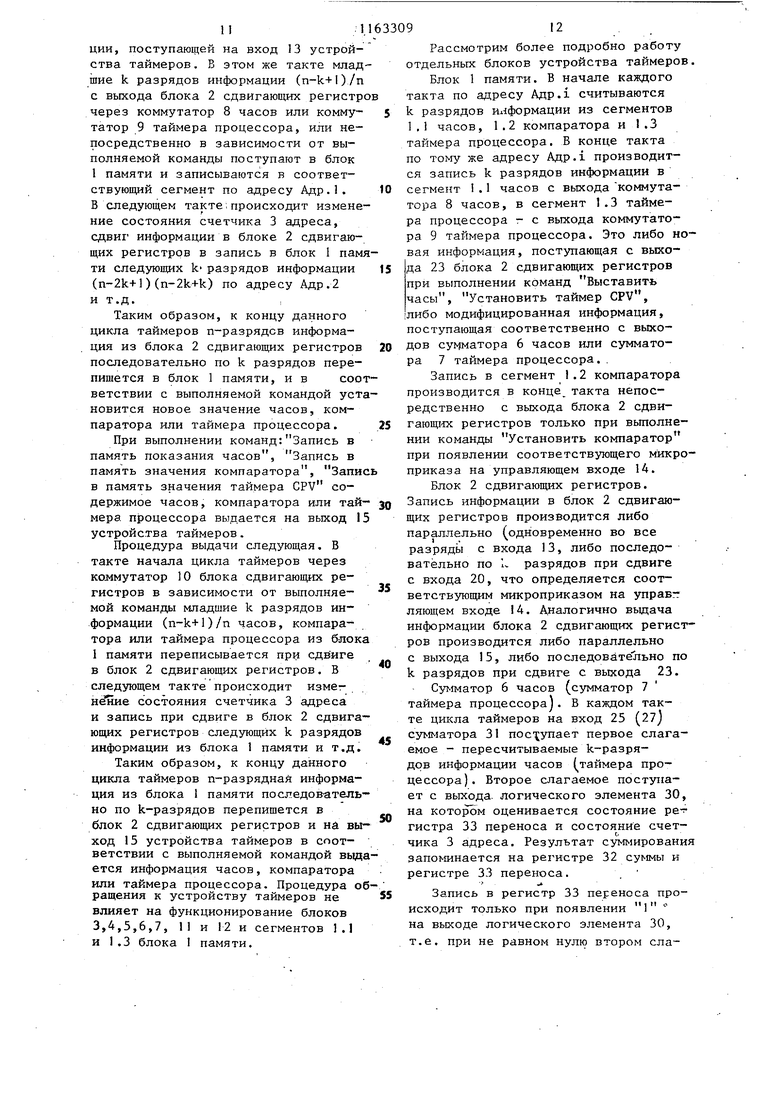

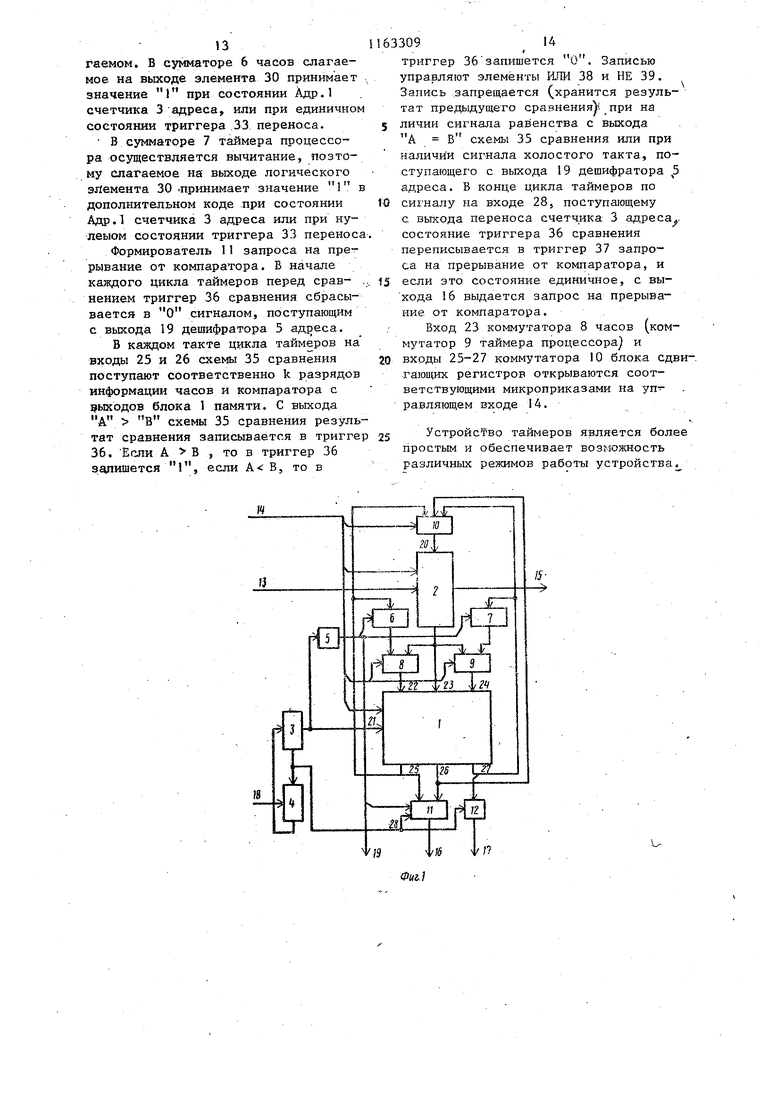

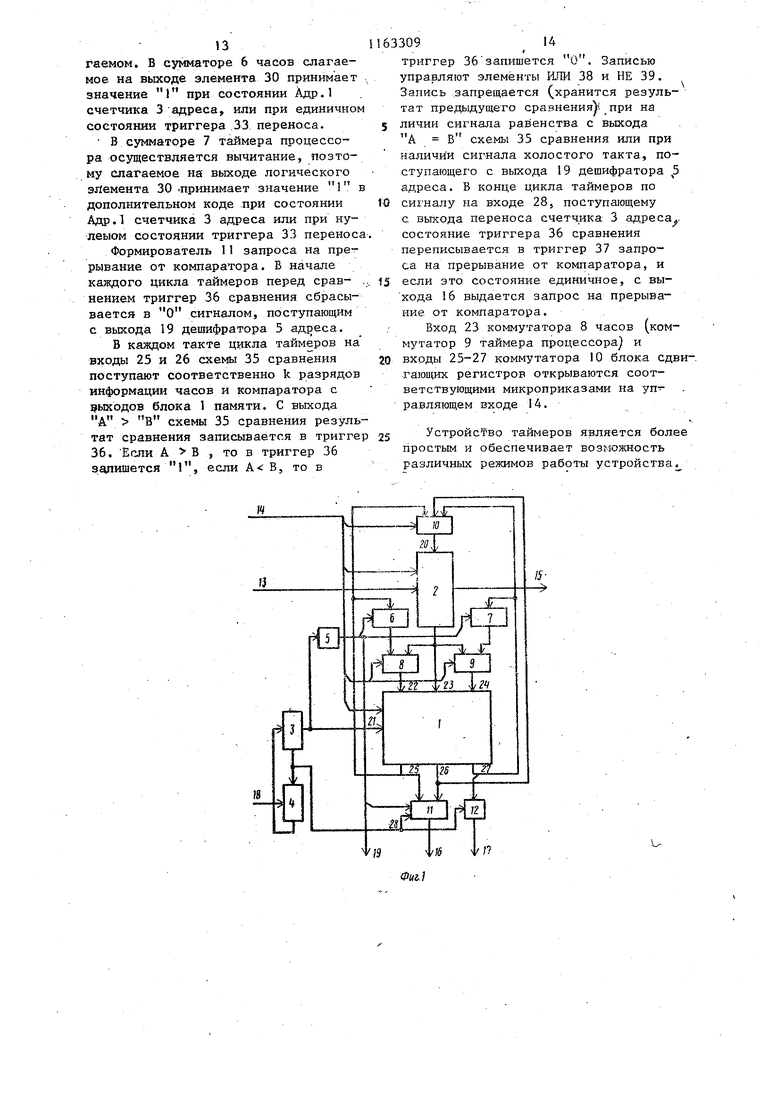

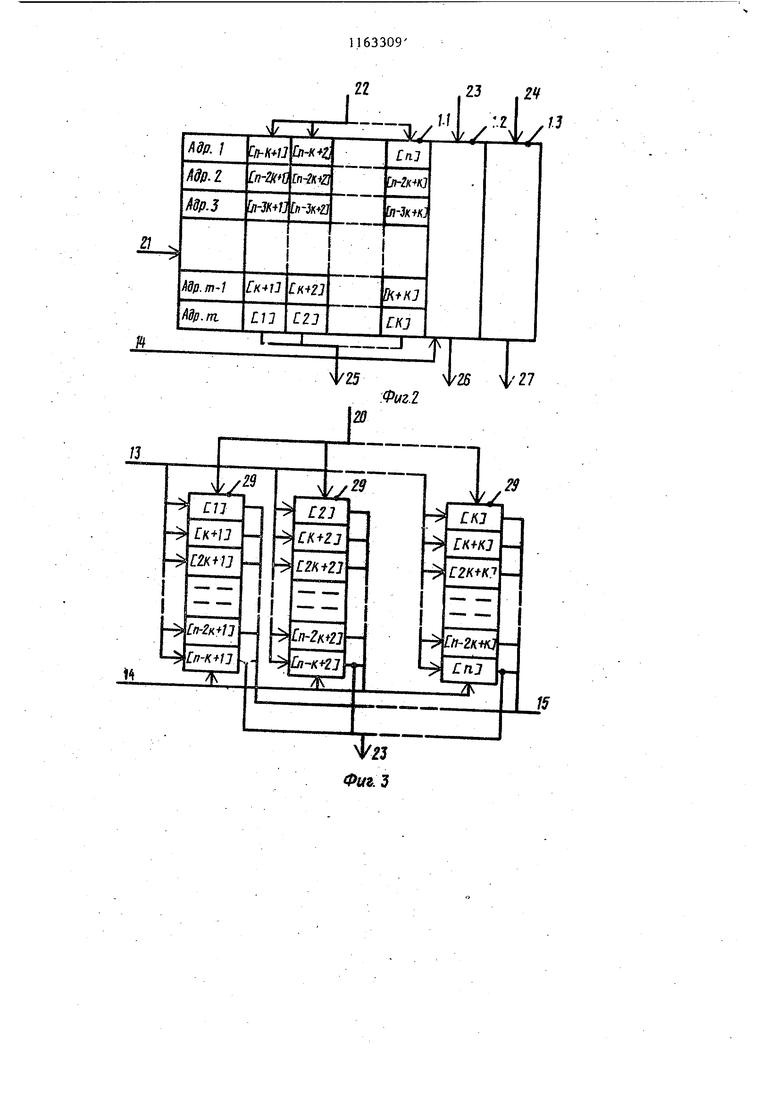

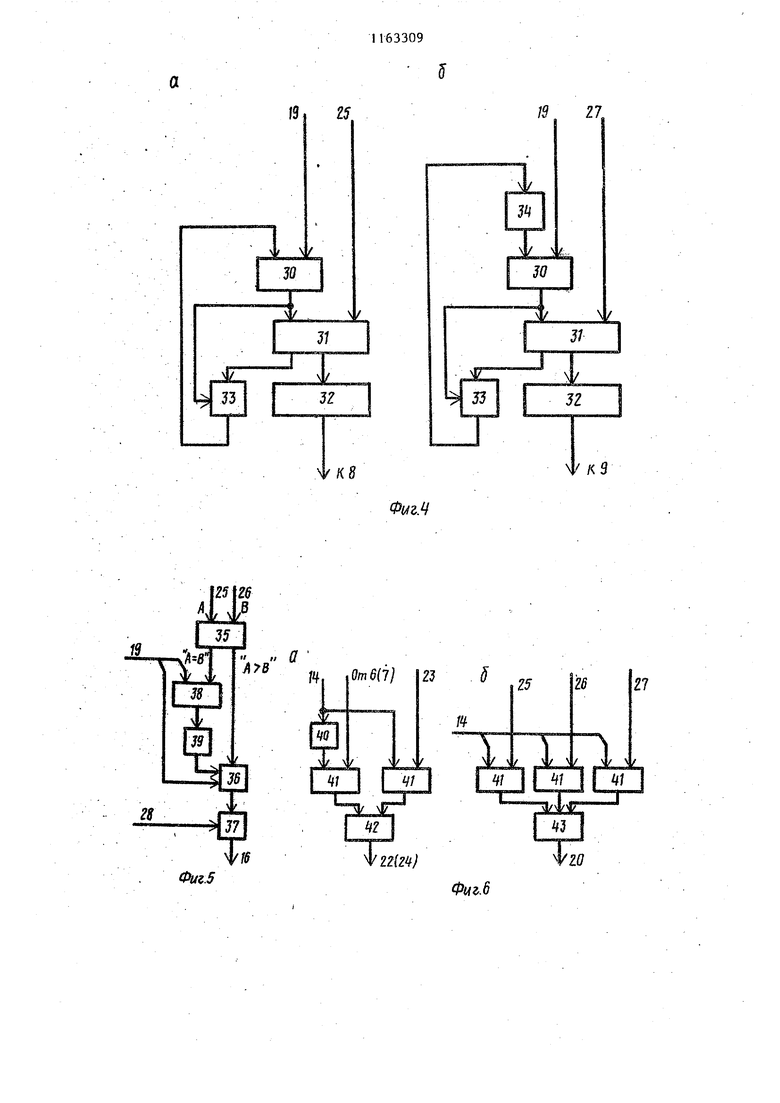

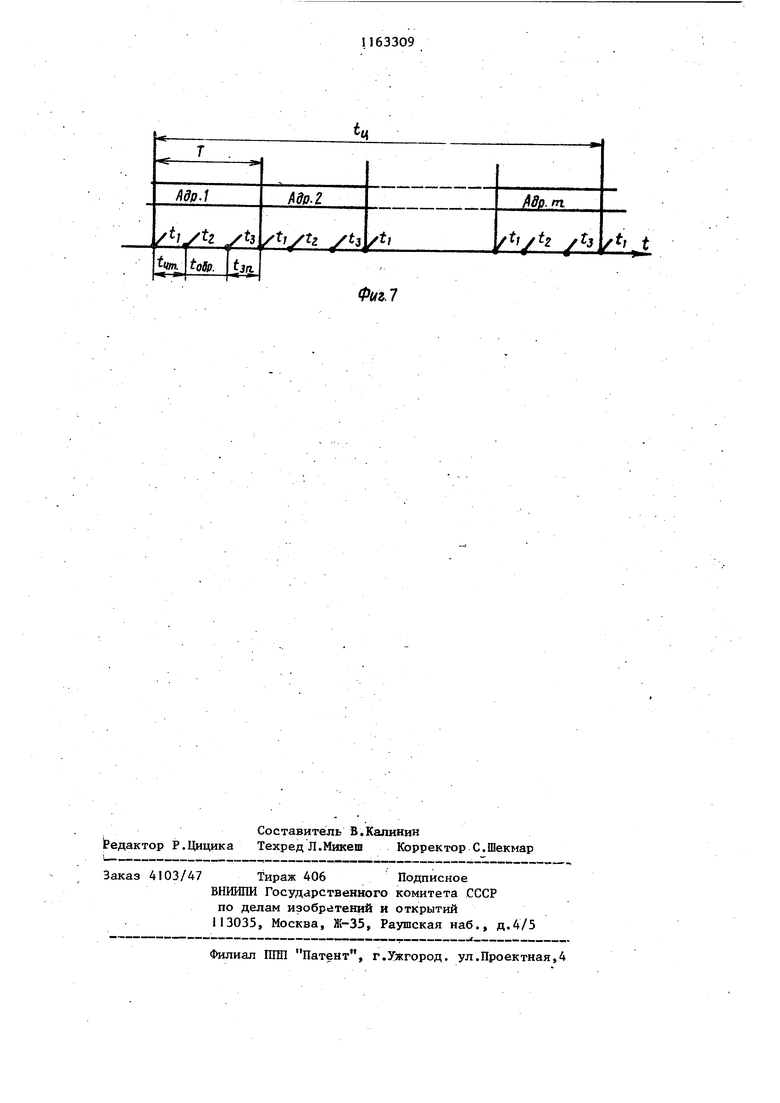

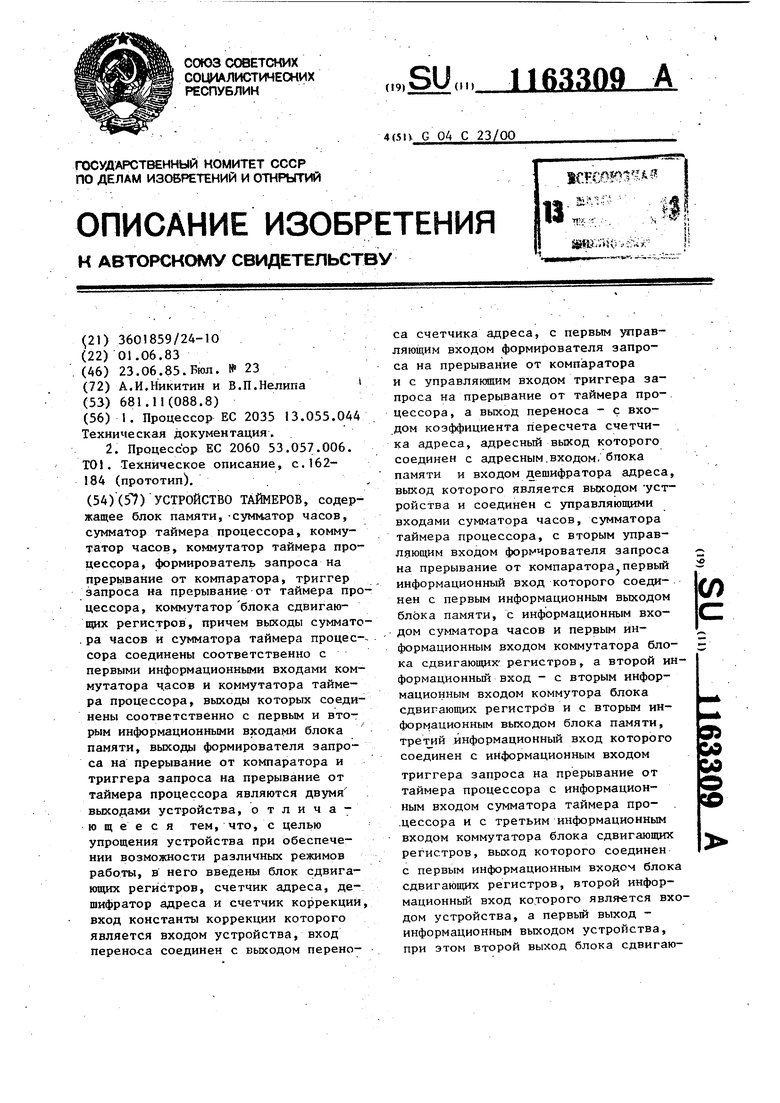

К недостаткам известного устройства следует отнести его сложность, обусловленную наличием в нем специалного генератора, несинхронного по отношению к тактовой частоте ЭВМ, что в свою очередь требует введения дополнительных средств, обеспечивающи:: синхронную работу устройства таймеров и ЭВМ,а также недостаточ- ную универсальность устройства в связи с тем, что информация и таймера процессора обрабатывается только по 16 разрядов, уменьшение степени параллельности обработки информации таймеров вызывает усложрение устройства. Цель изобретения - упрощение уст ройства при обеспечении возможности различных режимов работы. Поставленная цель достигается тем, что в устройство таймеров, со- держащее блок памяти, сумматор часов, сумматор таймера процессора, коммутатор часов, коммутатор таймера процессора, формирователь за проса на прерывание от компаратора, триггер запроса на прерывание от таймера процессора, коммутатор блока сдвигаюир х регистров, причем выходы сумматора часов и сумматора таймера процессора соединены соответственно с первыми информационными входами коммутатора часов и коммута тора таймера процессора, выходы которых соединены соответственно с пе вым и BTopt iM информационными входа блока памяти, выходы формирователя запроса на прерывание от компаратора и триггера запроса на прерывание от таймера процессора являются двумя выходами устройства, введены блок сдвигающих регистров, с;етчик адреса, дешифратор адреса и счетчик коррекции, вход константы коррекции которого является входом устрой ства, вход переноса соединен с выхо дом переноса счетчика адреса, с первым управляющим входом формиро. вателя запроса на прерывание от компаратора и с управляющим входой триггера запроса на прерывание от таймера процессора, а выход переноса - с входом коэффициента перес чета счетчика адреса, адресный выхо которого соединен с адресным входом блока памяти и с входом дешифратора адреса ныход которого является выходом устройства и соединен с управ ляющими входами сумматора часов, сумматора таймера процессора, с вторым зшравляюпщм входом формирова теля запроса на прерывание от компв ратора, первый информационный вход которого соединен с первым информационным выходом блока памяти, с информационным входом сумматора ча- сов и с первым информационным входом коммутатора блока сдвигающих регистров, а второй информационный вход - с вторым информационным входом коммутатора блока сдвигающих регистров и вторым информационным выходом блока памяти, третий информационный вход которого соединен с информационным входом- триггера запроса на прерывание от таймера процессора, с информационным входом сумматора таймера процессора и с третьим информационным входом коммутатора блока сдвигающих регистров, выход-которого соединен с первым информационным входом блоком сдвигающих регистров, второй информационный вход которого является входом устройства, а первый выход - информационным выходом устройства, при этом второй выход блока сдвигающих регистров соединен с третьим информационным входом блока памяти и вторыми информационными входами коммутатора часов и коммутатора таймера процессора, управляющий вход блока памяти является управляющим входом устройства и соединен с управляющими входами блока сдвигающих регистров,, коммутатора часов, коммутатора таймера процессора, коммутатора блока сдвигающих регистров. На фиг.1 представлена структурная схема устройства таймера; на фиг.2 - структурная схема блока памяти; на фиг.З - структурная схема блока сдвигающих регистров; на фиг.4 структурные схемы сумматора часов (а У и сумматора таймера процессора (5-); на фиг.5 - структурная схема формирователя запроса прерывания от компаратора; на фиг.6 - структурная схема коммутатора часов и коммутатора таймера процессора (а) и структурная схема коммутатора блока сдвйгаюпщх регистров (S) на фиг.7 временная диаграмма работы устройства . таймера. Устройство таймеров (фиг.1) содержит блок 1 памяти, блок 2 сдвигающих регистров, счетчик 3 адреса, счетчик 4 коррекции, дешифратор 5 адреса, сумматор 6 часов, сумматор. 7 таймера процессора, коммутатор 8 часов, коммутатор 9 таймера процессора, коммутатор 10 блока сдвигающих регистров, формирователь 1 запроса на прерывание, от KOMiiapaTopa, триггер 12 запро- са на прерывание от таймера процессо ра, информационньй вход 13 параллель ного приема, управляющий вход 14 устройства, выход J5 параллельной выдачи информации таймеров, выход 16 запроса на прерывание от компаратора выход 17 запроса на прерывание от таймера процессора, вход 18 константы коррекции, выход 19 дешифратора а реса, сдвиговый информационный вход 20 последовательного приема, адресный вход 21 блока памяти, информационные входы 22-24, It выходы 25-27 блока памяти, выход 28 переноса счет чика 3 адреса. Выходы сумматора 6 часов и сумматора 7 таймера процессо ра соединены соответственно с первым информационными входами коммутатора 8 часов и коммутатора 9 таймера процессора, выходы которых соединены соответственно с первым и вторым информационными входами.блока 1 памяти, выход формирователя 1 I запроса на прерывание от компаратора является выходом 16 запроса на прерывание от компаратора, выход триггера 12 запроса на прерывание от таймера процессора является выходом 17 запро са на прерывание от таймера процессора, вход 18 константы коррекции счетчика Д коррекции является входом устройства, вход переноса счетчика коррекции соединен с выходом переноса счетчика 3 адреса, с первым управляющим входом формирователя П за проса на прерывание от компаратора и с управляющим входом триггера 12 запроса на прерывание от таймера процессора, а выход переноса - с вхо дом коэффициента пересчета счетчика . 3 адреса, адресный выход которого соединен с адресным входом блока I памяти и с входом дешифратора 5 адреса, выход которого является выходом 19 устройства и соединен с управ ляющими входами сумматора 6 часов, суйматора 7 таймера процессора, с вторым управляющим входом формирователя 11 запроса на прерывание от компаратора, первый информационный вход которою соединен с первым информационным выходом блока 1 памяти с информационным входом сумматора 6 часов и с первымоинформационным входом коммутатора 10 блока сдвигающих регистров, а второй информационный вход - с вторьм информационным входом коммутатора 10 блока сдвигающих регистров и с вторым информационным выходом блока 1 памяти, третий информационный выход которого соединен .с информационным входом триггера 12 запроса на прерывание от таймера процессора, с информационным входом сумматора 7 таймера процессора и с третьим информационным входом коммутатора 10 блока сдвигающих регистров, выход которого соединен с первым информационным входом блока 2 сдвигающих регистров, второй информационный вход которого является входом 13 устройства, а первьй выход - с информационным выходом 15 устройства, при этом второй вьжод блока 2 сдвигающих регистров соединен с третьим информационным входом блока 1 памяти и с вторыми информационными входами коммутатора 8 часов и коммутатора 9 таймера процессора, управляющий вход блока 1 памяти является управляющим входом 14 устройства и соединен с управляющими входами блока 3 сдвигающих регистровJ коммутатора часов, коммутатора 9 таймера процессора, коммутатора 10 блока сдвигаюпщх регистров , Блок I памяти (фиг.2 состоит из п-разрядных сегментов:1.I Часов 1.2 компаратора и 1.3 таймера процессора. Сегменты имеют обпщй адресный вход 21. Сегмент 1,2 компаратора имеет управляющий вход 14. , Информация часов, компаратора и таймера процессора в соответствующих сегментах 1.1, 1.2 и 1.3 организована в виде m строк по k разрядов. В первой строке, имеющей .адрес Адр.Т располагаются младшие k разрядов (п-1с+1)/п, в строке с адресом Адр.2 следующие k разрядов {n-2k+l)/(n-2k+ +k) и т.д. Старшие разряды располагаются в строке с адресом Адр. т. Блок 2 сдвигаюпщх регистров (фиг.З) содержит k m-разрядных регистров 29. Сумматор 6 часов (фиг.4а) и сумматор 7 таймера процессора (фиг.4б) содержат элемент ИЛИ 30, k-разрядный сумматор 31 на два входа,регистр 32 суммы и регистр 33 переноса. В сумматоре 7 таймера процессора имеется также логический элемент НЕ 34. Формирователь 11 (фиг.5} запроса на прерывание от компаратора содержит k-разрядную схему 35 сравнения, триггер 36 сравнения, триггер 37 711 запроса на прерывание от компаратора j элемент ИЛИ 38 и элемент НЕ 39. Коммутатор 8 часов и коммутатор 9 таймера процессора (фиг.бч содержи элемент НЕ 40, и разрядные элементы И 41 на два входа и элемент ИЛИ 42 на два входа. Коммутатор 10 блока сдвигающих регистров (фиг.б) содеряшт элементы И 41 на два входа и элемент ИЛИ 43 .на три входа, На временной диаграмме (фиг.) для каждого гакта показаны: t, - мо- мент изменения состояния счетчика 3 адреса, а также момент записи в триг гер 37 запроса на прерывание от компаратора (в конце цикла таймеров); t - момент появления достоверной информации на выходах блока 1 памяти; t - момент.записи информации в блок 2 сдвигающих регистров, регистр 32 суммы, регистр 33 переноса, триггер 36 сравнения, триггер 12 запроса на прерывание от таймера процессора (в конце цикла таймеров). Работа устройства таймеров, основанная на последовательно-параллельном способе обработки информации, имеет циклический характер. В каждом цикле таймеров к содержимому часов прибавляется единица, а из содержимого таймера процессора вычитается единица. Одновременно ведется сравнение содержимого часов и компаратора, а также анализ содержимого таймера процессора. Обработка п-разрядной информации ведется последовательно по k-разрядов, начиная с младших, Цикл таймеров состоит из m последовательных тактов, которые отсч тываются счетчиком 3 адреса. Счетчи 3 адреса, работающий как и все устройство таймеров от системы синхрон зации ЭВМ, является одновременно и генератором метки времени, определя |Ющей разрешающую способность устрой ства таймеров. Длительность цикла таймеров t га Т, где Т - длительность такта. Начало цикла таймеров определяется адресом Адр.1 на счетчике 3 адреса, а конец - адресом Адр,т. Сигнал начала цикла таймеров снимается с выхода дешифратора 5 адреса, а сигнал конца - с выхода переноса счетчика 3 адреса (или с выхода дешифратора 5 адреса . В каждом из m последовательных тактов цикла., начиная с первого, вы- полняется обработка очередных k разрядов п-разрядной информации таймеров. Процедура обработки следующая. Из блока 1 памяти по сдресу Адр.1 считываются очередные k ,разрядов информации часов, компаратора и таймера процессора. Считанные k разрядов числа и компаратора сравниваются в фс м{ рователе 1 i запроса на прерывание от компаратора, результат сравнйкня запоминается и увеличивается при сравнении последующих k разрядов. Одновременно со сравнением k разрядов часов пересчитывается в сутматоре 6 часов, а k разрядов таймера процессора - в сумматоре 7 таймер-а процессора, результат пересчета запоминается. Модифицированные k разрядов информации часов и таймера процессора соответственно через коммутатор 8 часов и коммутатор 9 таймера процессора записыЕзются з блок 1 памяти по тому же адресу Адр.. I-. конце циклов таймеров в формирователе 11 запроса на прерывание от Kor-snapaTopa анализируется ре зультат последовательного сравнения по k разрядов п-разрядного содержимого часов и компаратора и, если значение часов превышает значение компаратора, на выходе 16 появляется запрос на прерывание от компаратора. В KOHie цикла таймеров анализируется также состояние старшего знакового разряда информации таймера процессора и, если оно едд1ничное, взводится триггер 12 запроса на прерывание от таймера процессора, и на выходе 17 появляется запрос на прерывание от таймера процессора. Числа m и k определяются из соотноше- ния (. ь m. число разрядов информации таймеров; разрешающая, способность таймеров (дискретность отсчета времени) ; максимальное время считывания информации из сегментов памяти по некоторому адресу; -время обработки (суммирования, сравнения, анализа передачи) считанной информации;-максимальное время записи обработанной информации в сегменты памяти по некото рому адресу; . ц - берется целая часть отноfi t шения -J СЧ ОБр -5Н Дробное значение k округляется до ближайшего большего целого значе ния , которому соответствует новое, расширенное значение числа разрядов информации таймеров п k m Полученные при расширении старшие П|-п разряды являются не значащими. При занесении нового значения в указанные разряды записываются нули а при чтении информации таймеров, указанные разряды игнорир тся. Из соотношений (для m и k) имеем два предельных варианта последова тельно-параллельного способа обработ ки информации - последовательная обработка информации по одному разря ду (самый экономичный вариант); Гт - параллельная обработка информа ции (вариант, требующий наибольших затрат оборудования). При использовании для работы устройства таймеров .системы синхронизации с периодом следования синхросигналов Тд, соотношение для m при Период следования синхросигналов может быть не кратен требуемой разрешающей способности устройс ва таймеров At. Возникающая при этом в соответствии с неравенством t ц m T. ошибка отсчета времени компенсируется счеТчиком 4 коррекции, который периодически .изменяет коэффициент пересчета m счетчика 3,адресов.При этом в цикле таймеров появляются дополни1ельные холостые тактыj которые не используются для обработки информации таймеров, а средняя длительность цикла таймеров t gpстановится равной требуемой разрешающей способности .устройства таймеров ut. Коэффициент пересчета 1 счетчика 4 коррекции задается константой коррекции, подаваемой на вход 14 устройства таймеров в виде набора логических единиц и нулей при настройке устройства на заданный TIY, . Обращение к устройству таймеров происходит при выполнении команд: Выставить часы Установить компаратор, Установить таймер CPV, Запись в память показания часов, Запись в память значения компаратора, Запись в память значения таймера CPV. Управляющие сигналы, соответствующие перечисленным командам, поступают на управляющий вход 14 устройства таймеров в моменты времени, определяемые сигналами с выхода 19 дешифратора 5 адреса. Процедура обращения к устройству таймеров по указаиньгх командам зависит от конкретного применения устройства. Например, для микропрограммно-управляемой ЭВМ эта процедура следующая. При вьшолнении одной из команд обращения вызываете соответствующая микропрограмма. Сигналы с выхода 19 дешифратора 5 адреса используются для ветзления микропрограммы. Микроприказы обращения поступают на вход 14 устройства таймеров и соответствующим образом воздей.ствуют на блоки 1, 2, 8, 9 и 10, Вход 13 и выход 15 устройства через микропрограммно-управляемые регистры и коммутаторы ЭВМ связаны с оперативной памятью ЭВМ, В схемно-управляемой ЭВМ сигналы с выхода 19 дешифратора 5 адреса участвуют в формировании сигналов управления для устройства таймеров, При выполнении команд Выставить часы, Установить компаратор, Установить таймер CPV п-разрядная информация, поступающая на вход 13 устройства таймеров записывается в блок 1 памяти, изменяя соответственно содержимое часов, компаратора и таймера процессора. Процедура записи следующая. В такте начала цикла таймеров происходит параллельная запись в блок 2 сдвигающих регистров п-разрядной информации, поступающей на вход 13 устройства таймеров. В этом же такте млад шие k разрядов информации (n-k+I)/n с выхода блока 2 сдвигающих регистр через коммутатор 8 часов или коммутатор 9 таймера процессора, или непосредственно в зависимости от выполняемой команды поступают в блок 1 памяти и записываются в соответствующий сегмент по адресу Адр.1. В следующем такте;происходит измене ние состояния счетчика 3 адреса, сдвиг информации в блоке 2 сдвигающих регистров в запись в блок 1 пам ти следующих k- разрядов информации (n-2k+l)(n-2k+k) по адресу Адр.2 и т.д. Таким образом, к концу данного цикла таймеров п-разрядсв информация из блока 2 сдвигающих регистров последовательно по k разрядов перепишется в блок 1 памяти, и в соо ветствии с выполняемой командой уст новится новое значение часов, компаратора или таймера процессора. При выполнении команд: Запись в память показания часов, Запись в память значения компаратора, Запи в память значения таймера CPV содержимое часов, компаратора или тай мера процессора выдается на выход 1 устройства таймеров. Процедура выдачи следующая. В такте начала цикла таймеров через коммутатор 10 блока сдвигающих регистров в зависимости от выполняемой команды младшие k разрядов информации (n-k+1)/п часов, компаратора или таймера процессора из блок 1 памяти переписывается при сдвиге в блок 2 сдвигающих регистров. В следующем такте происходит измег нЙ1ие состояния счетчика 3 адреса и запись при сдвиге в блок 2 сдвига ющих регистров следующих k разрядов информации из блока 1 памяти и т.д. Таким образом, к концу данного цикла таймеров п-разрядная информация из блока 1 памяти последователь но по k-разрядов перепишется в блок 2 сдвигающих регистров и ни вы ход 15 устройства таймеров в соответствии с выполняемой командой выд ется информация часов, компаратора или таймера процессора. Процедура о ращения к устройству таймеров не влияет на функционирование блоков 3,5,6,7, II и 12 и сегментов 1.1 и 1 .3 блока I памяти. Рассмотрим более подробно работу отдельных блоков устройства таймеров. Блок 1 памяти. В начале каждого такта по адресу Адр.1 считываются k разрядов Ш1формации из сегментов 1,1 часов, 1.2 компаратора и 1.3 таймера процессора. В конце такта по тому же адресу Адр.1 производится запись k разрядов информации в сегмент 1.1 часов с выхода коммутатора 8 часов, в сегмент 1.3 таймера процессора - с выхода коммутатора 9 таймера процессора. Это либо новая информация, поступающая с выхода 23 блока 2 сдвигающих регистров при выполнении команд Выставить часы, Установить таймер CPV, либо модифицированная информация, поступающая соответственно с выходов сумматора 6 часов или сумматора 7 таймера процессора.. Запись в сегмент 1.2 компаратора производится в конце такта непосредственно с выхода блока 2 сдвигающих регистров только при вьшолне- НИИ команды Установить компаратор при появлении соответствующего микроприказа на управляющем входе 14. Блок 2 сдвигающих регистров. Запись информации в блок 2 сдвигающих регистров производится либо параллельно (одновременно во все разряды с входа 13, либо последовательно по 1. разрядов при сдвиге с входа 20, что определяется соответствующим микроприказом на управляющем входе 14. Аналогично выдача информации блока 2 сдвигающих регистров производится либо параллельно с выхода 15, либо последовательно по k разрядов при сдвиге с выхода 23. Сумматор 6 часов (сумматор 7 таймера процессора). В каждом такте цикла таймеров на вход 25 (27) сумматора 31 пос упает первое слагаемое - пересчитываемые k-разрядрв информации часов (таймера процессора). Второе слагаемое поступает с выхода, логического элемента 30, на которюм оценивается состояние регистра 33 переноса и состояние счетчика 3 адреса. Результат суммирования запоминается на регистре 32 суммы и регистре 33 переноса. . Запись в регистр 33 переноса происходит только при появлении 1 на выходе логического элемента 30, т.е. при не равном нулю втором ела13гаемом. В сумматоре 6 часов слагаемое на выходе элемента 30 принимает значение 1 при состоянии Адр.1 счетчика 3 ;адреса, или при единично состоянии триггера 33 переноса. В сумматоре 7 таймера процессора осуществляется вычитание, позтому слагаемое на выходе логического элемента 30 .принимает значение 1 дополнительном коде при состоянии Адр.1 счетчика 3 адреса или при нулеыом состоянии триггера 33 перенос Формирователь 1 запроса на прерывание от компаратора. В начале каждого цикла таймеров перед сравнением триггер 36 сравнения сбрасывается в О сигналом, поступающим с выхода 19 дешифратора 5 ащеса, В каждом такте цикла таймеров на входы 25 и 26 схемы 35 сравнения поступают соответственно k разрядо информации часов и компаратора с выходов блока 1 памяти. С выхода А в схемы 35 сравнения резул тат сравнения записывается в тригг 36. Если А В , то в триггер 36 запишется 1, если А В, то в

W

U 30914 триггер 36запишется О. Записью управляют элементы ИЛИ 38 и НЕ 39. Запись запрещается (хранится результат предыдущего сравнения при на личии сигнала равенства с выхода А в схемы 35 сравнения или при наличии сигнала холостого такта, поступающего с выхода 19 дешифратора 5 адреса. В конце цикла таймеров по сигналу на входе 28, поступающему с выхода переноса счетчика 3 адреса,,. состояние триггера 36 сравнения переписывается в триггер 37 запроса на прерывание от компаратора, и если это состояние единичное, с выхода 16 выдается запрос на прерывание от компаратора. Вход 23 коммутатора 8 часов (коммутатор 9 таймера процессора и входы 25-27 коммутатора 10 блока сдвигающих регистров открываются соответствующими микроприказами на управляющем входе 14. Устройство таймеров является более простым и обеспечивает воз южность различных режимов работы устройства. Фиг.З

VfJ

а

19 2S

l

/

J/

Ж.

зг

33

Фк

/5 27

L

30

зг

ж:

53

52

l/ КЗ

Фи.5

Фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ окрашивания в черный цвет продуктов конденсации фенолов с формальдегидом | 1924 |

|

SU2035A1 |

| Техническая документация | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| TOI | |||

| Техническое описание, с.162184 (прототип)., | |||

Авторы

Даты

1985-06-23—Публикация

1983-06-01—Подача