ки в единицу перэого счетчика является вторым управляющим входом узла тарировки, вход установки в ноль второго счетчика и вход разрешения

записи регистра объединены и являются третьим управляющим входом узла тарировки, а выход регистра является выходом узла тарировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1383398A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

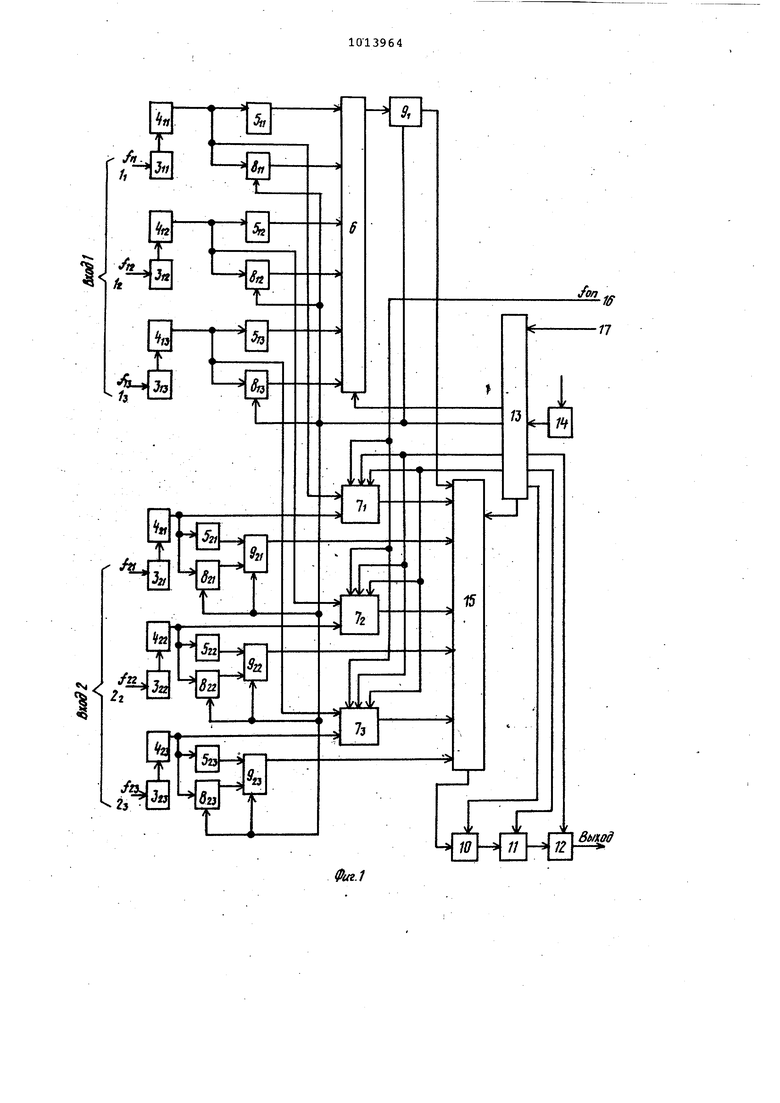

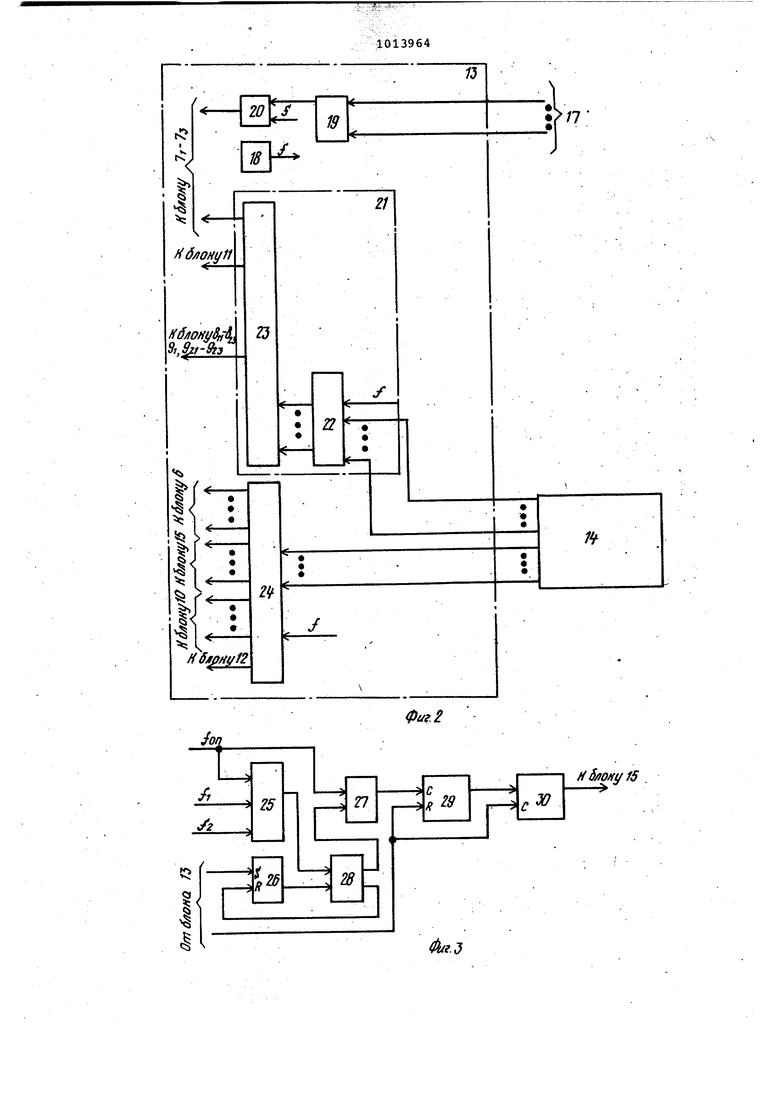

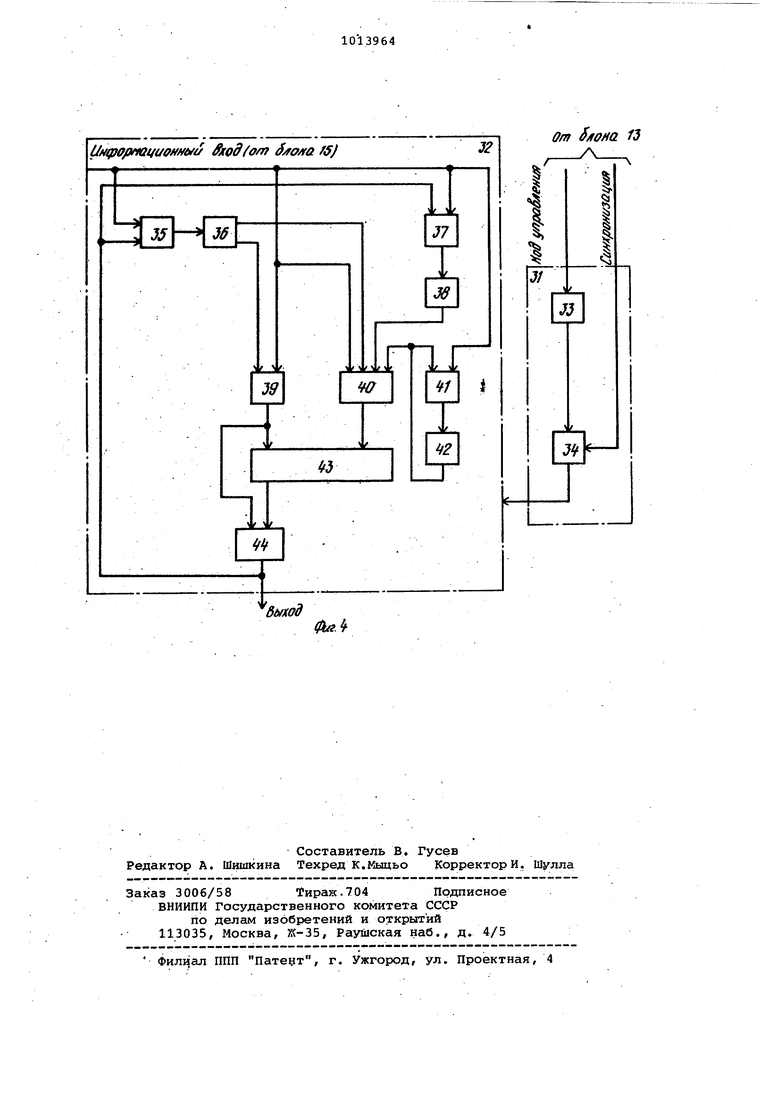

Изобретение относится к вычислительной и информационно измерительной технике и может быть использова но в качестве преобразователя инфор мации , получаемой с датчиков с част ным выходом, в частности струнных, пьезоэлектрических и т.д. Известно устройство, содержащее в каждом измерительном канале после довательно соединенные усилитель, триггер Шмитта и удвоитель частоты, счетчик, выход которого через регис подключен к соответствующему входу арифметического.блока, блок управле ния и регистр индикацииfl 3. Недостатком устройства является небольшой коэффициент использования оборудования, так как устройство предназначено для работы с датчиком имеквдим одну измерительную и одну опорную частоты. Наиболее близким по технической сущности к изобретению является вычи лительное устройство, содержащее в каждом измерительном канале послед вательно соединенные усилитель, триг гер Шмитта и умножитель частоты, счетчик, причем входы усилителей сое динены с соответствующими входами устройства, первый, второй и третий регистры, блок управления,KOMiviyTaTOp арифметический блок, выход которого через выходной регистр соединен с блоком индикации, выход которого является выходом устройства, управляющие входы счетчиков, первого, второго и третьего регистров, комлутатора, ари4 1етического блока, выходного регистра и блока индикации соединены с соответствующими выходами блока управления, вход которого соединен с выходом блока постоянной памяти Недостатком устройства является пониженная точность вычислений, поскольку оно не учитывает начальную частоту датчика. Целью изобретения является повышение точности вычиcлeFшй, Поставленная- цель достигается тем, что в вычислительное устройство, содержащее в каждом измерительном канале последовательно соединенные усилитель, триггер 13митта и умно житель частоты, счетчик, причем входы усилителей соединены ,с соответствующими входами устройства, первый, второй и третий регистры, блок управления, коммутатор, арифметический блок, выход которого через выходной регистр соединен с блоком индикации, выход которого является выходом устройства, а управлякидие входы счетчиков, первого, второго и третьего регистров, коммутатора, арифметического блока, выходного регистра и блока индикации, соединены с соответствукядими выходами блока управления, вход KOTOporQ соединен с выходом блока постоянной памяти, введены первый, второй и третий узлы тарировки, четвертый регистр и второй коммутатор, причем выходы умножителей частоты и счетчиков измерительных каналов первой группы соответственно соединены с входами первого коммутатора, выход которого соединен с информационным входом четвертого регистра, управляющий вход которого соединен с соответствующим выходом блока управления, выходы триггеров 1Ш 1Итта измерительных каналов первой группы соответственно соединены, с первыми информационными входами первого, второго и третьего узлов тарировки, выходы триггеров Шмитта измерительных каналов второй группы соответственно соединены с вторыми информационными входами первого, второго и третьего узлов тарировки, выходы первого, второго, третьего и четвертого регистров, первого, второго и третьего узлов тарировки соединены с соответствующими входами второго коммутатора, выход которого соединен с входом арифметического блока, а управляющий вход соединен с соответствующим выходом блока управления, первый, второй и третий управляющие входы первого, второго и третьего узлов тарировки соответственно объединены и сое.циненыс соответствующими выходами блока управления и с шиной опорной частоты устройства. Кроме того, каждый узел тарировки содержит вычитатель частот, триггер, элемент И, первый и второй счетчики и регистр, выкод вычитателя частот соединен со счетным входом первого счетчика, информационный выход которого соединен с первым входом злемаита И, выход переноса первого счетчикд-соединен, с входом установки в ноль триггера, инверсный выход которого соединен с установочным входом первого счетчика, выход элемента И соединен со счетным входом второго счетчика, выход которого соединен с информационным входом регистра, тактовый вход вычитателя час тот и второй вход элемента И объединены и являются первым управляющим входом узла тарировки, первый и второй входы вычитателя частот являются соответственно первым и вторым инфор мационными входами узла тарировки, вход установки в единицу первого счетчика является вторым управляющим входом узла тарировки, вход установки в ноль второго счетчика и вход разрешения записи регистра объединен и являются третьим управляющим входо узла тарировки, а выход регистра является выходом узла тарировки. На фиг.1 представлена функциональ ная схема устройства; на фиг.2 функциональная схема блока управления; на фиг.З - функциональная схем узла тарировки; на фиг.4 - функциоНсшьная схема арифметического блока Вычислительное устройство для дат чиков с частотным выходом содержит информационный вход 1 с входными шинами 1,., 1, информационный вход 2 с входными шиншли 2 , 2, 2 усилители 3, 3.у , 3, 3, у триггеры Шмитта 4 , .. , 4 , 431 , 14 423,умножители 5 . / 5 , / Sji частоты, первый коммутатор б, узлы 7 , 7, 7.j тарировки счетчики 8 , 8 .8 , 8, 8, 83 регистры 9 , 9,2.1 , 9 , 9 , арифметический блок 10, выходной регистр 11, блок 12 индикации, блок 13 упра ления, блок 14 постоянной памяти, второй коммутатор 15, шину 16 опор-: ной частоты и шину 17 кода команды Тарировка причем в каждом измерительном канале усилитель 3 , триг гер Шмитта 4 и умножитель частоты последовательно соединены (iномер измерительного канала, выход триггеров Шмитта 4 , 4 и , сое динены со счетными входами счетчиков 8 , 8 и 8 соответственно и с первыми входами узлов 7 , 7а,и 7э тарировки соответственно, выходы триггеров Шмитта 4, , и 4 .соединены со счетными входами счетчиков 8 , 82 и соответственно и с вторыми входагли узлов 7 , и 7 тарировки соответственно, выходы умножителей 5 , 5, и 5j частоты и выходы счетчиков 8 , и соединены с соответствую щими входами первого коммутатора б, выход которого соединен с информационньвл входом регистра 9 , выходы умножителей 5 , . и 5,j частоты соединены с информационными входами регистров 9 , 9 и 9.j соотвётственно, выходы счетчиков 8 , 8и 8 соединены с входами разрешения записи регистров 9 , 9 и 9, соответственно, выходы регистров гл I г-i гз выходы узлов 7, 7, 7 тарировки соединены с соответствующими входами второго коммутатора 15, выход которого соединен с входом арифметического блока 10, .юследовательно соединенного с выходньм регистром 11 и блоком 12 индикации, управляющие входда первого и второго коммутаторов б и 15 соединены с соответствующими вьвсодами блока 13 управления, установочный выход которого соединен с входами установки в ноль счетчиков 8 , 8 г 8 , 8,, 22 2г и регистров .9 , a-i ai a-i первые управляющие входы узлов 7 , 7 и Ij тарировки объединены и соединены с шиной 16 опорной частоты устройства,, вторые и третьи управляюоше входы узлов 7 , 7 и 7 тарировки соответствед но объединены и соединены с соответствующими выходами блока 13 управления, другие соответствующие выходы которого соединены с управляющими входами арифметического блока 10, выходного регистра 11 и блоЬа 12 индикации, первый вход блока 13 управления соединен с шиной 17 кода команды Тарировка, а второй вход - . с выходом блока 14 постоянной, йамяти устройства. Блок 13 управления содержит генератор 18 тактовых импульсов, дааифратор 19 кода команда Тарировка, устройство 20 синхронизации, блок21 распределения импульсов, состоящий из блока элементов И 22 и блока элементов ИЛИ 23, регистр 24, причем вход дешифратора 19 является первым входом блока 13 управления, выход дешифратора 19 соединен с управляющим входом устройства 20 синхронизации, тактовый вход которого соединен с выходом генератора 18 тактовых импульсов, первые входы блока элементов И 22 и информационные входы регистра 24 являются вторым входом блока 13 управления, вторие входы блока элементов И 22 объединены и соединены с входом разрешения записи регистра 24 и с выходом генератора 18 тактовых имнульсов, выходы блока элементов И 22 соединены с соответствующими входами блока элементов ИЛИ 23. Каждый из узлов 7 , 7, 7 тарировки содержит вычитатель 25 частот, триггер 26, элемент И 27, первый и второй счетчики 28 и 29 и регистр 30, причем выход вычитателя 25 частот соединен со счетным входом первого счетчика 28, информационный выход которого соединен с первым входом элемента И 27, выход переноса первого счетчика 28 соединен с входом установки в ноль триггера 26, инверсный выход которого соединен с установочным входом первого счетчика 28, выход элемента И 27 соедине со счетным входом второго счетчика 29, выход которого соединен с информационным входом регистра 30, тактовый вход вычитателя 25 частот и второй вход элемента И 27 объединены и являются первым управляюцщм входом . узла 7 тарировки, первый и второй входы вычитателя 25 частот являются соответстве.нно первым и вторым информационными входами узла 7 тарировки, вход установки в единицу первого счетчика 28 является вторым управляю щим входом узла тарировки, вход установки в ноль второго счетчика 29 и вход разрешения записи регистра 30 объединены и являются третьим управляющим входом узла 7,- тарировки, а выход регистра 30 является выходом узла тарировки.

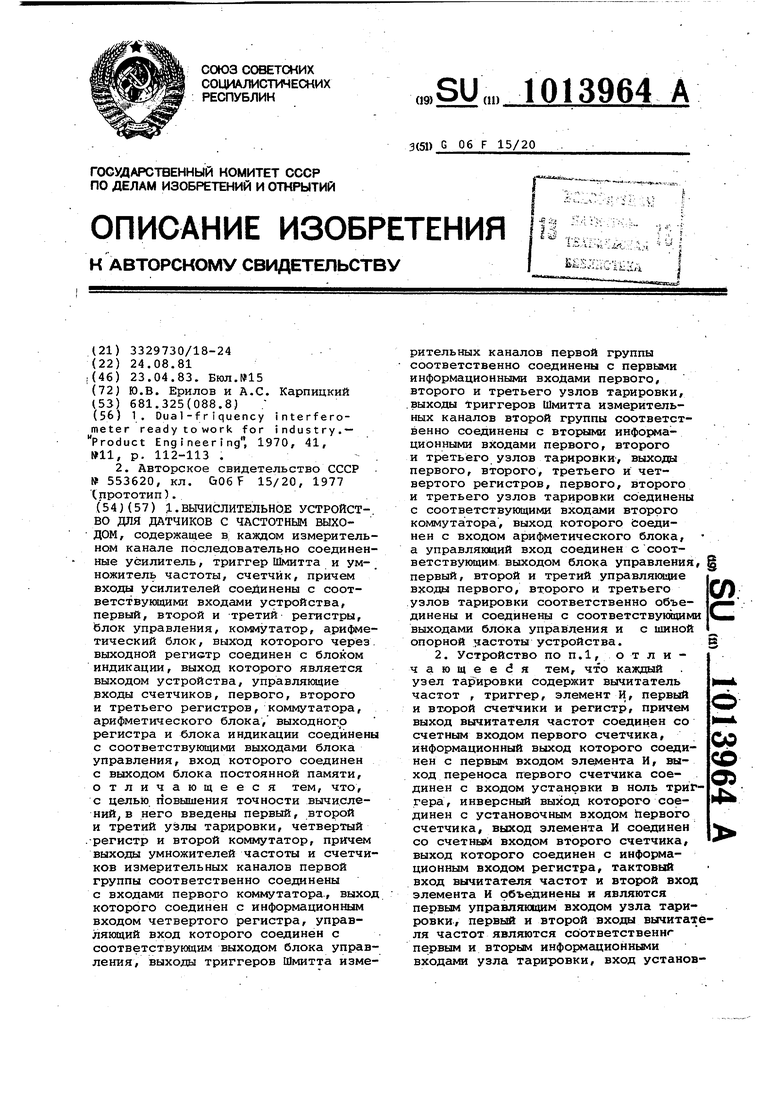

Арифметический блок 10 состоит из узла 31 управления и исполнительного устройства 32. Узел 31 управлеНИН содержит последовательно соединенные программируемую логическую матрицу 33 и операционный регистр 34, причем вход программируемой логической матрица 33 является информационным входом узла 31 управления, а выход операционного регистра 34 является выходом узла 31 управления, вход синхронизации которого соединен с управляющим входом операционного регисгра 34, ч

Исполнительное устройство 32 содержит коммутатор 35 регистрового запоминающего устройства, регистрово запоминающее устройство 36, коммутатор-37 рабочего регистра, рабочий , регистр 38, коммутаторы 39 и 40 oneрандов, коммутатор 41 дополнительног регистра, дополнительный регистр 42, арифметико-логическое устройство

43и коммутатор 44 выходных данных, причем первые входы коммутаторсэв 35, 37,39 40 и 41 объединены и являются информационным входом исполнительного устройства 32, вторые входы коммутаторов 35 и 37 и выход коммутатора

44объединены и являются выходок исполнительного устройства 32, вы™ ход коммутатора 35 соединен с входом запоминающего устройства 36, выходы которого соединены соответственно с вторыми входами коммутаторов 39 и

40, выход коммутатора 37 соединен с входом рабочего регистра 38, выход которого соединен с третьим входом коммутатора40, коммутатора

41 соединен с входом дополнительного регистра 42, выход которого соединен с. четвертым входом коммутатора 40 и вторым входом коммутатора 41, выходы коммутаторов 39 и 40 соединены соответственно с входами арифметикологического устройства 43, выход которого соединен с первым входом коммутатора 44 выходных данных, второй вход коммутатора 44 соединен с выходом коммутатора 39.

Устройство работает следующим Образом.

Информационные сигналы с выходов трех дифференциальных пар датчиков ( с первого датчика каждой пары сигнал поступает на соответствующую шину входа 1, с второго датчика - на соответствующую шину входа 2) или с трех пар датчик - источник опорного сигнала обрабатываются параллельно во. времени в трех идентичных каналах, каждый из которых содержит две функциональные цепочки элементов. Впервой функциональной цепочке канала производится обработка сигнала, поступившего на вход 1 устройства, во. второй функциональной цепочке этого же канала, поступившего на вход 2 устройства ( входные шины при этом имеют одинаковые индексы).

В арифметическом блоке 10 обработка сигналов каждой пары датчиков происходит последовательно во времени согласно задающей программе..

Один из трех каналов параллельной обработки работает следующим образом.

На входы 1 и 2,| поступают информационные сигналы с частотами f и f При прохождении входных сигналов через усилители 3 и 3/2.-1 и триггеры Шмитта 4 и 42 формируются последовательности прямоугольных импульсов с частотами следования и f , поступающие затем на входы умножителей

, частоты, на счетные вхо-i-t

ды счетчиков 3 и 8. шотульсов, на информационные .входы узла 7 .тарировки. Умножители 5 ;и 521частоты i при этом осуществляют умножение частоты следования импульсов в К раз. При опросе данного канала выходы умножителя 5 и счетчика 8 через коммутатор б подключаются к информационному входу ра.гистра 9 , что обеспечивает занесение в регистр 9 параллельный двоичный код в соответствии с выражениет:

выходной код при -S -м опро се данного канала, цикл внутреннего опроса; частота следования импульсов на Еходе умножител.я 5.

Одноэременно в регистр Oj заносится код в. соответствии с выражением

М,.;

Далее коммутатор 15 поочередно подключает регистры 9 и 92 к входу арифметического блока 10, в котором происходит обработка результатс в опросов по внутреннему циклу устройства, при этом вычисляется код в соответствии с выражением

-. р

Результат X И; хранится во внут

ренней памяти арифметического блока. При таком структурном построении устройства можно получить многоразр

рядное число г N: при использовании

jro d малоразрядных счетчиков 8 -и что существенно- снижает требования к быстродействию счетчиков 8 -ц и 8 Измерение начальной разности частот производится следующим образом.

При подаче на шину 17 кода команды Тарировка на четвертом выходе блока 13 управления вырабатывается импульс, который,поступая на входы запуска узлов 7 , 7, 1-) тарировки приводит их в исходное состояние и дает команду, по которой начинается измерение начальной разностной частоты. Одновременно в шину 16 поступает импульсная последовательность опорной частоты оп которая проходит на входы синхронизации узлов Ti г тарировки.

При опросе данного канала вслед за счетчиками 8 , 8 и умножите- . лями 5 и 52 опрашивается узел 7 тарировки, при этом на его выходе вырабатывается двоичный код в соответствии с выражением

. i

on

-rO

±11 ±21

где выходной .код узла тариров- 50 ки при О- м опросе;

tj - цикл внутреннего опроса; { и S°- входные частоты по данно . му каналу в начальных условиях. Когда производится тарировка;

оп опорная частота. Далее этот код через коммутатор 15 поступает на вход арифметического блока 10, где происходит обработка результатов опросов по внутреннему циклу устройства в соответствии с выражением

р р .N:.--I

-- м .-го го i )-0 31 3-0 . Р.

Результат I Х;. хранится во внут; 3

ренней памяти арифметического блока 10. Другие два канала с входными

3 и 123Р частотами 2 и i, ботают аналогично.

Следует отметить, что для получения высокой точности при ограниченном времени измерения необходимо чтобы разностная частота fp г -{. отличалась от нуля. Особенно неблагоприятен для проведения тарировки случай, если значение fp колеблется около нуля в ту и другую сторону в процессе измерения. В предлагаемом устройстве к датчикам предъявляется требование: ° 7 °,. f f I,. Причем диапазон значений начальной разностной частоты и число периодов и, длительность которых измеряется мри тарировке, выбираются исходя из требу емой точности и допустимого времени измерения. Т.е. узлы тарировки могут обеспечить высокую точность только в более ограниченном диапазоне, чем,весь диапазон входных частот

При правильном выборе значений fp и и измерение начальной разностной частоты в таком устройстве может быть произведено с погрешностью меньшей, чем цена единицы младшего, разряда арифметического блока 10.

Это объясняется тем, что. при предлагаемом методе измерения начальной

разности частот число к° -f°

H-t 2.Н

может быть выбрано больше, чем емкость разрядной сетки блока 10.

Н б/гону 15 От S/iona /J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прялка для изготовления крученой нити | 1920 |

|

SU112A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство для измерителей перемещений | 1975 |

|

SU553620A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-23—Публикация

1981-08-24—Подача