ел

со

00

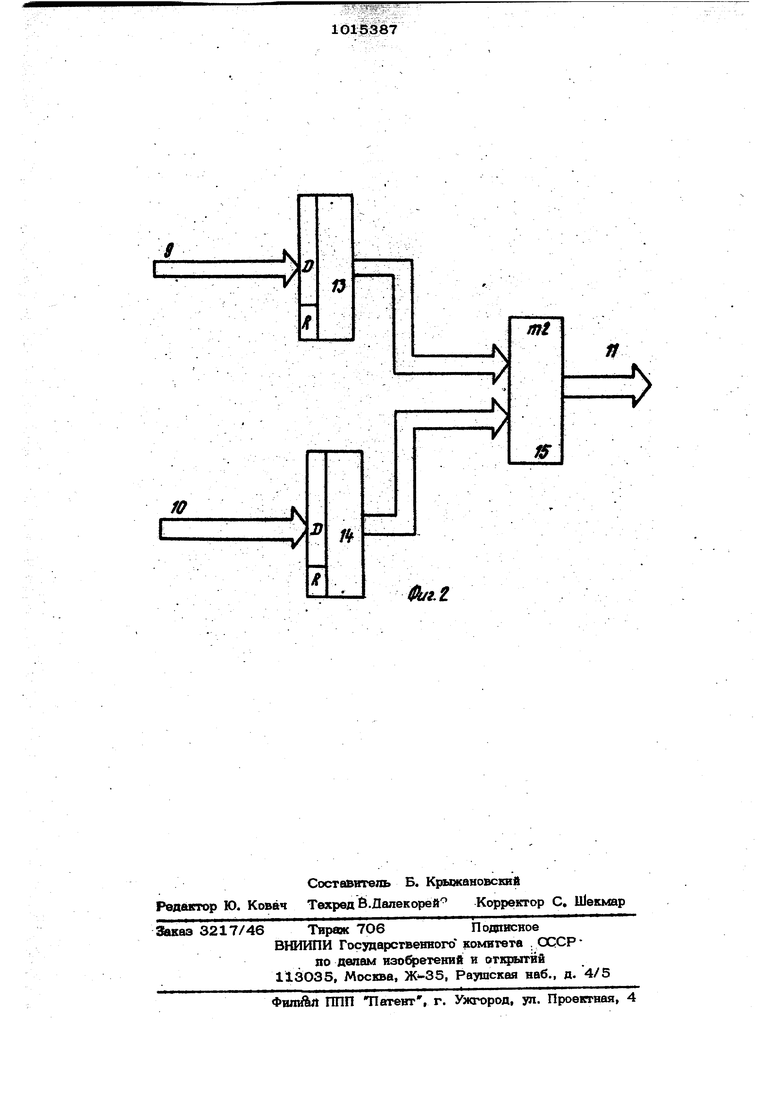

ч| Изобретение относигея к вычислительной технике и может быть использовано для проверки на четность информации, принимаемой в параллельном виде. По основному авт. св. № 88391О иэвесгно устройство для контроля параллельного кода на четность, содержащее группу элементов И, элемент ИЛИ, входы которого соединены с выходами блока элементов И, триггер, счетный Вход которого соединен с выходом элемента ИЛИ, выход триггера является выходом устройства, регистр, единичные выходы каждого разряда которого соединены с первыми входами соответствующих элементов И группы элементов И, элемент И и элемент И-НЕ, причем нулевой выход каждого разряда регистра соединен с одним Из других входов каждого прсле дукщего Ч т.е. по очередности опроса и исключая соответствующий разряду регистра элемент И) элемента И групйы элементов Икс соответствующим входом элемента И-НЕ, выход которого соединен с первым входом элемента И, второй вход которого является входом тактовой частоты, выкод элемента И соединен с управляющими ккодами элементов И группы элементов И, выход каждого элемента И группы элементов И соеди1юн с входом установки в нуль соответствую щего разряда регистра L13 . Недостатком устройства является сравнительно низкое быстродействие, определяемое количеством единиц в конт ролируемом коде.. 6j. NlUP , где Bj - условное быстродействие извес ного устройства; N - количество пачек кодов; L, - количество контролируемых кодов в пачке кодов; Р - количество единиц в конгоолируемом коде. Цель нзофетения - повышение быстро действия устройства. Указанная цепь достигается тем, что в устройство дополнительно введен модификатор кода, группа информационных выходов которого соединена соответствен но с группой единичных разрядных входо регистра, группа информационных входов и группа входов маски модификатора кода являются соответственно одноименныМИ входами устройства. Кроме того, модификатор кода содэржит регистр кода, регистр маски и блок сумматоров по модулю два, причем первая группа входов которого является группой информационных входов модификатора кода, вторая группа входов блока сумматоров по модулю два соединена со ответственно с группой выходов регистра маски, группа входов которого я&ляется группой вкодов маски модификатора кода, группа выходов блока сумматоров по модулю два является гругахой информационных выходов модификатора, кода. Сущность изобретения состоит в модификации контролируемого кода на 4eiv ность путем наложения на него кода маски и в уменьшении тем самым количества единиц в контролируемом коде, при этом первоначальная четность (нёчет ность) контролируемого кода не изменяется. На фиг. 1 изофажена функциональная схема устройства для контроля параллельного кода на четность; на фиг. 2 функциональная схема модификатора кода. Устройство для контроля параллельно1Ч кода на четность содержит модификатор 1 кода, регистр 2, группу 3 элементов И, элемент ИЛИ 4, триггер 5, элемент И-НЕ. 6, элемент И 7; входы 8 10 и выходы 11 и 12. Модификатор 1 кода содержит регистр 13 кода, регистр 14 маски и блок 15 сумматоров по модулю два. Введение регистров 13 и 14 кода и мазки обусловлено необходимостью хранения контролируемого кода и кода маски на время модификации контролируемого кода с помощью блока 15 сумьлаторов по модулю два. Устройство работает следующим образом. В исходном состоянии элементы памяти модификатора 1 кода (регистр 13 кода и регистр 14 маски), регистр 2 и триггер 5 находятся в нулевом состоянии. Одновременно с подачей контролируемого кода на гр}7шу информационных входов 9 устройства и записью его в регистр 13кода на группу входов 1О маски поступает код маски, который записывает- ся в регистр 14 маски. Регистр 13 кода и регистр 14 маски обьгчно имеют одинаковую разрядность, равную постоянной разрядности контролируемого кода и соответствукицей разрядности кода маски. При переменной разрядности контролируемого кода разрядность регистров 13 и 14кода и маски равна максимальной разрядносги контролируемого кода. Та;кую жё разрядность имеет блок 15 сум;маторов по модулю два, каждый элемент Которого представляет собой простейший одноразрядный (т.е. с одним выходом) с двумя родами сумматор модулю два. Поступившие контролируемой код и код маски на блоке 15 сумматоров по модулю два поразрядно суммируются по модулю два.Модифицированный код (резутпьтат суксмы по модутгю два)с яыхода модификатора 1 кода через его выход 11 записывала тся в регистр 2. , Возможен случай, когда будет получен нулевой модифицированный код. Это наиболее удачное (эффективное) исполь зование принципа маскирования. При этом с регистра 2 на все входы элементе И-НЕ 6 поступают сигналы, имеющие уровень логической единицы. На выходе элемента И-НЕ 6 дет сигнал, соответсгвукиций уровню логического нуля, который запирает элемент И 7 .через его первый вход. Тактовые импульсы, посту. пающие на второй вход элемента И 7,. непроходят на grb выход. Таким офазом, с выходов группы 3 элементов И через элемент ИЛИ 4 на вход триггера 5 не поступит ни одного вмпул ьса. Триггер 5 осганется в исходном нулевом состоянии, что соответствует правильному определению четности контролируемого кода. Наибсхлее часто состояние регистра 2 будет отлично от нулевого и на выходе элемента И-НЕ 6 будет сигнал, сог ответствукйдий уровню логической : едвницьт, . который открывает элемент И 7 и paaipemaex прохождение черей него импульсов тактовой частоты для сятроса разрядов репютра 2. Вначапе опрашивается .триггер 2 регистра 2, затем - 2, далее -2. Последним опре шивается триггер 2 р. При этом, если три гер 2v| находился в результате модификации контролируемого кода в состоянии единицы , первый тактовый импульс с выхода элемента И 3 группы 3 элементов И через элемент ИЛИ 4 переключит триггер 5 из состояния нуля в состояние единиць и одновременно с этим переклку {чиг триггер 2 регистра 2 из состояония единицы в состояние нуля. Если.триггер 2 находился э состоянии нуля а триггер 2 „ - в состоянии единицы, то первый тактовый импульс осуществит аналогичные переключения триггера 5 и триггера 2 регистра 2, пройдя соответственно через элемент И 3 и элемент ИЛИ 4. Таким офазом, процесс опроса начинар-рся с того триггера, находящегося в состоянии единицы, который иибет наименьщий индекс 1,2..., Аналогичным образом второй, тфетий и т.д. тактовые импульсы через соответствукшие элементы И группы 3 и элемент ИЛИ 4 переключат последовательно триггер 5 из состояния единицы в состояние нуля, затем - из состояния нуля в состояние единицы и т.д. пока все триггеры 2, 2, ...,2 регистра 2 не установятся в состояние нуля. При нулевом состоянии регистра 2 выходной сигнал элемента И-НЕ 6 запирает элемент И 7, на выход которого прекращают поступать тактовые импульсы; Процессе свертки контролируемого кода рпределения его четности или нечетности) прекращается. Результегт свертки фиксируется триггером 5 и можег быть считан для дальнейшего использования с выхода 12 триггера 5. Быстродействие ( контроля кода Hia четность) узгройства будет гахределять- ,NL(P-T),, где t - количество маскируемых разрядов в контролируемом коде. Очевидно, чГй . при этом втносительиый выигрьш в.быстродействии определяется следующим образом Во NU(P-T) Таким обрезом, модификация контро.лируемого кода путем| маскирования определенных разрядов кода позволяет умень - шить количество единиц в контролируемом коде и тем самым повысить быстродействие устройства и, следовательно, эффективность системы контроля и вычислительной сисутемы в целом.

У

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1084800A2 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля кода на четность | 1988 |

|

SU1529224A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для обнаружения и исправления ошибок в @ -кодах Фибоначчи | 1986 |

|

SU1441400A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

1. УСТРОЙСТВО ДЛЯ КОНТ. РОЛЯ ПАРАЛЛЕЛЬНСШ КОДА НА ЧЕТНОСТЬ по. 9ВТ. св. № 883910, о т л и чающееся тем, что, с целью повышения быстродейспжия, оно содержит модификатор кода, группа информационных выходов которого соединена соответственно с группой еданичных разрядных BICO дов регистра, группа информационных входов и группа входов маски модификатора ..кода являются соответст1венно одноименными входш ш устро{1сгтва. 2. Устройство по п. 1, о т п и ч а ю ш е е с. я тем, что модификатор ко-, да содержит регистр кода, регистр маски и блок сумматоров по модулю два, привем перВЕЩ группа входов которого является группой информационных входов модификатора кода, вторая группа входов блока сумматора по модулю два соединена соответственно с группой выходов регистра маски, группа входов котсн рого является группой входов маски модификатора кода, группа выходов блока сумматора по модутпо два является групШ)й информационных выходов модифика(Л тора кода.

/

ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для определения вязкости глины и подобных ей материалов | 1949 |

|

SU88391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-30—Публикация

1981-12-05—Подача