СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

| Отказоустойчивое устройство для умножения чисел | 1990 |

|

SU1777134A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

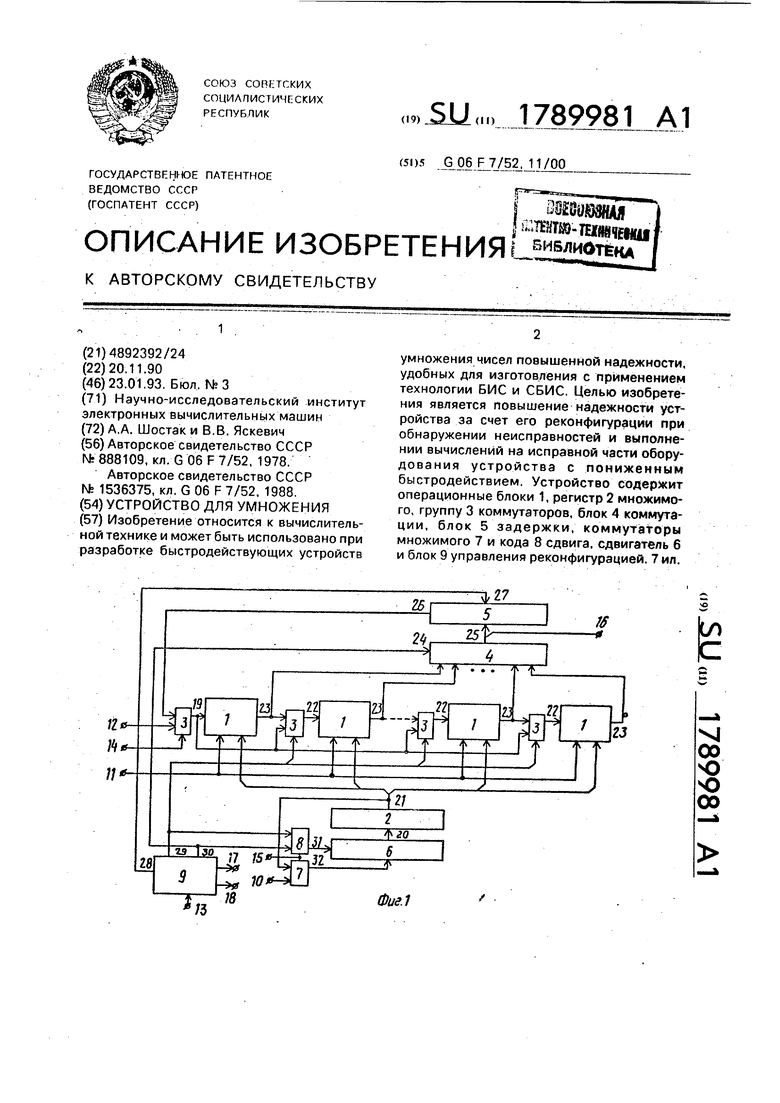

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения чисел повышенной надежности, удобных для изготовления с применением технологии БИС и СБИС. Целью изобретения является повышение надежности устройства за счет его реконфигурации при обнаружении неисправностей и выполнении вычислений на исправной части обору- дования устройства с пониженным быстродействием. Устройство содержит операционные блоки 1, регистр 2 множимого, группу 3 коммутаторов, блок 4 коммутации, блок 5 задержки, коммутаторы множимого 7 и кода 8 сдвига, сдвигатель 6 и блок 9 управления реконфигурацией. 7 ил.

VI 00 О О 00

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств умножения чисел повышенной надежности, удобных для изготовления с применением технологии больших и сверхбольших интегральных схем (БИС и СБИС). ;

Известно устройство умножения, содержащее регистр множимого и п операционных блоков (п - разрядность множимого),. каждый из торых включает узел вычисления . Значений произведения и два буфёрй||х р втистра с соответствующими СВЯЗЯМИ, . ;;..,...

Данное устройство отличается достаточно высоким быстродействием. Недостатком его является низкая надежность.

Наиболее близким по технической сущности к предполагаемому изобретению является устройство умножения, содержащее п операционных блоков (п - разрядность множимого), регистр множимого, блок задержки и коммутатор, причем вход множимого j-ro операционного блока (,.,.,n-1) соединен с выходом 1-го разряда регистра множимого, вход слагаемого - с выходом (i-йj-ro .операционного блока, вход слагаемого п-го операционного блока соединен с выходом коммутатора, первый информационный вход которого подключен к входу кор- рекции устройства, выход результата которого соединен с выходом первого операционного блока и информационным входом блока задержки, выход которого. соединен с вторым информационным входом коммутатора, вход регистра множимого подключён к входу множимого устройства, первый и второй управляющие входы которого соединены соответственно с управляющими входами коммутатора и блока задержки, вход множителя устройства соединен с входами множителя п операционных блОКО В. : :- - -- -

Известное устройство удобно для изготовления с применением БИС и СБИС, отличается достаточно высоким быстродействием. Недо- этого, как и предыдущего устройства является его низкая надежность.

Целью изобретения является повыше- ние надежности устройства за счет его реконфигурации в случае неисправности- операционных блоков и выполнения вычислений на исправной части оборудования устройства с пониженным быстродействием.

Поставленная цель достигается тем, что в устройство умножения, содержащее п операционных блоков (п-разрядность множимого), регистр множимого, блок задержки и первый коммутатор, управляющий вход которого соединен с первым управляющим

входом устройства, вход множителя которого соединен с входами множителя п операционных блоков, входы множимого которых соединены с выходами соответствующих

разрядов регистра множимого, первый и второй информационные входы первого коммутатора соединены соответственно с входом коррекции устройства и выходом блока задержки, а выход - с входом слагае0 мого п-го операционного блока, дополнительно содержит (п-1) коммутаторов, блок коммутации, сдвигатель, коммутаторы множимого и кода сдвига и блок управления реконфигурацией, причем вход слагаемого

5 1-го операционного блока ,...,п-1) соединен с выходом (n-i+1)-ro коммутатора,.первый информационный вход которого соединен с выходом первого коммутатора, управляющий вход блока задержки соеди0 нен с первым выходом блока управления реконфигурацией, второй выход которого соединен с управляющим входом k-ro коммутатора (,...,n) и первым информацион- . ным входом коммутатора кода сдвига,

5 выход которого соединен с управляющим входом сдвигателя, информационный вход которого соединен с выходом коммутатора множимого, первый информационный вход которого соединен с входом множимого ус0. тройства, второй управляющий вход которого соединен с управляющими входами коммутаторов множимого и кода сдвига, выход сдвигателя соединен с входом регистра множимого, выход которого соединен с вто5 рым информационным входом коммутатора множимого, выход го операционного блока соединен с вторым информационным входом (n-k+2)-ro коммутатора и k-м информационным входом блоки коммутации, пэр0 вый информационный зход которого соединен с выходом первого сперацисино- . го блока, а выход - с информационным входом блока задержки и выходом результата устройства, вход контроля которого соеди5 нен с входом блока управления реконфигурацией, третий выход которого соединен с управляющим входом блока коммутации и вторым информационным входом коммута- Ttrpa кода сдвига, четвертый и пятый выходы

0 блока управления реконфигурацией соединены соответственно с выходами отказа и прерывания устройства.

Устройство умножения содержит отличительные признаки, не обнаруженные ни в

5 одном из известных аналогичных устройств - оно содержит группу коммутаторов, блок коммутации, сдвигатель, коммутаторы множимого и кода сдвига и блок управления реконфигурацией с соответствующими связями. Это позволяет обеспечить работу устройства при отказах операционных блоков за счет реконфигурации и продолжения вычислений на исправной части оборудования устройства с пониженным быстродействием. Устройство работоспособно до logan отказов операционных блоков.

Таким образом, так как в устройстве имеются отличительные признаки, обеспечивающие достижение поставленной цели и не известные ни в одном другом аналогичном техническом решении, то оно соответствует критерию существенные отличия.

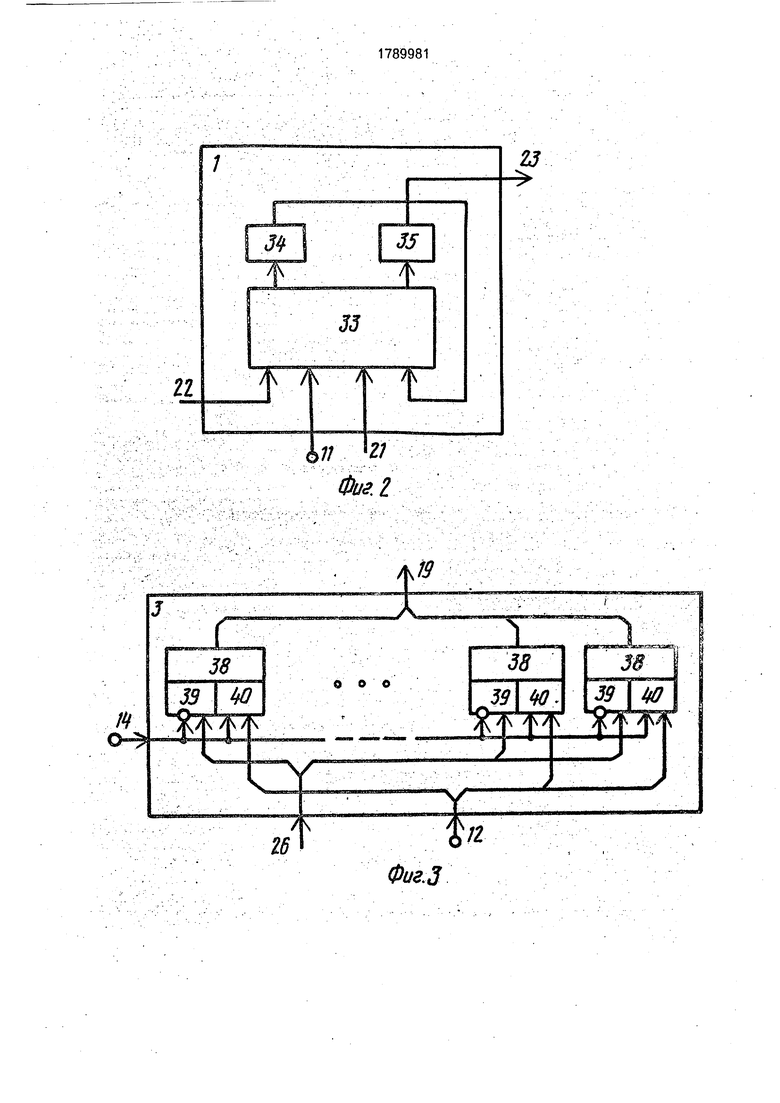

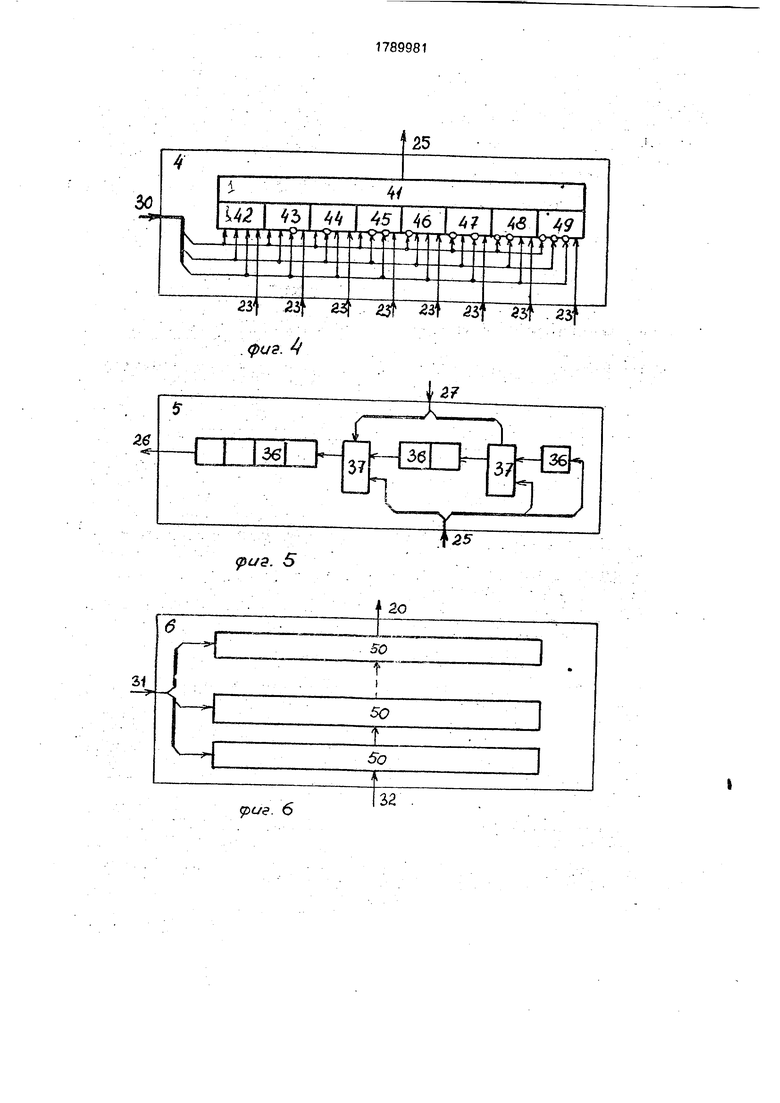

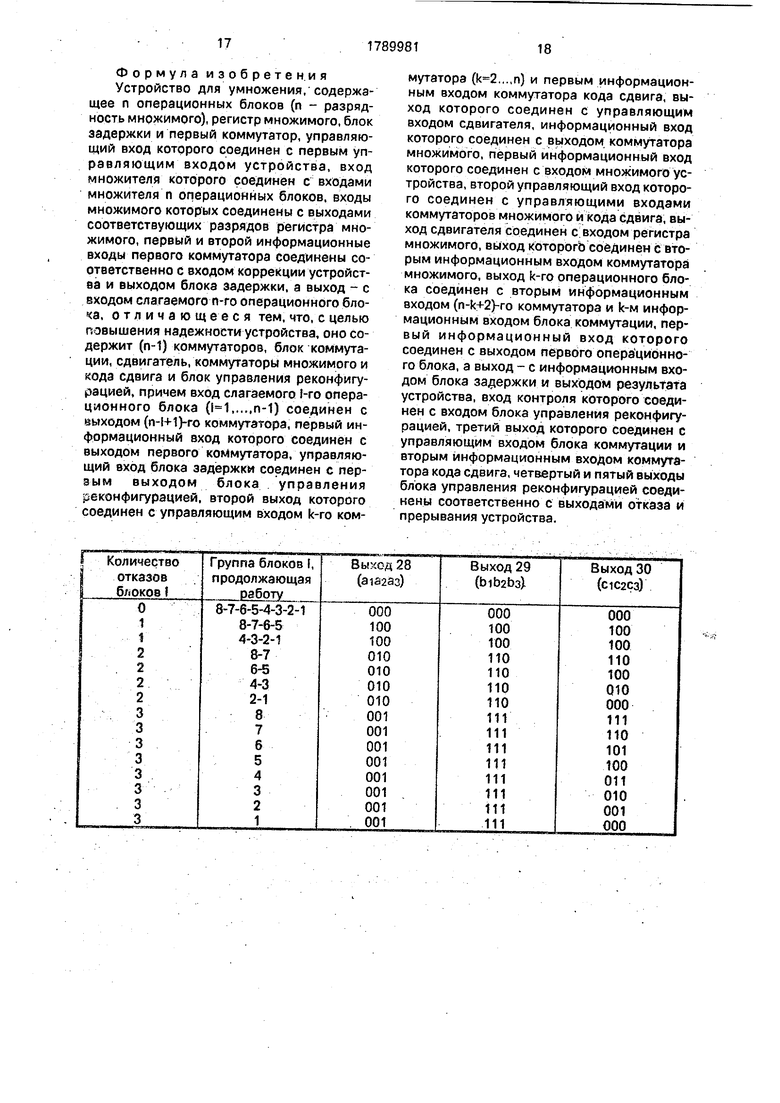

На фиг. 1 приведена структурная схема устройства умножения; на фиг. 2 - структурная схема операционного блока; на фиг. 3 - функциональная схема коммутатора группы (такую же функциональную схему имеют коммутаторы множимого и кОда сдвига); на фиг. 4 - функциональная схема блока коммутации при на фиг, 5 - структурная схема блока задержки при на фиг. 6 - структурная схема сдвигателя; на фиг. 7 - функциональная схема блока управления реконфигурацией.

Устройство умножения (фиг. 1) содержит п операционных блоков 1 (п-разряд- носТь множимого), регистр 2 множимого, п коммутаторов 3, блок 4 коммутации, блок 5 задержки, сдвигатель 6, коммутатор 7 множимого, коммутатор 8 кода сдвига, блок 9 управления реконфигурацией, входы 10 и 11 множимого и множителя устройства соответственно, входы 12 и 13 коррекции и контроля устройства соответственно, первый 14 и второй 15 управляющие входы устройства, выход 16 результата устройства, выходы 17 и 18 отказа и прерывания устройства соответственно. Входы множителя блоков 1 соединены с входом 11 устройства, вход 10 множимого которого соединен с первым информационным входом коммутатора 7, второй информационный вход которого соединен с входами множимого блоков 1 и выходом 21 регистра 2, вход которого соединен с выходом 20 сдвигателя 6, информационный вход которого соединен с выходом 32 коммутатора 7, вход слагаемого i-ro блока 1 (,...,n-1) соединен с выходом 22 (п-1+1)-го коммутатора 3, первый информационный вход которого соединен с входом слагаемого п-го блока 1 и выходом 19 первого коммутатора 3, первый информационный вход которого соединен с выходом 26 блока 5, управляющий вход 27 которого соединен с выходом 28 блока 9, выход 29 которого соеди-. нен с управляющим входом k-ro коммутатора 3 (,...,n) и первым информационным вхо дом коммутатора 8, выход 31 которого соединен с управляющим входом сдвигателя 6,информационный вход блока 5 соединен

с выходом 25 блока 4 и выходом 16 результата устройства, вход 13 контроля которого соединен с входом блока 9, выход 30 которого соединен с вторым информационным 5 входом коммутатора 8 и управляющим входом 24 блока 4, k-й информационный вход которого соединен с выходом 23 k-ro блока 1 и вторым информационным входом (п- k+2)-ro коммутатора 3, вход 12 коррекции

0 устройства соединен с вторым информационным входом первого коммутатора 3, управляющий вход которого соединен с первым управляющим входом 14 устройства, второй управляющий вход 15 которого

5 соединен с управляющими входами коммутаторов 7 и 8, четвертый и пятый выходы блока 9 являются выходами 17 отказа и 18 прерывания устройства соответственно, выход первого операционного блоха соединен

0 с первым информационным входом блока 4. Рассмотрим функциональное назначение и реализацию отдельных узлов и блоков устройства.

Операционные блоки 1 предназначены

5 для вычисления разрядных значений произведения и формируют на своих выходах 23 значения

/X Y+A+B/мл, где / /мл означает младший разряд двух0 разрядного результата;

X, Y - соответствующие разряды сомно-, жителей, поступающие на входы множителя и множимого блоков 1;

А - одноразрядное слагаемое, поступа5 ющее на вход слагаемого блоков 1;

В - внутреннее одноразрядное слагаемое, хранимое в одном из буферных регистров блоков 1.

Реализация блоков 1 показана на фиг. 2,

0 В этом случае каждый блок 1 содержит узел 33 вычисления разрядных значений произведения и буферные регистры 34 и ЗбС Узел 33 формирует двухразрядные значения функции F X. Y+A+B, ...

5 старший и младший разряды которых записываются соответственно в регистры 34,35. Реализация узла 33 зависит от требований к регулярности структуры и к быстродейст-. вию. Регистры 34, 35 могут быть реализова0 ны на синхронных двухтактных D-триггерах с цепями установки в нулевое состояние.

Регистр 2 множимого предназначен для хранения п-разрядного значения множимого и может быть реализован на синхронных

5 двухтактных D-триггерах.

Коммутаторы 3 группы предназначены для выдачи информации на свои выходы 22(19} (входы слагаемых блоков 1) с первого или второго своих информационных входов в зависимости от управляющих сигналов.

Они могут быть реализованы на элементах 2 ИЛИ 38 и 2 И 39 и 40, как это показано на

Фиг. з. -;, . . .:

Блок 4 коммутации предназначен для подключения выходов 23 блоков 1 к инфор- мацйонному входу блока 5 задержки- при работе устройства в режиме с пониженным быстродействием. В зависимости от сигнала на управляющем входе 24 блока 4 на его выход 25 передается информация с одного из его информационных входов (выхода 23 блока 1). Для случая реализация блока 4 показана на фиг. 4, при этом он содержит в осемь групп 42-49 элементов И и одну группу 41 элементов ИЛИ.

Блок 5 пр ёдййз йёчёи для хранения раз- рйДЬв 1сумм частичных произведений, формируемых при работе устройства с пониженным быстродействием после отка- зоё блоков 1 /и реконфигурации структуры устройства. В зависимбсти ы сигналов на управляющем входе 26 блока 5, он может быть настроен на различную величину задержки прохождения сигнала с его инфбр- .м ацибнных входов к его выходу 26. Ё ел йчШа задержки при количестве блоков

.- -,- - -- - f -,-.--, . .- - ... ... 1 (, 2,3,...) равна 2 п/2а, ,

. а - 1 : . 2, ..., m - количество отказавших блоков 1 устройства,Реализация блока 5 может быть различной. На фиг, 5 показана реализация блока 5 для случая . В этом случае блок 5 содержит три регистра 36 и два коммутатора 3.7, причем первый регистр 36 - п/2- разрядный (в рассматриваемом случае 4-разрядный), второй регистр 36 - п/4-разрядны и (в рассматриваемом случае 2-разрядный) м третий регистр 36 - п/8-разрядный (в рассматриваемом случае одноразрядный). Подавая управляющие сигналы на коммутаторы 37 можно образовать цепь регистров разрядностью п/2 или n/2+n/4-3n/4 или n/2+n/4+n/8 7n/8. Регистры 36 блока 5 могут быть реализованы на синхронных двухтактных D-триггерах. Ком- мутаторы 37, передающие информацию на входы соотёетствующих регистров Зб с первого или второго своих информационных входов могут быть реализованы на элемен- тах 2И-2ИЛИ аналогично показанному на фиг. 3 коммутатору 3.

Сдвигатель 6 предназначен для сдвига информации на величину, определяемую кодбм на его управляющем входе. Он вы- полняет циклический сдвиг влево информации, поступающей на его информационный вход и может быть реализован как показано на фиг. 6. В этом случае он содержит m коммутаторов 50, реализованных аналогично показанному на фиг. 3 коммутатору 3, причем первый (младший) разряд кода на управляющем входе сдвигателя 6 настраивает первый коммутатор 50 на сдвиг 0-1 разряд, второй разряд кода настраивает второй коммутатор 50 на сдвиг 0-2 разрядов, а m-й разряд кода - т-й коммутатор 50 на сдвиг разрядов. Таким образом, сдвигатель б под управлением кода подаваемого на его управляющий вход, может быть настроен на сдвиг множимого на любое число разрядов.

Коммутатор 7 предназначен для передачи на свой выход 32 (информационный вход сдвигателя 6) информации с первого или второго своих информационных входов (входа 10 множимого устройства или выхода 21 регистра 2 множимого) в зависимости от управляющего сигнала на входе 15 устройства. Он может быть реализован на элементах 2И-2ИЛИ аналогично показанному на фиг. З коммутатору 3,

Коммутатор 8 предназначен для передачи кода сдвига на управляющий вход сдвигателя 6 (выход 31 коммутатора 8) с второго 29 или третьего 30 выходов блока 9 в зависимости от управляющего сигнала на вход 15 устройства. Он может быть реализован на элементах 2И-2ИЛИ, как показано на фиг. 3 для коммутатора 3.

Блок 9 управления реконфигурацией предназначен для выдачи управляющих Сигналов на прерывание работы устройства при отказах операционных блоков 1. на выбор работоспособной группы блоков 1 и организацию ее связи с блоком 5 задержки, на выбор необходимой величины задержки в блоке 5, на установку начального и текущего кодов сдвига множимого при его записи в регистр 2, а также для выдачи сигнала об отказе устройства после т+1 отказов блоков 1. Одна из возможных реализаций блока 9 для устройства с количеством блоков 1 (, 2, 3...) показана на фиг. 7. Блок 9 содержит (п-1) элементов ИЛИ 51, образующих m-ступенчатую пирамиду, т-1 элементов ИЛИ 52, счетчик 53, дешифратор 54, элементов И 55, m RS-триггеров 56 первой группы и m RS-триггеров 57 второй группы. С помощью элементов ИЛИ 5.1 и 52 определяется местоположение отказавших блоков 1 в структуре устройства. Сигнал об отказе одного из блоков 1 через элементы ИЛИ 51 поступает на счетный вход счетчика 53, устанавливая его в очередное состояние и на пятый выход блока 9 (выход 18 устройства), вызывая прерывание работы устройства. После f отказов на f-м выходе дешифратора 54 формируется Г, которая поступает на первый вход f-ro элемента И

55, разрешая прохождение информации с (М)-го элемента ИЛИ 52 (для первого элемента И 55 - с выхода второго элемента ИЛИ 51 предпоследней ступени пирамиды), определяемой наличием отказавшего блока 1 в той или иной части оборудования устройства.

Таким образом на выходе 28 блока 9 после f-ro отказа во всех разрядах, кроме f-ro, будут О, а в f-м разряде 1 (этот сигнал используется для настройки блока 5 задержки), на выходе 29 блока 9 в разрядах с первого по f-й будут 1, а в остальных разрядах - О (эти сигналы настраивают коммутаторы 3 на организации в устройстве групп по п/2 блоков 1, а также определяют величину текущего сдвига множимого после каждого цикла работы устройства), на выходе 30 блока 9 устанавливается информация, определяющая работоспособную группу блоков 1 (сигналы настраивают блок 4 коммутации на организацию связи между работоспособной группой блоков 1 и блоком 5 задержки, а также определяют величину начального сдвига множимого).

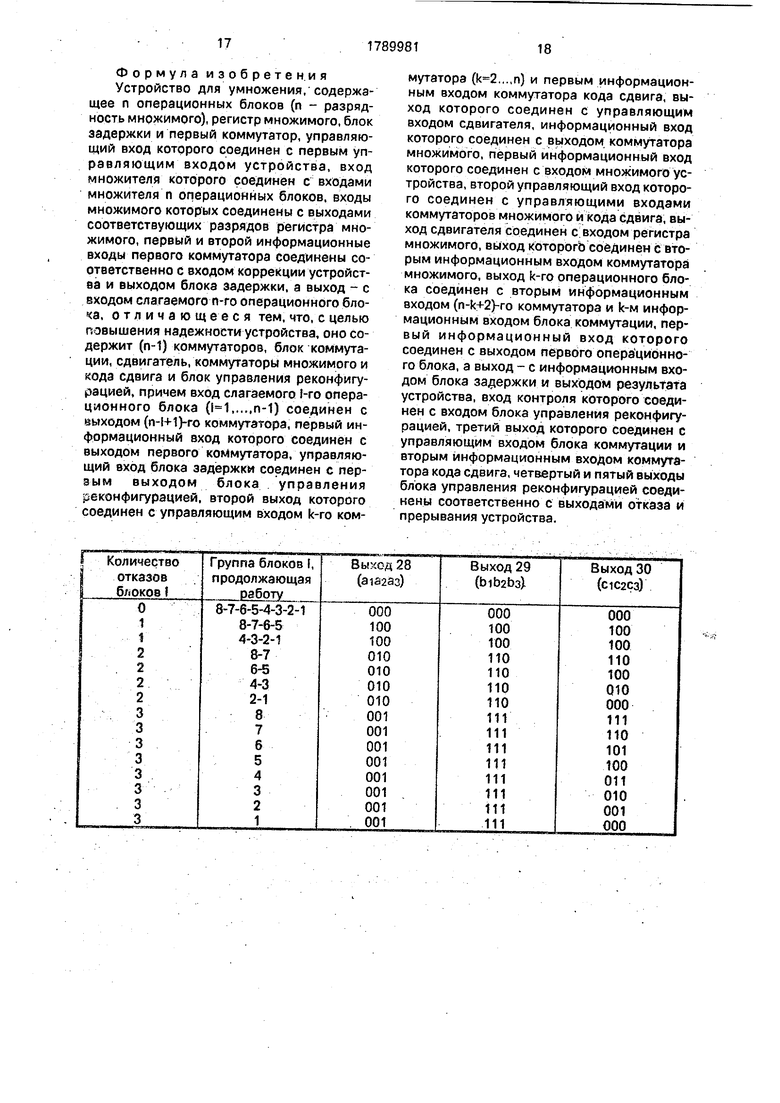

В таблице приведены значения информации на выходах 28-30 блока 9 в случае использования в устройстве восьми блоков 1 (, ).

Как видно из таблицы, на выходе 28 блока 9 значение 1 присутствует в разряде, номер которого соответствует количеству отказов блоков 1 (после одного отказа блока 1 присутствует 1 в разряде ai, после двух отказов - в разряде 32 и т.д.), причем сигнал с каждого разряда выхода 28 управляет соотвек вующим коммутатором 37 блока 5 (сигнал с разряда ai управляет первым коммутатором 37 блока 5, сигнал с аз - вторым коммутатором 37 блока 5), настраивая его на определенную задержку.

На выходе 29 блока 9 значение 1 присутствует в разрядах, номер которых меньше или равен количеству отказов блоков 1 (после одного отказа блока 1 - в разряде ai, после двух отказов блоков 1 - в разрядах Ьи и D2, после трех отказов блоков 1 - в разрядах bi, О2 и Ьз), причем сигнал с каждого разряда выхода 29 блока 9-управляет определенными коммутаторами 3 (сигнал с разряда bi управляет h/2-м коммутатором 3, сигнал с Ь2-п/4-м и Зп/4-м коммутаторами 3, сигнал с Ьз-п/8-м, Зп/8-м, 5п/8-м и 7п/8-м коммутаторами 3), а кроме того, информация на выходе 29 блока 9 определяет значение текущего сдвига множимого после каждого цикла работы устройства (после одного отказа блоков 1 устанавливается значение сдвига в 1002-4 разряда, после двух отказов блоков 1 - значение сдвига 1102-6

разрядов, после трех отказов блоков 1 - значение сдвига II( разрядов).

На выходе 30 блока 9 устанавливается информация, определяющая работоспособ- 5 ную группу блоков 1, продолжающих функционирование после восстановления работоспособности устройства. Так, после одного отказа блоков 1 могут быть образованы две группы блоков i, поэтому выраба0 тываются два варианта кода на выходе 30 блока 9, причем код 100 определяет работоспособную группу блоков 1 в виде 8-7-6-5 и поступает на управляющий вход 24 блока 4, разрешая прохождение информации с вы5 хода 23 пятого блока 1 через группы элементов И 45 и ИЛ И 41 на информационный вход блока 5 задержки, кроме того - этот код определяет величину начального сдвига множимого в разряда. Код 000 на

0 выходе 30 блока 9 устанавливает работоспособную группу блоков 1 в виде 4-3-2-1 и поступает на управляющий вход 24 блока 4, разрешая прохождение информации с выхода 23 первого блока 1 через группы эле5 ментов И 49 и ИЛИ 41 на информационый вход блока 5 задержки, кроме того, код 000 определяет величину начального сдвига в разрядов. После двух отказов блоков 1 в устройстве образуются четыре группы по

0 два блока 1 в каждой и значение кода на выходе 30 блока 9 определяет одну из них. например, группу4-3 определяет кодОЮ на выходе 30 блока 9, который настраивает блок 4 на передачу информации с выхода 23

5 третьего блока 1 на информационный вход блока 5 задержки, а также определяет величину начального сдвига множимого в разряда. В остальных случаях блок 9 работает аналогично.

0На структурных и функциональных схемах с целью упрощения услб вно не показаны цепи установки в нулевое состояние регистров 34 и 35 блоков 1, триггеров 56 и 57 первой и второй Трупп и счетчика 53 ка 9, а также цепи синхронизации регистра 2 множимого, регистров 34 и 35 блоков 1 и регистров 36 блока 5, однако, можно отметить, что имеется общая цепь синхронизации регистров 34, 35 блоков 1 и регистров

0 36 блока 5 (сигналы подаются в конце каждого такта работы устройства), цепь синхронизации регистра 2 множимого (сигнал подается перед началом работы устройства и в конце каждого цикла его работы), общая

5 цепь установки в нулевое состояние регистров 34, 35 блоков 1 (сигнал подается перед началом любого из режимов работы устройства) и общая цепь установки в нулевое Состояние триггеров 56,57 и счетчика 53 блока 9 (сигнал подается перед началом ислользой

вания устройства при всех исправных блоках I)/ .

Устройство работает следующим образом. .

В исходном :состоянми регистры 34 и 35 блоков 1, триггеры 56 и 57 блока 9 обнулены. На вход 15 устройства подан сигнал, настраивающий коммутаторы 7 и 8 на передачу информации соответственно с входа 10 устройства на информационный вход сдвигате- ля б и с выхода 30 блока 9 на управляющий вход сдвйгателя 6. Под управлением нулево го кода на выходе 30 блока 9 (управляющем входе сдвигателя 6) в регистр 2 с входа устройства записывается без сдвига п-разряд- ное .значегже множимого. По окончании 3a.ii.Wcw множимого на вход 15 устройства поДа ется сигнал, настраивающий коммутатор 7 и 8 на передачу информации с их : других информационных входов, Под управлением нулевого кода на выходе 29 блока 9 коммутаторы 3 настроены на организацию связей между соседними блоками 1 „На вход 14 устройства подан сигнал/настраивающий первый коммутатор 3 на передачу информации с входа 12 коррекции устройства на вход слагаемого п-го блока 1.

Работу устройства будем рассматривать для случая (,2,...) в следующих режимах: рабочий режим; режим реконфигурации; рабочий режим с пониженным быстродействием. .

РАБОЧИЙ РЕЖИМ. В рабочем режиме в устройстве производится умножение п- разрядных сомножителей в течение 2.п тактов с использованием п операционных блоков 1 (все блоки 1 исправны). В каждом из п первых тактов работы устройства на его вход 11 поступает по одному разряду, начиная с младших,, множитель. При этом в J-M блоке 1 ,..... п) производится умножение j-ro разряда множимого, поступающего на его вход множимого с j-ro разряда выхода 21 регистра 2, на разряд множителя, поступающий на его вход множителя с входа 11 устройства и прибавление к младшему разряду получившегося при этом произведения t младшего разряда произведения (j-M)-ro блрка 1, сформированного в предыдущем такте и поступающего на вход слагаемого j-ro блока 1 с выхода 22 j-ro коммутатора 3, а также старшего разряда произведения j-ro блока 1, сформированного в предыдущем такте и хранимого в его регистре 34. Сформированные к концу такта старший и младший разряды произведения j-ro блока 1 записываются в его регистры 34 и 35 соответственно.

. После выполнения п первых тактов работы устройства на его вход 11 подается

нулевая информация и далее осуществляется еще дополнительно п тактов, в течение которых из устройства выводится с соответствующим преобразованием информация,

хранимая в регистрах 34 и 35 блоков 1. Следует отметить, что вывод 2п-разрядного произведения сомножителей в устройстве осуществляется через его выход 1 & по одному разряду в каждом такте..

0 В рассмотренном случае на вход 12 коррекции устройства во всех тактах подается нулевая информация. В тех же случаях, когда требуется получить округленное произведение, необходимо в первом цикле

5 работы устройства на его вход 12 подать корректирующую информацию (для округления 2п-разрядного произведения п-раз- рядных сомножителей, представленных в двоично-кодированной шестнадцатеричной

0 системе счисления необходимо подать в первом такте работы на вход 12 двоичный код 1000). Это позволяет осуществить округление результата без дополнительных временных затрат, Кроме того, вход 12 может

5 быть использован также для введения результирующей коррекции по знакам множимого и множителя в случае умножения чисел в дополнительном коде.

РЕЖИМ РЕКОНФИГУРАЦИИ. В про0 цессе функционирования блоки 1 могут отказывать. Будем предполагать, что каждый операционный блок 1 имеет средства обнаружения отказа в виде средств встроенного контроля, которые могут быть организованы

5 любыми известными способами, например дублированием или контролем по модулю. Информация о состоянии блоков 1 поступает на вход 13 устройства в момент опроса средств контроля блоков 1, периодичность

0 которого определяется различными требованиями к работе устройства. Ввиду малой вероятности одновременного отказа двух и более блоков 1, эту ситуацию рассматривать не будем.

5 Сигнал об отказе j-ro блока 1, вырабатываемый средствами встроенного контроля и поступающий на вход 13 устройства, через элементы ИЛИ 51 блока 9 и его пятый выход, поступает на выход 18 устройства, вызывая

0 прерывание работы и перевод устройства в режим реконфигурации. Этим же сигналом счетчик 53 переключается в состояние 1, устанавливая 1 на первом выходе дешифратора 54, которая (поступает на первый раз5 ряд выхода 28 блока 9, устанавливает в Г первый триггер 56 первой группы и поступает на первый вход первого элемента И 55. В случае, если n/2+1 j п, то с выхода второго элемента ИЛИ 51 предпоследней ступени пирамиды на второй вход первого

элемента И 55 поступает 1й и первый триггер 57 второй группы устанавливается в 1й, которая поступает на первый разряд выхода 30 блока 9 (если же 1 j п/2, то первый триггер 57 останется в нулевом состоянии). Таким образом, на выходах блока 9 устанавливается следующая информация: 1 в первых разрядах первого 28,-второго 29 и третьего 30(если n/2+1 ) выходов, под управлением которых в устройстве формируется новая рабочая конфигурация. Сигналом с выхода 28 блока 9 в блоке 5 первый коммутатор 37 настраивается на передачу информации с информационного входа блока 5 на вход первого регистра 36 (формируется цель n/2-разрядного регистра с задержкой распространения от входа к выходу блока 5 равной п/2 тактов). Сигнал с выхода 30 блока 9, определяющий работоспособную часть оборудования (при 1 j п/2 работоспособными считаются блоки 1 с (п/2+1)-го по n-й наоборот), поступает на управляющий еход 24 блока 4 коммутации, который настраивается на передачу информации с выхода 23 или первого или (п/2+1)- го блока 1. Кроме того, этот сигнал поступает на второй информационный вход коммутатора 8 и при подаче соответствующего сигнала на вход 15 устройства с его входа 10 через сдвигатель 6 е регистр 2 записывается множимое циклически сдвинутое влево на п/2 разрядов (при 1 j л/2) Зд1и без сдвига (при n/2+1 j n).

Сигнал с выхода 29 блока 9 настраивает (п/2+1)-й коммутатор 3 на передачу информации с выхода 19 первого коммутатора 3 на вход слагаемого ri/2-ro блока 1, а также йоступа-зт на первый информационный эход коммутатора 8, определяя код сдвига множимого на п/2 разрядов, который используется при перезаписи содержимого регистра 2 множимого по окончании каждого цикла работы устройства в третьем режиме.

Таким образом, под управлением блока 9 в устройстве в зависимости от местонахождения отказавшего блока 1 формируются одна из двух возможных конфигураций для продолжения вычислений. При отказавшем блока 1 с 1 j п/2 включаются в работу блоки 1 с (п/2+1)-го по п-й, выход 23 (п/2+1)-го блока 1 соединяются с информационным входом блока 5, который настраивается на задержку в п/2 тактов, в регистр 2 при этом загружается с входа 10 устройства множимое, циклически сдвинутое влево на п/2 разрядов. Если же отказал блок 1 с п/2+1 : j п, то в работу включаются с первого по n/2-й блоки 1. причем выход 23 первого блока 1 соединяется с информационным входом блока 5, а вход слагаемого п/2-го блока 1 подключается к выходу 19 первого коммутатора 3, в регистр 2 записывается с входа 10 устройства множимое без

5 сдвига.. .

По окончании режима реконфигурации,

одновременно с записью со сдвигом или без

сдвига множимого с входа 10 устройства в

регистр 2 (при соответствующей настройке

0 коммутатора 7 и 8) производится обнуление регистров 34, 35 блоков 1. После этого подают управляющий потенциал на вход 15 устройства, настраивая коммутаторы 7 и 8 на передачу информации с их других информа5 ционных входов. Устройство переходит в режим работы с пониженным быстродействием.

РАБОЧИЙ РЕЖИМ С ПОНИЖЕННЫМ БЫСТРОДЕЙСТВИЕМ. Этот режим харак0 теризуется тем, что умножение п-разрядных сомножителей производится за большее количество тактов, чем при использовании всех имеющихся операционных блоков 1. Так, в случае, когда количество операцибн5 ных блоков 1 в устройстве при фиксации f отказов (, .,., m) блоков 1 произведение n-разрядных сомножителей аычисляется за 2 циклов, каждый из котоQ рых состоит из (п+ -р) тактов, используя

п/2 операционных блоков 1 (при одном отказе -п/2 блоков 1, при двух отказах - п/4 блоков 1 и т.д.). В каждом цикле осуществляется вычисление частичного проиэведе5 ния n-разрядного множителя на n/2f разрядов множимого и подсуммирование к нему сумм частичных произведений, сформированной в предыдущем цикле и хранимой в регистрах 36 блока 5 (старшие

0 разряды) в регистрах 35 блоков 1 (младшие разряды). В итоге получается новая сумма частичных произведений. Блок 5 настраива

ется на задержку в (п- -) тактов.

Т

Пусть после отказа 1 с 1 j п/2 в устройстве образована новая конфигурация, в которой работоспособной является группа блоков 1 с (п/2+1)-го по n-й, причем

выход 23 (n/2+l ro блока 1 через блок 4 коммутации подключён к информационному входу блока 5, настроенного на задержку в п/2 тактов, а вход слагаемого n-го блока 1 через первый коммутатор 3 подключен к выХ°ДУ 26 блока 5. Умножение п-разрядных сомножителей в устройстве выполняется за два цикла по (п+п/2) тактов каждый.

В первом цикле работы устройства вычисляется частичное произведение п/2 младших разрядов множимого, которое хранится в регистре 2 циклически сдвинутым влево на п/2 разрядов, на n-разрядный множитель, который поступает в течение первых п тактов первого цикла по одному разряду, начиная с младших, на вход 11 устройства. Работа блоков 1 аналогична рассмотренному выше основному режиму. Отличие состоит в том, что по окончании каждого такта с выхода 23 (п/2-И)-го блока 1 в первый регистр 36 блока 5 записывается очередной разряд частичного произведения (запись первого разряда частичного произведения производится во втором такте первого цикла, т.к. в первом такте этот разряд записывается в регистр 35 (п/2+1Н° блока 1), В (п/2+2)-м такте первого цикла первый разряд частичного произведения с выхода 26 блока 5 поступает на первый информационный вход первого коммутатора 3, однако на :вход слагаемого п-го блока 1 не прохо- дит, как и последующие (п/2-1) разрядов частичного произведения (что достигается подачей соответствующего сигнала на вход 14 устройства), поскольку младшие п/2 разрядов частичного произведения являются разрядами окончательного результата и в последующих вычислениях не участвуют.

По окончании (п-Н)-го такта первого цикла на вход 14 устройства подается сигнал, разрешающий прохождение информа- ции с выхода 26 блока 5 на вход слагаемого п-го блока 1 и одновременно с записью в последующих п/2-1 тактах первого цикла в первый регистр 3.6. блока 5 старших п/2 разрядов частичного произведения, через вход слагаемого п-го блока 1 осуществляется запись п/2 младших разрядов этого прбизве- дения в регистры 35 блоков 1.

В последнем такте цикла содержимое регистра 2 с помощью коммутатора 7 и сдви- гателя 6 циклически сдвигается влево на п/2 разрядов под управлением кода на выходе 29 блока 9, так что на входы множимого участвующих в работе блоков 1 поступают старшие п/2 разрядов множимого.

Во втором цикле работы устройства вычисляется частичное произведение множителя на п/2 старших разрядов множимого и подсуммирбванйе К нему п старших разрядов частичного произведения, сформиро- ванногбв первом цикле (п/2 разрядов частичного произведения первого цикла хранятся в регистрах 35 блоков 1, а п/2 разрядов постугШют на вход Слагаемого п-го блока 1 в каждом из п/2 первых тактах вто- рого цикла из блока 5).

Как в первом, так и во втором циклах в течение их первых п тактов на вход 11 устройства ттступает по одному разряду, начиная с младших, множитель, а в течение последних п/2 тактов циклов- нулевая информация.:- : .

Следует отметить, что вывод 2п-разряд- ного .произведения сомножителей осуществляется через выход 16 устройства в первые п/2 тактов первого цикла (младшие п/2 разрядов произведения) и в каждом такте второго цикла (старшие п+п/2 разрядов произведения).

При возникновении второго отказа среди участвующих в вычислениях блоков 1 (отказы блоков 1 из отключенной части устройства не регистрируются) устройство вновь переходит в режим реконфигурации, который проходит аналогично рассмотренному выше случаю, При этом счетчик 53 переключается в очередное состояние 2 и на втором выходе дешифратора 54 появляется .1, которая устанавливает второй триггер 56 первой группы в 1 и разрешает прохождение информации через второй элемент И 55, при этом второй, триггер 57 второй группы устанавливается в Т (если + 1 j S-Д) или остается

.-., t

в О (если п).

После завершения режима реконфигурации устройство вновь переходит в рабочий режим с пониженным быстродействием и продолжает функционирование.

Когда в устройстве будет зафиксирован m-й отказ блоков 1, то образуется конфигурация из одного блока 1, выход 23 которого через блок 4 коммутации подключается к информационному входу блока 5, настраиваемого на задержку в (п-1) тактов. Вход слагаемого этого блока 1 через соответствующий коммутатор 3 и первый коммутатор подключается к выходу 26 блока 5 задержки. Далее устройство работает аналогично.

Таким образом, устройство за счет реконфигурации после отказов операционных блоков 1 и продолжение вычислений с использованием части исправного оборудования при пониженном быстродействии сохраняет работоспособность до 1од2П отказов операционных блоков, что повышает надежность устройства.

Устройство состоит из однотипных узлов и блоков, что делает его перспективным при разработке современных наращиваемых средств на БИС и СБИС.

Технико-экономические преимущества устройства умножения заключается в его более высокой надежности, достигаемой за счёт реконфигурации устройства.

Формула изобретен.ия Устройство для умножения, содержащее п операционных блоков (п - разрядность множимого), регистр множимого, блок задержки и первый коммутатор, управляющий вход которого соединен с первым управляющим входом устройства, вход множителя которого соединен с входами множителя п операционных блоков, входы множимого которых соединены с выходами соответствующих разрядов регистра множимого, первый и второй информационные входы первого коммутатора соединены соответственно С входом коррекции устройства и выходом блока задержки, а выход - с входом слагаемого n-го операционного бло- а, отличающееся тем, что, с целью повышения надежности устройства, оно содержит (п-1) коммутаторов, блок коммутации, сдвигатель, коммутаторы множимого и йода сдвига и блок управления реконфигурацией, причем вход слагаемого 1-го операционного блока (,...,п-1) соединен с выходом (n-l+1)-ro коммутатора, первый информационный вход которого соединен с выходом первого коммутатора, управляющий вход блока задержки соединен с первым выходом блока управления реконфигурацией, второй выход которого соединен с управляющим входом k-ro коммутатора (...,n) и первым информационным входом коммутатора кода сдвига, выход которого соединен с управляющим входом сдвигателя, информационный вход которого соединен с выходом коммутатора множимого, первый информационный вход которого соединен с входом множимого устройства, второй управляющий вход которого соединен с управляющими входами коммутаторов множимого и кода сдвига, выход сдвигателя соединен с; входом регистра множимого, выход которого соединен с вторым информационным входом коммутатора множимого, выход k-ro операционного блока соединен с вторым информационным входом (n-k+2)-ro коммутатора и k-м информационным входом блока коммутации, первый информационный вход которого соединен с выходом первого операционного блока, а выход - с информационным входом блока задержки и выходом результата устройства, вход контроля которого соединен с входом блока управления реконфигурацией, третий выход которого соединен с управляющим входом блока коммутации и вторым информационным входом коммутатора кода сдвига, четвертый и пятый выходы блока управления реконфигурацией соединены соответственно с выходами отказа и прерывания устройства.

Фи. 2

ФигЗ

фиг. 4

26

СЕМ

Ј)/. S

pt/e. 6

i

2

г

37

36

37

32

29

Фиг.. 7

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой преобразователь координат | 1988 |

|

SU1536375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-11-20—Подача