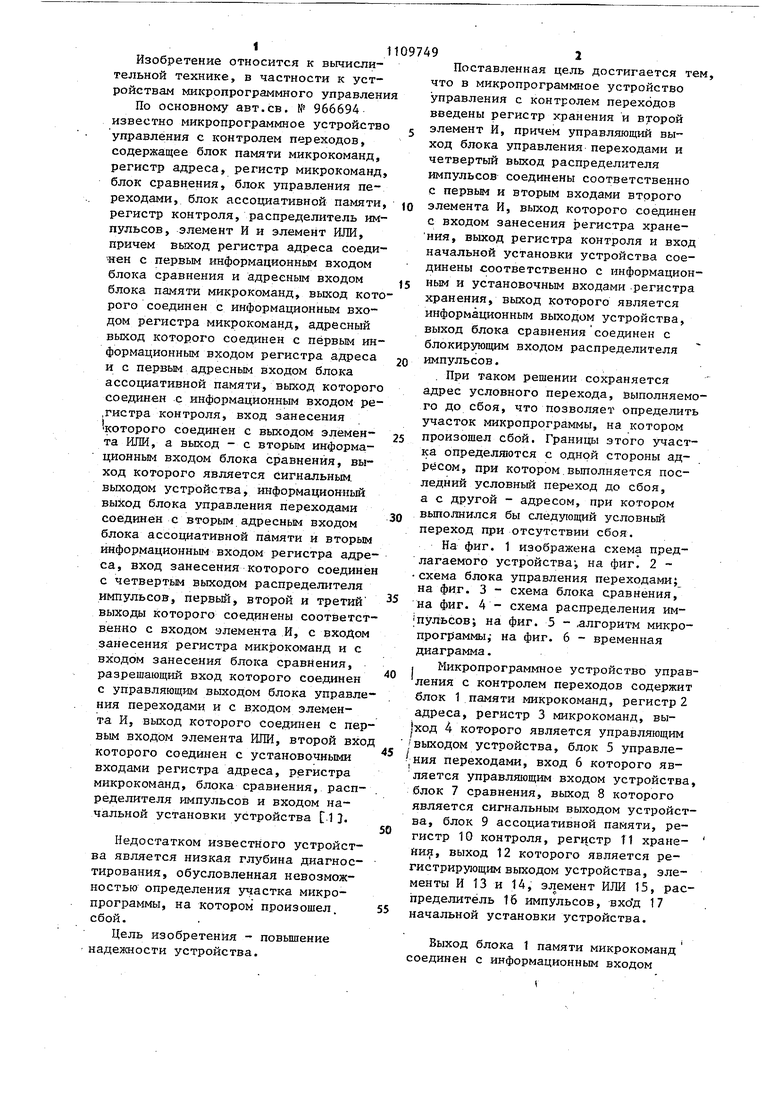

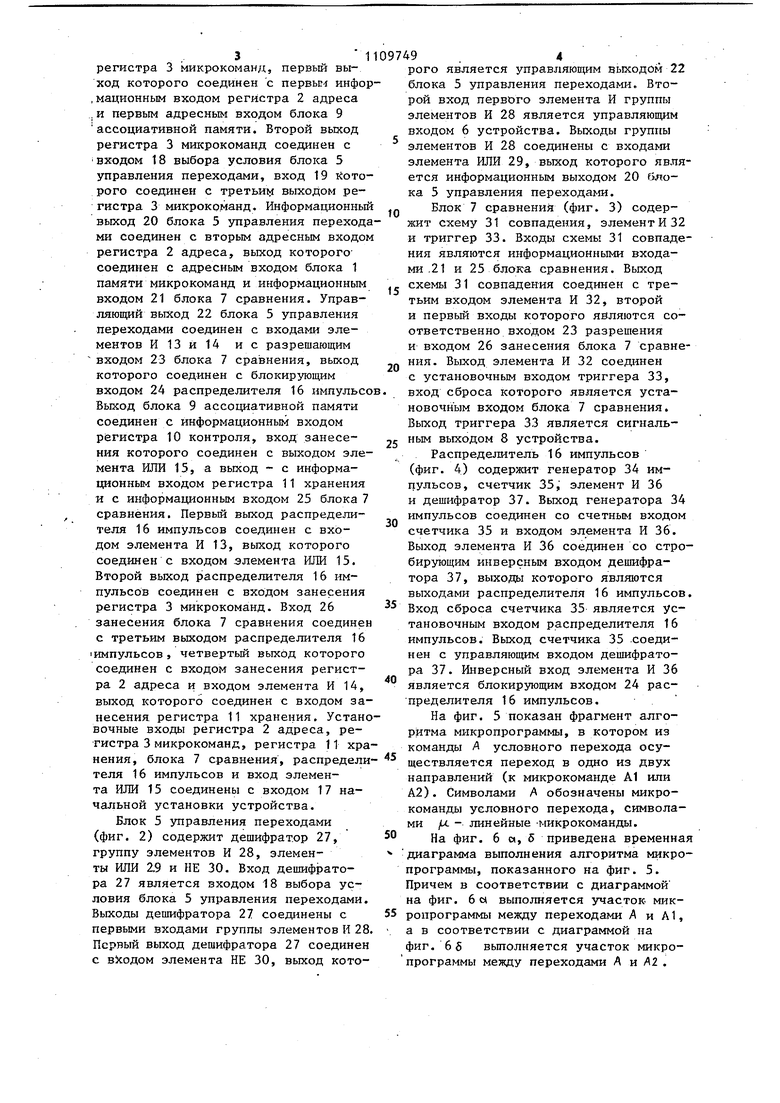

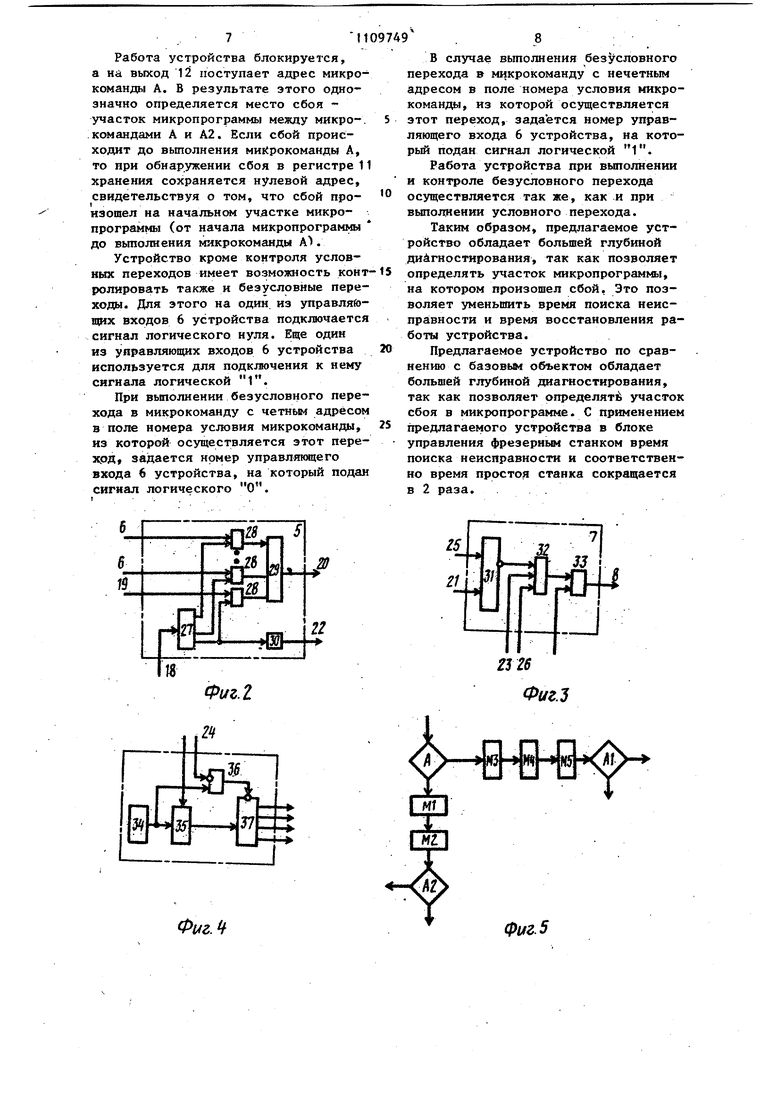

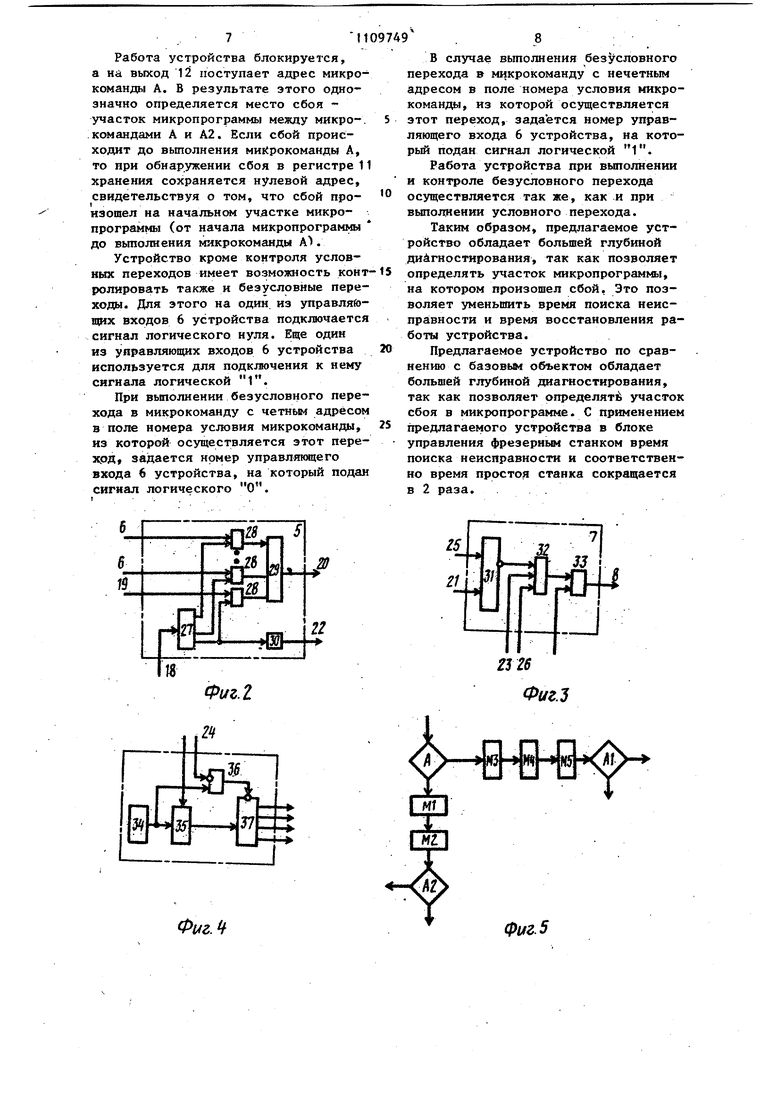

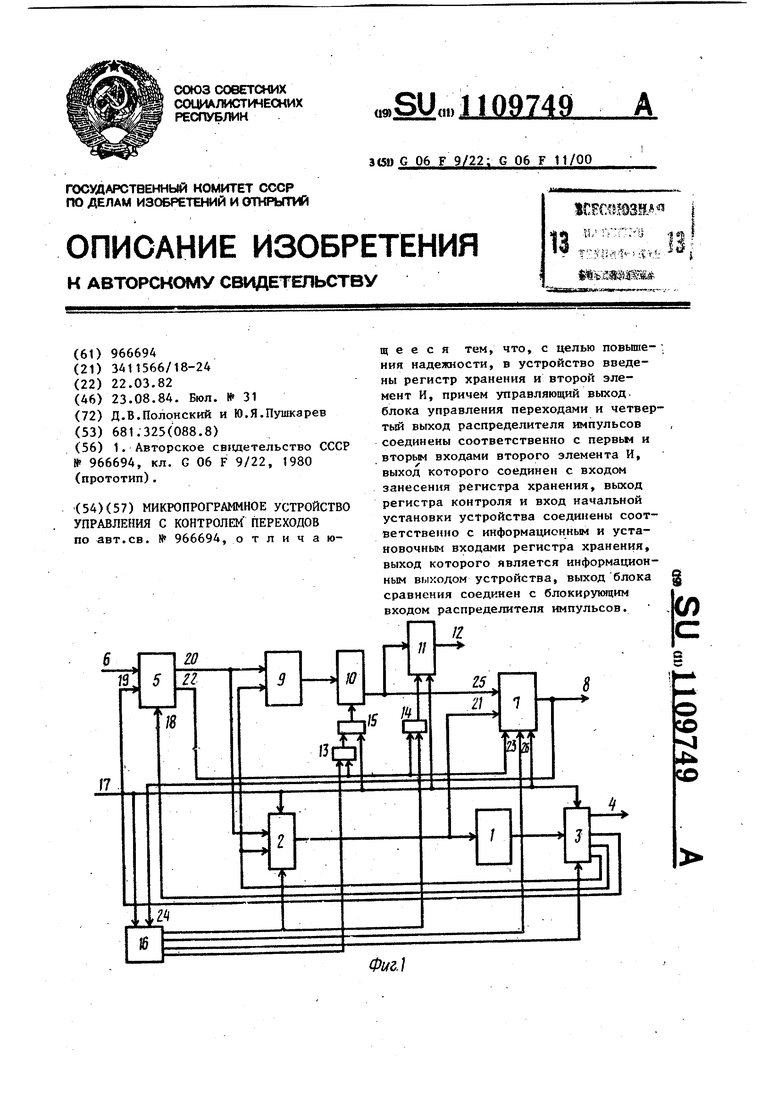

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управлен По основному авт.св. № 966694 известно микропрограммное устройств управления с контролем переходов, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд блок сравнения, блок управления переходами, блок ассоциативной памяти регистр контроля, распределитель им пульсов, элемент И и элемент ИЛИ, причем выкод регистра адреса соеди нен с первым информационным входом блока сравнения и адресным входом блока памяти микрокоманд, выход кот рого соединен с информационным входом регистра микрокоманд, адресный выход которого соединен с первым ин формационным входом регистра адреса и с первьм адресным входом блока ассоциативной памяти, выход которог соединен с информационным входом ре .гистра контроля, вход занесения которого соединен с выходом элемента ИЛИ, а выход - с вторым информационным входом блока сравнения, выход которого является сигнальным, выходом устройства, информационньй выход блока управления переходами соединен с вторым. адреснь1м входом блока ассоциативной памяти и вторым информационным входом регистра адре са, вход занесения которого соедине с четвертым выходом распределителя импульсов, первьй, второй и третий выходы которого соединены соответст венно с входом элемента И, с входом занесения регистра микрокоманд и с входом занесения блока сравнения, разрешающий вход которого соединен с управляющим выходом блока управле ния переходами и с входом элемента И, выход которого соединен с пер вым входом элемента ИЛИ, второй вхо которого соединен с установочными входами регистра адреса, регистра микрокоманд, блока сравнения, распределителя импульсов и входом начальной установки устройства .1 J. Недостатком известного устройства является низкая глзбина диагностирования, обусловленная невозможностью определения з астка микропрограммы, на котором произошел, сбой. Цель изобретения - повьшение надежности устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления с контролем переходов введены регистр хранения и второй элемент И, причем управляющий выход блока управления переходами и четвертый выход распределителя импульсов соединены соответственно с первым и вторым входами второго элемента И, выход которого соединен с входом занесения регистра хранения, выход регистра контроля и вход начальной установки устройства соединены соответственно с информационным и установочным входами регистра хранения, выход которого является информационным выходом устройства, выход блока сравнениясоединен с блокирующим входом распределителя импульсов. При таком решении сохраняется адрес условного перехода, выполняемого до сбоя, что позволяет определить участок микропрограммы, на котором произошел сбой. Границы этого участка определяются с одной стороны адресом, при котором.выполняется последний условный переход до сбоя, а с другой - адресом, при котором выполнился бы следующий условный переход при отсутствии сбоя. На фиг, 1 изображена схема предлагаемого устройства, на фиг. 2 схема блока управления переходами; на фиг. 3 - схема блока сравнения, на фиг. 4 - схема распределения импульсов; на фиг. 5 - «алгоритм микропрограммы,- на фиг. 6 - временная диаграмма. Микропрограммное устройство управления с контролем переходов содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микрокоманд, выход 4 которого является управляющим ВЫХОДОМ устройства, блок 5 управления переходами, вход 6 которого является управляющим входом устройства, блок 7 сравнения, выход 8 которого является сигнальным выходом устройства, блок 9 ассоциативной памяти, регистр 10 контроля, регистр 11 хранейи, выход 12 которого является регистрирующим выходом устройства, элементы И 13 и 14, элемент ИЛИ 15, распределитель 16 импульсов, вход 17 начальной установки устройства. Выход блока 1 памяти микрокоманд соединен с информационным входом регистра 3 микрокоманд, первый выход которого соединен с первьс- инфор ,мационным входом регистра 2 адреса .и первым адресным входом блока 9 ассоциативной памяти. Второй выход регистра 3 микрокоманд соединен с входом 18 выбора условия блока 5 управления переходами, вход 19 йоторого соединен с третьи выходом регистра 3 микрокоманд. Информационньш выход 20 блока 5 управления перехода ми соединен с вторым адресным входом регистра 2 адреса, выход которогосоединен с адресным входом блока 1 памяти микрокоманд и информационным входом 21 блока 7 сравнения. Управляющий выход 22 блока 5 управления переходами соединен с входами элементов И 13 и 14 и с разрешающим входом 23 блока 7 сравнения, выход которого соединен с блокирующим входом 24 распределителя 16 импульсо Выход блока 9 ассоциативной памяти соединен с информационным входом регистра 10 контроля, вход занесения которого соединен с выходом элемента ИЛИ 15, а выход - с информационным входом регистра 11 хранения и с информационным входом 25 блока 7 сравнения. Первый выход распределителя 16 импульсов соединен с входом элемента И 13, выход которого соединен с входом элемента ИЛИ 15. Второй вькод распределителя 16 импульсов соединен с входом занесения регистра 3 микрокоманд. Вход 26 занесения блока 7 сравнения соединен с третьим вькодом распределителя 16 импульсов, четвертый выход которого соединен с входом занесения регистра 2 адреса и входом элемента И 14, выход которого соединен с входом занесения регистра 11 хранения. Устано вочные входы регистра 2 адреса, регистра 3 микрокоманд, регистра 11 хра нения, блока 7 сравнения, распредели теля 16 импульсов и вход элемента ИЖ 15 соединены с входом 17 начальной установки устройства. Блок 5 управления переходами (фиг. 2) содержит дешифратор 27, группу элементов И 28, элементы ИЛИ 2.9 и НЕ 30. Вход дешифратора 27 является входом 18 выбора условия блока 5 управления переходами. Выходы дешифратора 27 соед11нены с первыми входами группы элементов И 28 Первый выход дешифратора 27 соединен с входом элемента НЕ 30, выход кото19 рого является управляющим выходом 22 блока 5 управления переходами. Второй вход первого элемента И группы элементов И 28 является управляющим входом 6 устройства. Выходы группы элементов И 28 соединены с входами элемента ИЛИ 29, выход которого является информационным выходом 20 )Яока 5 управления переходами. Блок 7 сравнения (фиг. 3) содержит схему 31 совпадения, элемент И 32 и триггер 33. Входы схемы 31 совпадения являются информационными входами .21 и 25 блока сравнения. Выход схемы 31 совпадения соединен с третьим входом элемента И 32, второй и первый входы которого являются соответственно входом 23 разрешения и входом 26 занесения блока 7 сравнения. Выход элемента И 32 соединен с установочным входом триггера 33, вход сброса которого является установочным входом блока 7 сравнения. Выход триггера 33 является сигнальным выходом 8 устройства. PacпpeдeJЮтeль 16 импульсов (фиг. 4) содержит генератор 34 импульсов, счетчик 35, элемент И 36 и дешифратор 37. Выход генератора 34 импульсов соединен со счетным входом счетчика 35 и входом элемента И 36. Выход элемента И 36 соединен со стробирующим инверсным входом дешифратора 37, выходы которого являются выходами распределителя 16 импульсов. Вход сброса счетчика 35 является установочным входом распределителя 16 импульсов. Выход счетчика 35 .соединен с управляющим входом дешифратора 37. Инверсный вход элемента И 36 является блокирующим входом 24 распределителя 16 импульсов. На фиг. 5 показан фрагмент алгоритма микропрограммы, в котором из команды А условного перехода осуществляется переход в одно из двух направлений (к микрокоманде А1 или А2). Символами А обозначены микрокоманды условного перехода, символами /U. - линейные -микрокоманды. На фиг. 6 а, 5 приведена временная диаграмма выполнения алгоритма микропрограммы, показанного на фиг. 5. Причем в соответствии с диаграммой на фиг. 6« выполняется участок микропрограммы между переходами А и А1, а в соответствии с диаграммой на фиг. 65 выполняется участок микропрограммы между переходами А и А2. Диаграмма на фиг. 6 S показывает работу устройства в случае возникновения сбоя. Цифрами на фиг. 6а, S обозначены импульсы 38-41 соответственно на пер вом, втором, третьем и четвертом выходах распределителя 16 импульсов, код 42 адреса на входах регистра 2 адреса и блока 9 код 43 адреса на выходе регистра 2 адреса, код 44 мик рокоманды на выходе блока 1 памяти микрокоманд, код 45 микрокоманды на выходе регистра 3 микрокоманд, контрольный адрес 46 на выходе блока 9 ассоциативной памяти, сигнал 47 на управляющем выходе 22 блока 5 управления переходами, импульсы 48 на выходе элемента ИЛИ 15, импульсы 49 на выходе элемента И 14, сигнал 50 ошиб ки на сигнальном выходе 8 устройства В исходное состояние устройство приводится подачей на вход 17 сигнала начальной установки, в результате чего регистр 2 адреса, регистр 3 мик рокоманд, регистр 11 хранения, счетчик 35 и триггер 33 устанавливаются в О, а в регистр 10 контроля заносится контрольный адрес для первого условного перехода в микропрограмме А . Рассмотрим работу устройства в соответствии с временной диаграммой, приведенной на фиг. 6а. После выполнения линейной последо вательности микрокоманд, предшествую щей микрокоманде условного перехода , в регистре 2 адреса формируется адрес микрокоманды А (позиция 43). По этому адресу из блока 1 памяти микрокоманд выбирается микрокоманда А и поступает на информацион ный вход регистра 3 микрокоманд (позиция 44). По импульсу 39 микрокоман да А заносится в регистр 3 микрокоманд (позиция 45). Так как в микрокоманде А1 выполняется условный пере ход, то поле номера условия в ней не равно О. Вследствие этого единичный сигнал вад абатывается на одном из выходов дешифратора 27, кроме первого, и на информационный выход 20 блока 5 управления переходами поступает сигнал соответствующего условия с входа 6 устройства. Сигнал 47 принимает единичное значение. Адрес следующей микрокоманды и адрес контрольного адреса для следующего условного перехода определяются в зависимости от значения (О или 1) сигнала условия. Напри- мер, по адресной части микрокоманды А и конкретному значению логического условия на информационных входах регистра 2 адреса формируется адрес ми рокоманды МЗ (позиция 42). По этому же адресу из блока 9 ассоциативной памяти выбирается контрольный адрес для условного перехода А1 (пози1Д1Я 46). Одновременно в блоке 7 сравнения производится сравнение контрольного адреса, содержащегося в регистре 10 контроля, с адресом микрокоманды А, содержащимся в регистре 2 адреса. Если адреса в регистре 2 и регистре 10 контроля совпадают, то установка триггера 33 по импульсу 40 не производится, так как элемент И 32 закрыт нулевьм сигналом с выхода схемы 31 )совпадения. При поступлении импульса 41 в регистр 2 адреса заносится адрес микрокоманды МЗ, а по импульсу 49 в регистр 11 хранения заносится адрес микрокоманды А. В следующем микрокомандном цикле по импульсу 48 контрольный адрес микрокоманды А1 заносится в регистр 10 контроля. По импульсу 39 микрокоманда МЗ заносится в регистр 3 микрокоманд. Так как микрокоманда МЗ является линейной микрокомандой, сигнал 47 принимает нулевое значение. После вьшолнеНия микрокоманд МЗ, М4 и М 5 в регистре 3 адреса формируется адрес микрокоманды А1. Так как на участке между переходами А и А1 сбоев не происхохщт, микрокоманда А1 выполняется так же, как и микрокоманда А. Выполнение участка микропрограммы между переходами А и А2 (фиг. 66) начинается аналогично описанному примеру по вьтолнёнию участка микропрограммы между переходами А и А1 с той лишь разницей, что в регистр 10 контроля заносится контрольный адрес микрокоманды А2. В случае возникновения сбоя устройство переходит на выполнение другой (ложной) линейной последовательности микрокрманд, после которой выпо;шяется команда условного перехода Ах. Так как адрес микрокоманды Ад не совпадает с контрольным адресом микрокоманды А2, то по импульсу 40 вырабатьгеается сигнал 50, сигнализи-. руя о сбое. Работа устройства блокируется, а на выход 12 поступает адрес микрокоманды А. В результате этого однозначно определяется место сбоя участок микропрограммы между микро-. командами А и А2. Если сбой происходит до вьтолнения ми1(рокоманды А, то нри обнаружении сбоя в регистре 1 хранения сохраняется нулевой адрес, свидетельствуя о том, что сбой произошел на начальном участке микропрограммы (от начала микропрограммы до вьшолнения микрокоманды А). Устройство кроме контроля условных переходов имеет возможность конт ролировать также и безусловные переходы. Для этого на один, из управлжьщих входов 6 устройства подключается сигнал логического нуля. Еще один из управляющих входов 6 устройства используется для подключения к нему сигнала логической 1. При выполнении безусловного перехода в микрокоманду с четным адресом в поле номера условия микрокоманды, из которой осуществляется этот перехрд задается номер управляющего входа 6 устройства, на который подан сигнал логического О. В случае вьтолнения безусловного перехода в микрокоманду с нечетным адресом в поле номера условия микрокоманды, из которой осуществляется этот переход, задается номер управляющего входа 6 устройства, на который подан сигнал логической 1. Работа устройства при выполнении и контроле безусловного перехода осуществляется так же, как и при выполнении условного перехода. Таким образом, предлагаемое устройство обладает большей глубиной диагностирования, так как позволяет определять участок микропрограммы, на котором произошел сбой. Это позволяет уменьшить время поиска неисправности и время восстановления работы устройства. Предлагаемое устройство по сравнению с базовым объектом обладает большей глубиной диагностирования, так как позволяет определят участок сбоя в микропрограмме. С применением предлагаемого устройства в блоке управления фрезерным станком время поиска неисправности и соответственно время простоя станка сокращается в 2 раза. .

М

Фиг.

ФигЛ KMi Г - П /(/

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1254481A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Микропрограммное устройство управления с исправлением ошибок | 1981 |

|

SU985789A1 |

| Микропрограммное управляющее устройство | 1981 |

|

SU1005051A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ ПЕРЕХОДОВ по авт.св. № 966694, отличающееся тем, что, с целью повьппе- ; ния надежности, в устройство введены регистр хранения и второй элемент И, причем управляющий выходблока управления переходами и четвертый выход распределителя импульсов соединены соответственно с первые и вторьм входами второго элемента И, выход которого соединен с входом занесения регистра хранения, выход регистра контроля и вход начальной установки устройства соединены соответственно с информационным и установочным входами регистра хранения, выход которого является информационным выходом устройства, выход блока сравнения соединен с блокирующим (Л входом распределителя импульсов. ;О 4 СО

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1982-03-22—Подача