(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

12

Изобретение относитря к области вычислительной техники и может быть, использовано в ассоциативных процессорах, поэволякадих осуществлять параллельную обработку больших массивов данных.

Известно микропрограммное устрой-; ство управления, содержащее блок памяти, генератор тактовых импульсов, регистр адреса, регистр микрокоманды, дешифратор, логические элементы tilНедостатком устройства является то, что для анализа условий, определяккцих направление переходов при выполнении микропрограмм, затрачивается большое количество разрядов микрокоманд. Кроме того, устройство отличается малым быстродействием и применение его в ассоциативных процессорах малоэффективно.

Наиболее близким к предлагаемому является микропрограммное устройство управления,.содержащее блок памяти с дешифратором, регистр адреса и регистр микрокоманд, блок формирования адреса и блок формирования адреса условного перехода, включающий в себя регистр признака устройства, элемент ИЛИ и дешифратор

условий, входные шины адреса микрокоманд и сигналов, анализируемых условий и выходную шину микрокоманд 2,

Недостатком устройства является низкое быстродействие, вызванное необходимостью прохождения адреса следующей микрокоманды через блок формирования адреса регистр адреса, память микрокоманд и дешифратора

to микрокоманд, причем в регистр адреса запишется достоверный адрес лишь только после анализа условия перехода в дешифраторе условий. Таким образо, следующий такт вычислитель15ного устройства должен быть начат после всех этих задержек.

Цель изобретения - повышение быстродействия устройства микропрограммного управления.

20

Цель достигается тем, что микропрограммное устройство управления, содержащее блок памяти микрокоманд, nepBbdl регистр Управляющих команд, выходы разрядов адреса, кроме

25 последнего, первой группы которого подключены к информационным входам первой группы первого коммутатора адреса соответственно, первый элемент ИЛИ, дополнительно содержит

30 второй регистр управляющих команд.

второй коммутатор адреса, второй элемент ИЛИ, блок памяти управлякяци команд, триггер условного перехода счетчик циклов, группу элементов НЕ и элемент И-НЕ, причем выход второг когФ1утатора соединен с адресным входом блока памяти управляющие команд выход которого соединен с и нформационными входами первого и-второго регистров управляющих команд, к управляинцим входам которых подключены и второй входы синхроимпуль;сов устройства ооответственно, выхоДы последних разрядов адреса первых групп первого и второго регистров управляющих команд подключены к первым входам первого и второго элементов ИЛИ соответственно, вторые входы которых соединены с выходом триггера условного перехода, информационный вход которого соединен с входом признака условного перехода устройства, а управлшогаий вход - с третьим входом: синхроимпульса, устройства, выходы разрядов адреса, кроме посяедаего, первой группы второго регистра управляющих команд подключены к информационным входам второй,группы первого коммутатора соответственно, первые и второй уп равл5шшше входы которого соединены с первым и вторым управлявядими входами второго комнутатора и являются четвертым и пятым входами сннхроилйхульсов устройства соответственно выход первого коммутатора подключен к а.цресно(й входу блока памяти шикрокоманд, выход которого являемся информационньа выходом устройства, а выход мпздаоего разряда соединен со счетным входом счетчика 1щклог, информационный вход которого подключен к ахсзду числа циклов устройства, а выход - к входам элемемт тов НЕ груп1ш, выхода которых соединены с входами элемента , вы ход которого подключен к управляю тему выходу устройства, аыхсщы разрядов адресов вторых групп первого и второго регистров управляюке х команд подключены к первому и второму инфор шщюнным входам второго коммутатора, третий информацшэнный вход которого подключен к входу адреса устройства, а третий управляющий вход - к входу пуска устройст а.

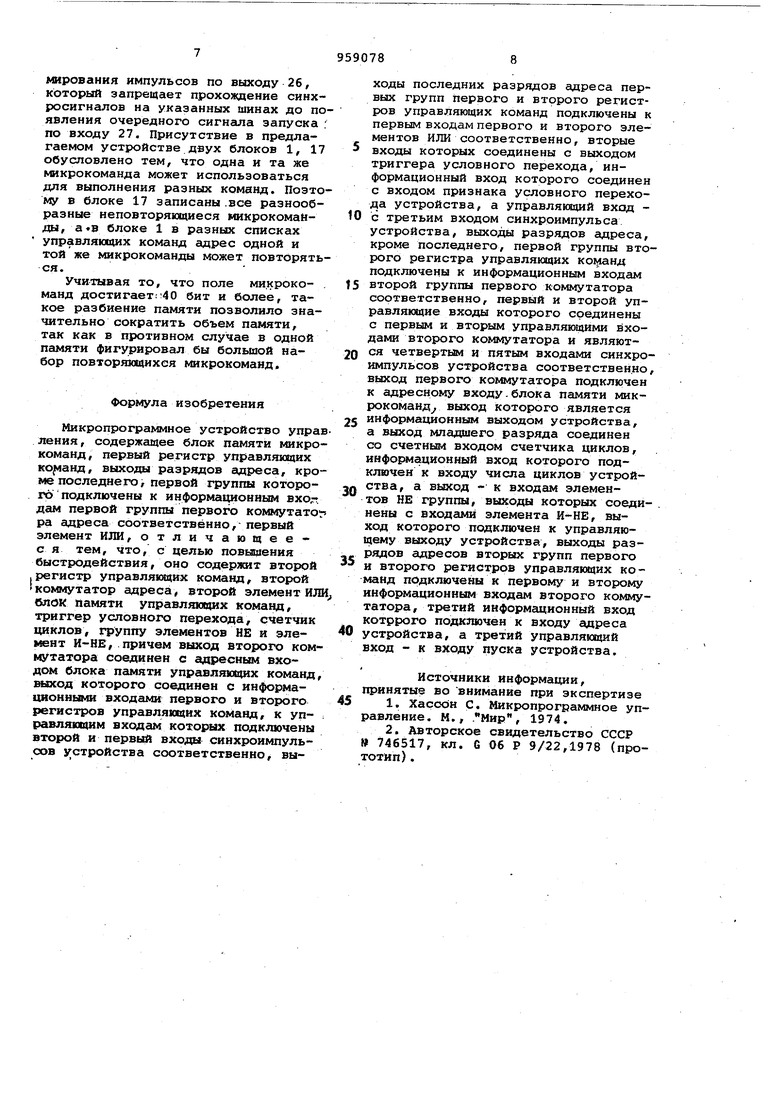

На чертеже представлена структурная схема микропрограммного устройства управления.

Устройство содержит блок 1 памяти управляющих комавд, регистры 2, 3 управляющих команд разрядности (к + п)блок 4 формирования адреса условного перехода, содержащий элементы ИЛИ 5, б и триггер 7 условйого перехода, коммутатор 8 адреса, содержащий две группы элементов И 9

10 и группу элементов ИЛИ-НЕ 11, коммутатор 12-адреса, содержащий тр группы элементов И 13, 14, 15 и групу элементов ИЛИ-НЕ 16, блок 17 памяти микрокоманд, группу элементов, блок 18 подсчета числа.циклов, счетчик 19 циклов, группу элементов НЕ20, элемент И-НЕ 21, вход 22 адреса устройства, вход 23 признака условного перехода, вход 24 числа циклов, информационный выход 25 устройства, управляющий выход 26 устройства, вход 27 пуска устройства, входы 28 - 32 синхроимпульсов устройства.

Фуйкциснирование устройства происходит следукяцим образом.

Информацияi записываемая в тот или иной регистр 2, 3 управляющих команд, состоит из двух частей. Первая К-разрядная часть регистров представляет собой .адрес соответствующей микрокоманды 3 блоке 17 памяти микрокоманд. Вторая п-разрядная часть регистров предоставляет собой адрес следующей управляющей команды. Причем, в блоке 1 памяти управляющих команд адрес следукадей управЛ5иощей команды записан в инверсном коде, но после прохождения коммутатора 12 он инвертируется и уже в прмом коде поступает на адресные входы блока 1 памяти управляющих команд. Для .выполнения той или иной команды в блоке 1 в соответствии с адресом - командой, поступакадей.по входу 22, выбирается определенный список управляющих команд адресовК Этому списку управляющих команд поставлен в соответствие определенный набор микрокоманд в блоке 17, необходимый для выполнения конкретной команды либо над двумя одноименными разрядными слайсами двух массивов либо над одним разрядным слайсом одного массива. Причем, во второй п-разрядной части последней управлякадей команды любого списка управляшнх команд указан адрес первой управляш ей команды данного списка.

подобная организация списков управляющих команд позволяет использовать каждый из них столько раз, сколько разрядных слайсов содержит обрабат{:зваемые массивы. Команда о выполнении той или иной операции (сложение, вычитание, поиск и т.д.7 поступает в виде адреса памяти управ л якадих команд по входу 22 одновременно с подачей синхросигнала по входу 27. Одновременно этот сигнал поступает в блок формирования импульсов (не показан ) и разрешает появление синхросигналов на входах 30, 31, которые разнесены во времени. Выбранная из блока 1 инфорМсщия подводится одновременно к двум регистрам 2, 3 управляющих команд, но она запишется в тот регистр, на синхронизирующий вход которого первым поступит импульс записи по входам 30, либо 31. Длительность синхроимпульса по входу 27 выдержана, таким образом, чтобы осуществить запись в один из регистров 2, 3 управлякицих команд. Появление синхроимпульса по входу 30 и 31 разрешает появление синхросигналов соответственно на входах 29 или 28,

Допустим, что первым пришел импульс записи по входу 30 синхросигналов, который разреишл запись первой выбранной управляющей команды в регистр 3 управляющих команд, п-разрядная информация об адресе еледующей управляющей команды со второй части этого регистра поступает на соответствующие входа коммутатора 12. Сигнал записи на входе 30 формирует синхросигнал на входе 29, который разрешает прохождение рядной информации через коммутатор 1 к адресным входам блока 1. ПЬсле чего осуществляется выбор следукяцей управляющей команды с целью записи ее в регистр 2 управляющих команд. Одновременно этот синхросигнал на входе 29 разрешает прохождение ком К-разрядной информации первой.части регистра 3 управляющих команд через коммутатор 8 к адресным входам блока 17. После чего на выходе 25 появится соответствующая микрокбмакнда. С этого NKJMeHTa в соответствии с тактовым импульсом начинается выполнение данной микрокоманды в ассоциативном процессоре. Одновременно этот тактовый сигнал по входу 32 поступает на синхрс низирующий вход триггера 7. Длительность тактового . импульса обусловлена временем выполнения наиболее длительной мнкрокрмбънды в ассоциативном процессоре и не превышает 150-200 не. К моменту окончания выполнения текущей микрокоманды, а следовательно, и окончания тактового икшульса осуществляется запись управляющей команды в регистр 2 по сигналу записи по входу 31, который, в свою очередь, формирует синхросигнал на входе 28. Теперь уже этрт синхросигнал разрешает прохождение и-разрядной информации регистра 2 через ко№лутатор 12 к адресным входам блока 1, а также К-разрядной информации через коммутатор 8 к адресным входам блока 17 и.т.д. Появление одного синхросигнала на входе 28 и окончание другого на входе 29, а также появление одного синхросигнала на входе 29 и окончание другого на входе 28 совпадает по времени с окончанием импульса на входе 32.

Отрицательным фронтом импульса, приходящего по входу 32, триггер 7 взводится в единичное или нулевое состояние в зависимости от того, какой уровень приходит по входу 23.

Для тех команд, которые требуют условный переход, этот уровень формируется после окончания выполне- ния микрокоманды в ассоциативном процессоре. По входу 23 приходит

0 единичный сигнал только в том случае , если необходимо совершить условный переход. Условный переход от одной микрокоманды к другой осуществляется изменением содержимого

5 мпадшего К-го разряда первой части регистров 2, 3. Это изменение осуществляется с помсадью Элементов ИЛИ 5 или 6. В младшем К-ом разряде адреса микрокоманды. Который может

0 быть.изменен, записано нулевое значение. Это значение может быть изменено в случае, если с триггера 7 придет признак условного перехода, соответствующий уровню, логичесной

5 единицы. Следовательно, на адресные входы блока 17 поступит адрес, отличный на единицу от адреса, кото1№зй запИсан в первой к-разрядной части регистров 2 или 3.

30

После вьадачи набора микрокоманд

из блока 17,,необходимого для обрабртки одного разрядного слайса массива или двух одноимённых разрядных слайсов двух массивов, с млад- ;

шего разряда последней микрокоманды I данного набора микрокоманд поступа-; ет сигнал на счетный вход счетчи- i ка 19. Этот сигнал осуществляет уменьшение содержимого счетчика 19

на единицу. Информация о количестве циклов, необходимых для выполнения операции над Массивами данных, равна разрядн хсти массивов и заносится в счетчик 19 перед началом выполнения операции по входу 24. Занесение этой инфОЕ 1ащ и совпадает во времени с подачей сигнала запуска по входу 27. Выходы счетчика 19 через группу элементов НЕ 20

подключены ко входам элемента И-НЕ 21 Когда содержимое счетчика 19 полностьЮ обнулится, на всех входах элемента И-НЕ 21 присутствуют уровни логической единицы. Это вызыва-

ет появление сигнала логического

55

нуля на выходе 26, который запрещает появление синхросигналов на входах 27-32.и означает конец выполнения команды. Таким образом, работа микропрограммного устройства управ60ления начинается с поступления сигнала запуска по входу 27, который разрешает последовательную вьщачу из блока формирования импульсов синхросигналов 31, 28, 32, 30, 29 и оканчивается выдачей сигнала в блок фор- мирования импульсов по выходу 26, который запрещает прохождение синхросигналов на указанных шинах до по явления очередного сигнала запуска по входу 27. Присутствие в предлагаемом устройстве двух блоков 1, 17 обусловлено тем, что одна и та же микрокоманда может использоваться для выполнения разных команд. Поэто му в блоке 17 записаны .все разнообразные неповторяющиеся микрокоманды, а«в блоке 1 в разных списках управлякхцих команд адрес одной и той же микрокоманды может повторять ся. Учитывая то, что поле ми.крокоманд достигает: 40 бит и более, такое разбиение памяти позволило значительно сократить объем памяти, так как в противном случае в одной памяти фигурировал бы большой набор повторякхцихоя микрокоманд. Формула изобретения Микропрограммное устройство упра ления , содержащее блок памяти микро команд, первый регистр управляющих , выходы разрядов адреса, кро ме последнего, первой группы которого подключены к информационным вхол дам первой группы первого коммутато ра адреса соответственно, первый элемент ИЛИ, отличающеес я тем, что, с целью повышения быстродействия, оно содержит второй .регистр управляющих команд, второй -коммутатор адреса, второй элемент HJ блок памяти управляющих команд, триггер условного перехода, счетчик циклов, группу элементов НЕ и И-НЕ, .причем вьосод второзго ком мутатора соединен с адресным входом блока памяти управляющих команд касод которого соединен с информационными входами первого и второго регистров управляющих команд, к управляющим входам которых подключены второй и первьЕй входы синхроимпульсов устройства соответственно, выходы последних разрядов адреса перВ1ЛХ групп первого и второго регистров управляющих команд подключены к первым входам первого и второго элементов ИЛИ соответственно, вторые входы которых соединены с выходом триггера условного перехода, информационный вход которого соединен с входом признака условного перехода устройства, а управляющий вход с третьим входом синхроимпульса устройства, выходы разрядов адреса, кроме последнего, первой группы второго регистра управляквдих подключены к информационным входам второй группы первого коммутатора соответственно, первый и второй управляющие входы которого соединены с первым и вторым управлякидими входами второго коммутатора и являются четвертьвл и пятым входами синхроимпульсов устройства соответственно, выход первого коммутатора подключен к адресному входу.блока памяти микрокоманду выход которого является информационным выходом устройства, а выход младшего разряда соединен со счетным входом счетчика циклов, информационный вход которого подключен к входу числа циклов устройства, а выход - к входам элементов НЕ группы, выходы которых соединены с входами элемента И-НЕ, выход которого подключен к управляющему выходу устройства, выходы разрядов адресов вторых групп первого и второго регистров управляющих команд подключены к первому и второму информационным входам второго коммутатора, третий информационный вход котррого подключен к входу адреса устройства, а третий управляющий вход - к входу пуска устройства. Источники информации, принятые во внимание при экспертизе 1. Хасоон С. Микропрограммное управление. М., .Мир, 1974. 2. Авторское свидетельство СССР 746517, кл. G 06 Р 9/22,1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1200288A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство обработки информации | 1986 |

|

SU1451710A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1170457A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1774335A1 |

Авторы

Даты

1982-09-15—Публикация

1981-01-14—Подача