одновибратора, выход которого соединен со счетным входом счетчика адреса, выходы которого соединены с вторьоми входами элементов и второй группы, выходы которых соединены с вторыми входами элементов ИЛИ группы,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Микропрограммное устройство управления с восстановлением при сбоях | 1978 |

|

SU932495A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Микропрограммное устройство управления с контролем переходов | 1980 |

|

SU966694A1 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

1. УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ ПЕРЕХОДОВ, содержащее регистр управления переходами, регистр адреса, блок памяти микрокоманд, регистр микрокоманд и первый блок ассоциативной памяти, причем входы регистра управления переходами соединены с входами устройства, а выходы - с входами старших разрядов регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы младших разрядов которого соединены с входами младших разрядов регистра адреса, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей путем увеличения глубины тестирования в него введены регистр хранения адресов команд перехода, даиифратор кода операции, два блока сравнения, два буферных регистра, втоцой блок . ассоциативной памяти, два элемента задержки, формирователь адреса и два регистра индикации, причем выходы старших разрядов регистра микрокоманд соединены с входами деишфратора кода операции, выход которого соединен с входами синхронизации первого и второго буферпых регистров и регистра хранения адреса команд переходов и че1/ез первый элемент задержки подключен к входам разрешения записи первого и второго буферных регистров, а через второй элемент задержки соединен с входами разрешения чтения первого и второго блоков ассоциативной памяти, выходы регистра соединены с информационными входами - регистра хранения адресов команд переходов, выходы которого соединены с первыми группами входов первого и второго блоков сравнения, выход первого блока сравнения соединен с входом первого регистра индикации и с первым входом формирователя адреса, выход второго блока сравнения соединен с входом второго регистра индикации и с вторым входом формирователя адреса, выходы которого соединены с адресными входами первого и второго § блоков ассоциативной памяти, выходы (Л первого блока ассоциативной памяти соединены с информационными входами первого буферного регистра., выходы которого соединены с второй группой входов первого блока сравнения, выходы второго блока ассоциативной памяти соединены с информационными входами второго буферного регистра, выходы которого соединены с второй группой входов второго блока сравнения. 2. Устройство по п. 1, о т л и чающееся тем, что формирователь адреса содержит генератор импульсов, одновибратор, два счетчика адреса, две группы элементов И и 00 группу элементов ИЛИ, причем первый вход формирователя соединен с первыми, входами элементов И первой группы и входом генератора импульсов, выход которого соединен со счетным входом -.первого счетчика адреса, выходы которого соединены с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, ,выходы которых соединены с выходами .Формирователя, второй вход формирователя соединен с первыми входами элементов И второй группы и входом

Изобретение относится к цифровой вычислительной технике и может быть использовано при отладке в динамике программного обеспечения цифровых вы числительных машин (ЦВМ), Известно устройство, в котором контроль хода программы при естественной последовательности операций, а также при условных и безусловных переходах основан на использовании и быточности информации в кодах команд а также использовании контрольных ме ток, т.е. специальных команд, расположенных на ветвях программ Cl3. Недостатками таких устройств явля ется большой Объем оборудования (в частности, запоминающих устройств). или же увеличение времени счета. Наиболее близким по техническому решению к предлагаемому является мик ропрограммное устройство управления, содержащее регистр адреса, блок памя ти микрокоманд, регистр микрокоманд, регистр начала участка, блок управле ния переходами, два регистра сдвига и блок ассоциативной памяти, причем выходы регистра адреса соединены с входами блока памяти микрокоманд, выходы которого соединены с входами регистра микрокоманд, выходы которого соединены с первыми группами входов регистра адреса и первого регистра сдвига, а также с входами регистра начала участка, выходы которого соеди нены с первой группой входов блока ассоциативной памяти, вторая и третья; группы входов которого подключены ееответственно к выходам первого и второго регистров сдвига, а выходы соеди нены с вторыми входами регистров сдви га, выходы блока управления переходами подключены к входам регистра адреса и второго регистра сдвига 2. Недостатки данного устройства заключаются в том, что в программу введены дополнительные меткие что тре.-г бует увеличение памяти кроме того это устройство при ложных переходах возвратных, пропусках одной или нескольких микрокоманд, ложных выполнениях микрокоманд условного перехода не позволяет обнаруживать место ошибки в ходе выполнения программы, т.е. обеспечивает контроль всего тракта и не обеспечивает контроль элементов, входящих в тракт. Целью изобретения является увеличение глубины тестирования программного обеспечения ЦВМ, путем анализа ветвей на дереве програмьш, Поставленная цель достигается тем, что в устройство, содержащее регистр управления переходами, регистр адреса, блок памяти микрокоманд, регистр микрокоманд и первый блок ассоциативной памяти, причем входы регистра. управления переходами соеди„ены с входами устройства, а выходы входами старших разрядов регистра адреса, выходы которого соединены с адресными входами блока памяти микрокоманд, выходы которого соединены входами регистра микрокоманд, младших разрядов которого соединены с входами младших разрядов регистра адреса, введены регистр хра„ „„3 адресов команд перехода, дешифратор кода операции, два блока сравнения, два буферных регистра, второй 6, ассоциативной памяти, два элемента задержки, формирователь адре-- - --са и два регистра индикации,причем выходы старших разрядов регистра памикрокоманд соединены с входами дешифратора кода операции, выход кото „..„„.. „ „..„„ рого соединен с входами синхронизацйи пёрвого и второго буфёрны регистров и регистра хранения адресов команд перехода и через первый элемент задержки подключен к входам разрешения записи первого и второго буфер- ных регистров, а через второй элемент задержки соединен с входами разрешения чтения первого и второго блоков ассоциативной памяти, выходы регистра aiipeca соединены с информационными входами регистра хранения адресов команд переходов, выходы которого .соединены с первыми группами входов первого и второго блоков сравнения, выход первого блока сравнения соединен с входом первого регистра индикации и с первым входом формирователя адреса, выход второго блока сравнения соединен с входом второго регистра индикации и с вторым входом формирователя адреса, выхбды которого соединены с адресными входами первого и второго блоков ассоциативной памяти, выходы первого блока ассоциативной памяти соединены с информационными.входами первого буферного регистра, выходы которого соединены с второй группой .

входов первого блока сравнения, выходы второго блока ассоциативной памяти соединены с информационными .входами второго буферного регистра, выходы которого соединены с второй группой входов второго блока сравнения. .

Формирователь адреса содержит генератор импульсов, одновибратор, два счетчика адреса, две группы элементов и и группу элементов ИЛИ, причем первый вход формирователя соединен с первыми входами элементов И первой группы и входом генератора импульсов, выход которого соединен со счетным входом первого счетчика адреса, выходы которого соединены с вторыми Входами элементов И первой группы, выходы которых соединены с первыми входами элементов ИЛИ группы, выходы которых соединены с - выходами формирователя, второй вход формирователя соединен с первыми входами элементов И второй группы и входом одновибратора, выход которого соединен со счетным входом счетчика адреса, выходы которого соединены с вторыми входами элементов И второй группы, выходы которых соединены с вторыми входами элементов ИЛИ ГРУ ппы.

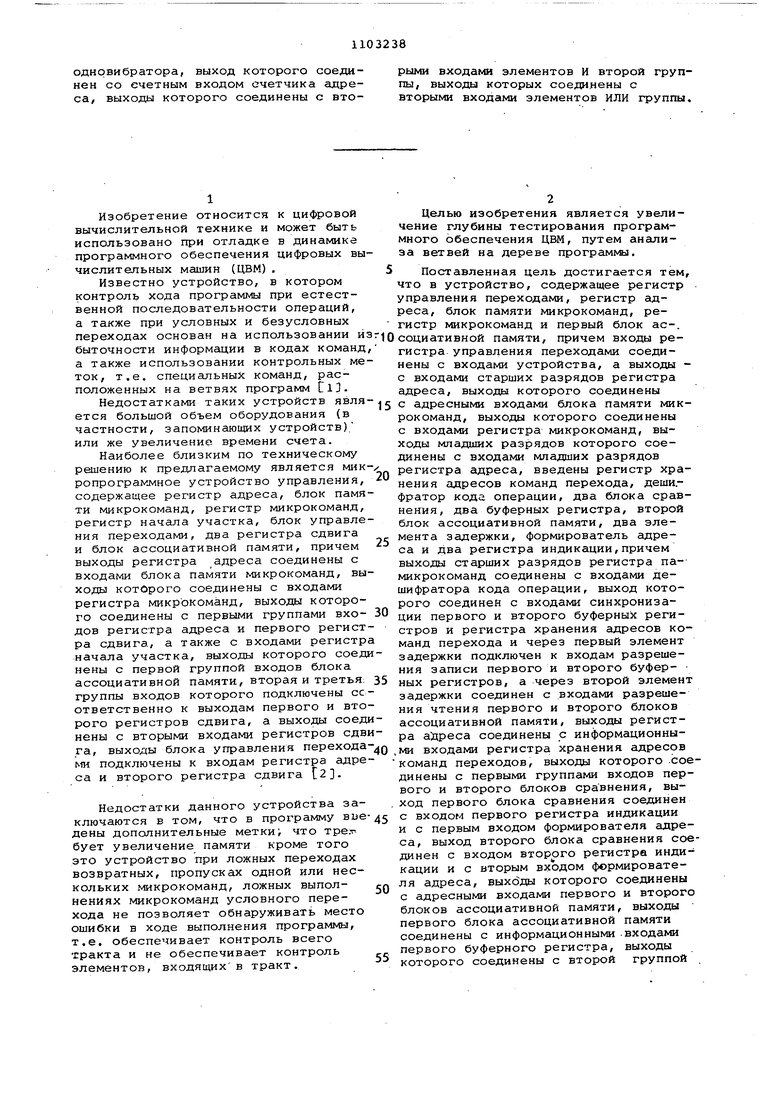

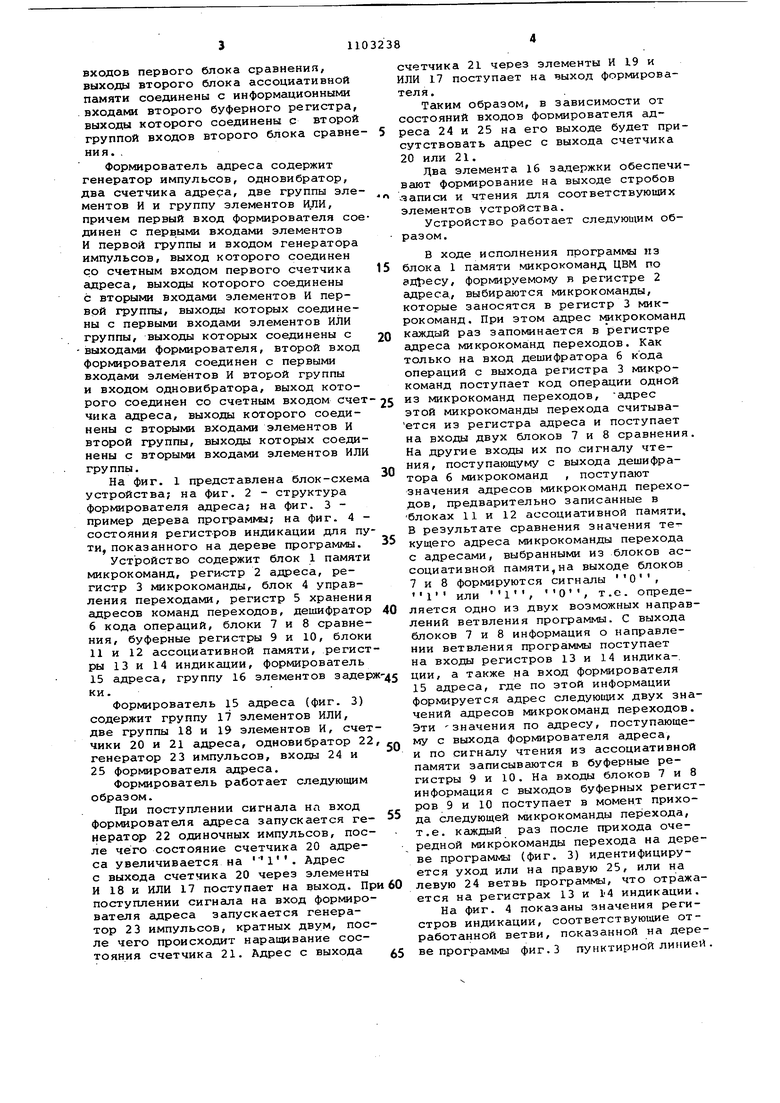

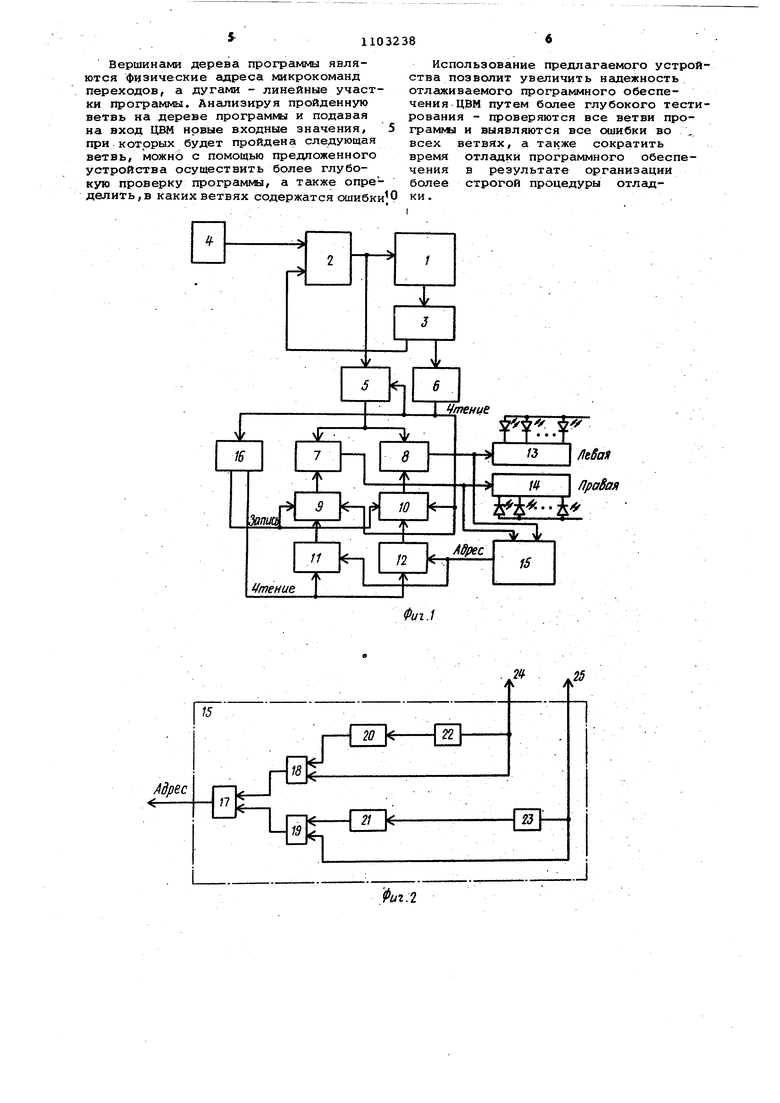

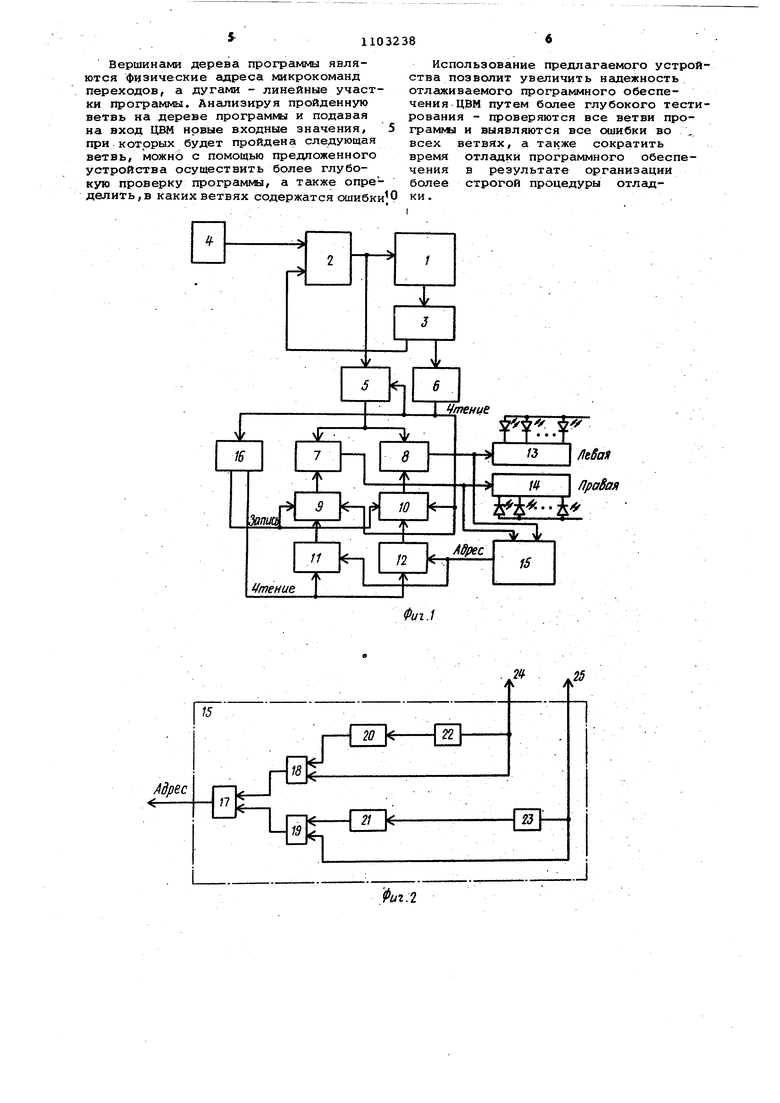

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - структура формирователя адреса; на фиг. 3 пример дерева программы; на фиг. 4 состояния регистров индикации для пути, показанного на дереве программы.

Устройство содержит блок 1 памяти микрокоманд, реги-стр 2 адреса, регистр 3 микрокоманды, блок 4 управления переходами, регистр 5 хранения адресов команд переходов, дешифратор 6 кода операций, блоки 7 и 8 сравнения, буферные регистры 9 и 10, блоки 11 и 12 ассоциативной памяти, регистры 13 и 14 индикации. Формирователь 15 адреса, группу 16 элементов задерки.

Формирователь 15 адреса (фиг. 3) содержит группу 17 элементов ИЛИ, две группы 18 и 19 элементов И, счетчики 20 и 21 адреса, одновибратор 22 генератор 23 импульсов, входы 24 и 25 формирователя адреса.

Формирователь работает следующим образом.

При поступлении сигнгша на вход формирователя адреса запускается генератор 22 одиночных импульсов, после чего состояние счетчика 20 адреса увеличивается на . Адрес с выхода счетчика 20 через элементы И 18 и ИЛИ 17 поступает на выход. Пр поступлении сигнала на вход формирователя адреса запускается генератор 23 импульсов, кратных двум, после чего происходит наращивание состояния счетчика 21. Адрес с выхода

счетчика 21 через элементы И 19 и ИЛИ 17 поступает на выход формирователя.

Таким образом, в зависимости от состояний входов формирователя адреса 24 и 25 на его выходе будет присутствовать адрес с выхода счетчика 20 или 21.

Два элемента 16 задержки обеспечивают формирование на выходе стробов яаписи и чтения для соответствующих элементов устройства.

Устройство работает следующим образом.

В ходе исполнения программы из блока 1 памяти микрокоманд ЦВМ по ахфесу, формируемому в регистре 2 адреса, выбираются микрокоманды, которые заносятся в регистр 3 микрокоманд. При этом адрес п1крокоманд каждый раз запоминается в регистре адреса микрокоманд переходов. Как только на вход дешифратора 6 кода операций с выхода регистра 3 микрокоманд поступает код операции одной из микрокоманд переходов, адрес этой микрокоманды перехода считывается из регистра адреса и поступает на входы двух блоков 7 и 8 сравнения На другие входы их по сигналу чтения , поступающуму с выхода дешифратора 6 микрокоманд , поступают значения адресов микрокоманд переходов, предварительно записанные в блоках 11 и 12 ассоциативной памяти, В результате сравнения значения текущего адреса микрокоманды перехода с адресами, выбранными из блоков ассоциативной памяти,на выходе блоков 7 и 8 формируются сигналы О , или Ч, , т.е. определяется одно из двух возможных направлений ветвления программы. С выхода блоков 7 и 8 информация о направлении ветвления программы поступает на входы регистров 13 и 14 индика-. ции, а также на вход формирователя 15 адреса, где по этой информации формируется адрес следующих двух значений адресов микрокоманд переходов. Эти -значения по адресу, поступающему с выхода формирователя адреса, и по сигналу чтения из ассоциативной памяти записываются в буферные регистры 9 и 10. На входы блоков 7 и 8 информация с выходов буферных регистров 9 и 10 поступает в момент прихода следующей микрокоманды перехода, т.е. каждый раз после прихода очередной микрокоманды перехода на дереве программы (фиг. 3) идентифицируется уход или на правую 25, или на левую 24 ветвь программы, что отражается на регистрах 13 и 14 индикации. На фиг. 4 показаны значения регистров индикации, соответствующие отработанной ветви, показанной на дереве программы фиг.З пунктирной линие

Вершинами дерева программы являются физические адреса микрокоманд переходов, а дугами - линейные участки программы. Анализируя пройденную ветвь на дереве програмкы и подавая на вход ЦВМ новые входные значения, при которых будет пройдена следующая ветвь, можнЬ с помощью предложенного устройства осуществить более глубокую проверку программы, а также определить, в каких ветвях содержатся ошибки

Использование предлагаемого устройства позволит увеличить надежность отлаживаемого программного обеспечения ЦВМ путем более глубокого тестирования - проверяются все ветви программы и выявляются все ошибки во всех ветвях, а также сократить время отладки программного обеспечения в результате организаций более строгой процедуры отладки.

/ П

О О О

О О

л

о

О О О О

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство с контролем переходов | 1977 |

|

SU711573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управ-лЕНия C КОНТРОлЕМ пЕРЕХОдОВ | 1978 |

|

SU807289A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-15—Публикация

1983-02-15—Подача