Изобретение относится к вычислительной технике и может быть использовано при разработке и конструировании высоконадежных микропроцессорных систем.

Целью изобретения является повышение отказоустойчивости работы устройства за счет реализации повторного выполнения сбойных микрокоманд и восстановления нормального функционирования микропрограммного устройства управления после сбоя.

Повышение надежности восстановления нормального функционирования микропрограммного устройства управления после сбоя достигается за счет того, что устройство обеспечивает возможность автоматической реализации повторных процедур восстановления после сбоев с увеличением глубины восстанов

ления в случае, если после выполнения однократной процедуры возврата к контрольной точке восстановление не было осуществлено. Кроме того, автомат, управляющий выполнением восстановления, не включает в себя ассоциативную память, что повышает достоверность ег работы. Возможность повышения надежности восстановления за счет увеличе- ния количества точек возврата следует из теоремы о повторении опытов.

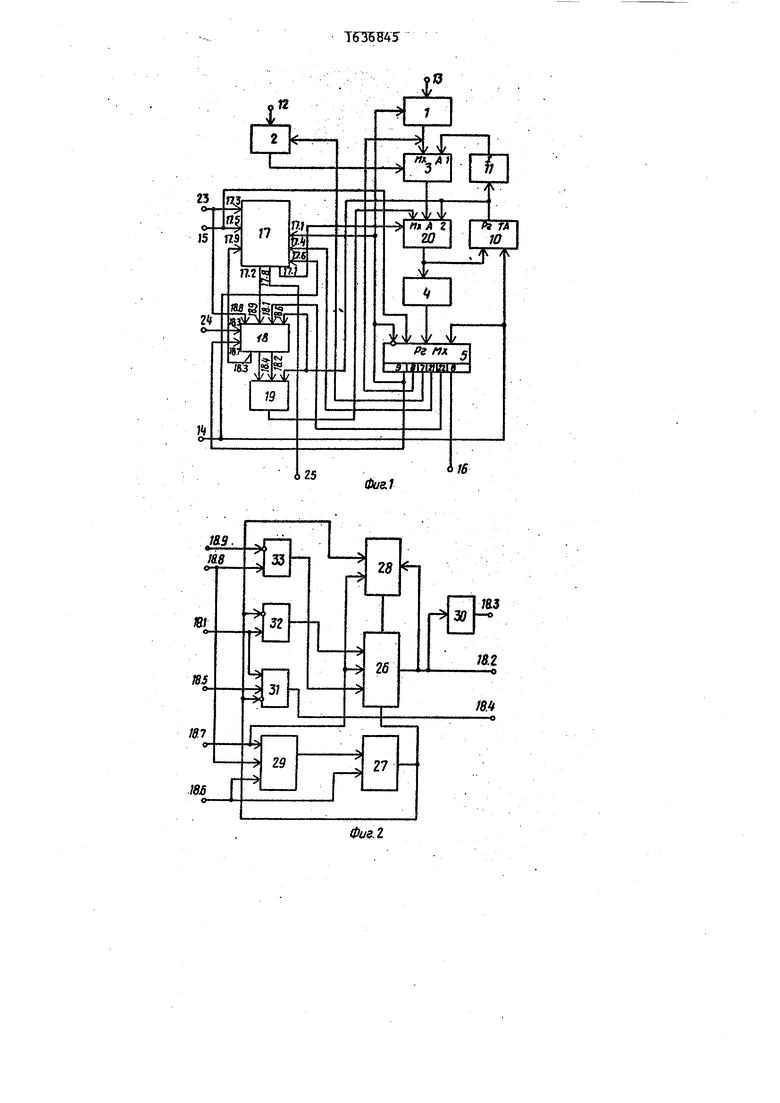

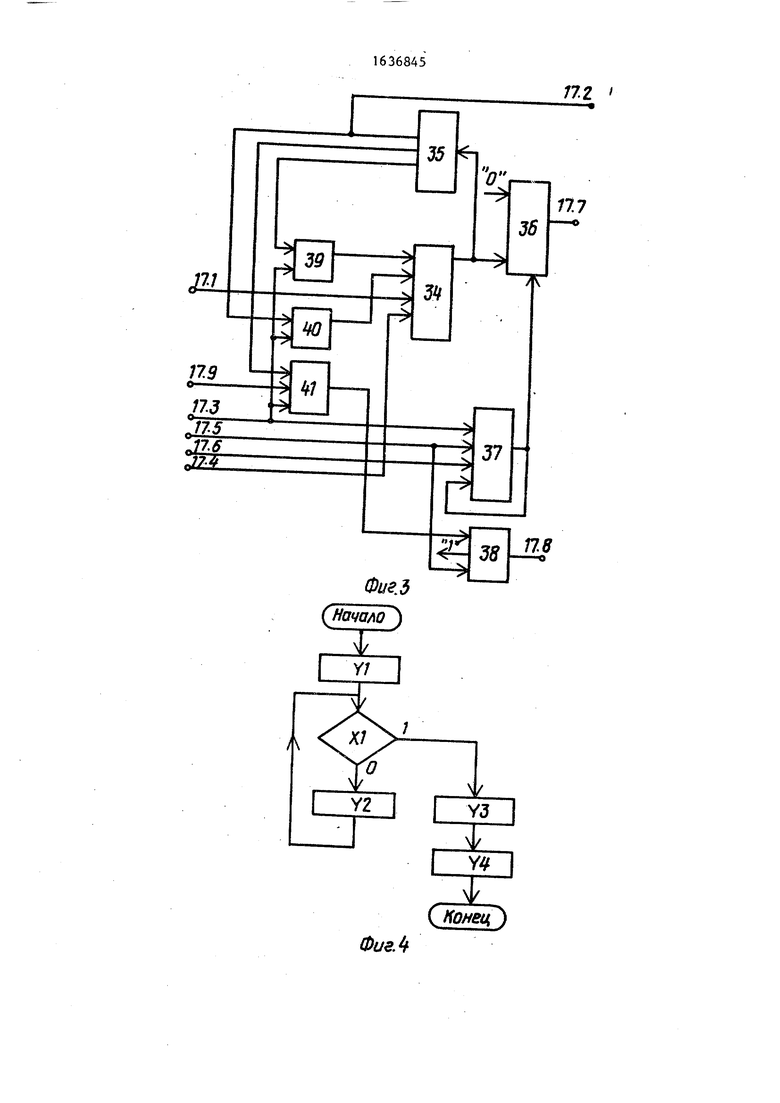

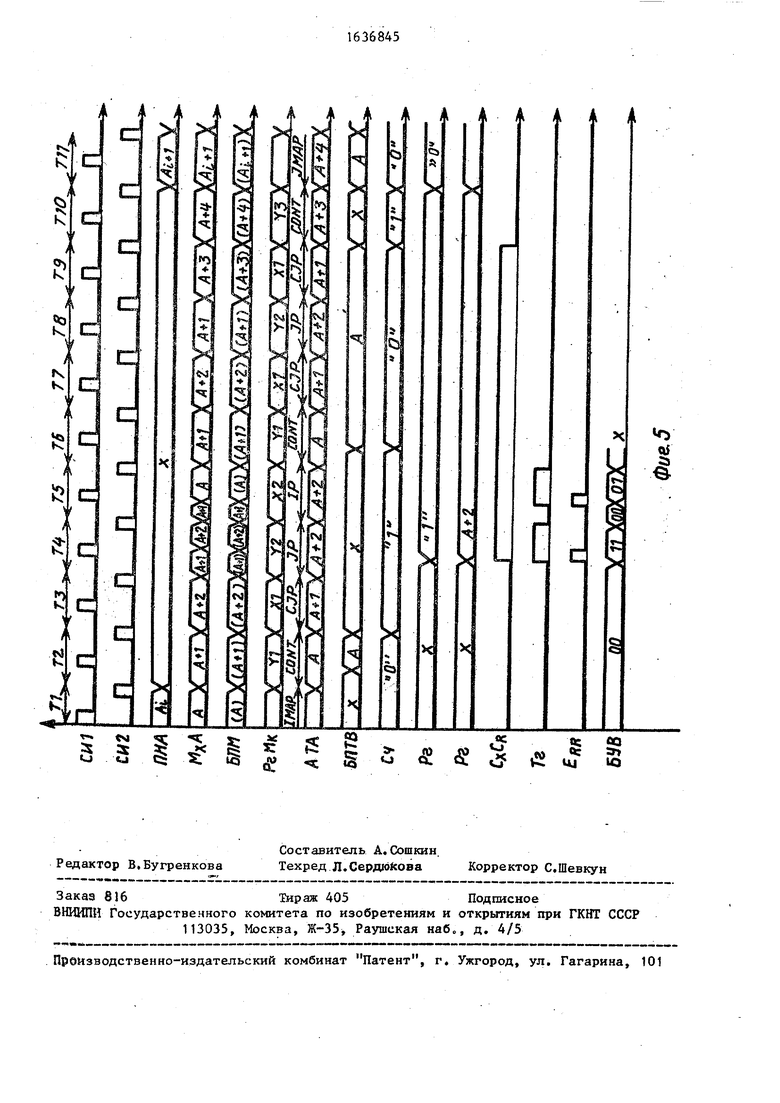

На фиг, 1 приведена структурная схема микропрограммного устройства управления; на фиг. 2 - то же, структур ная схема блока формирования точек возврата; на фиг, 3 - то же, блок управления восстановлением; нач

фиг, 4 - пример граф-схемы алгоритма микропрограммы; на фиг, 5 - времен- ная диаграмма работы устройства при восстановлении после сбоев, соответствующая алгоритму, представленному на фиг, 4.

Устройство микропрограммного управ ления (фиг. 1) содержит преобразователь 1 начального адреса, мультиплексор 2 условий, первьй мультиплексор 3 адреса, в котором выделены поле 6 адреса перехода, поле 7 кода условия, блок 4 памяти микропрограмм, регистр 5 микрокоманд, поле 8 микроопераций, выход 9 признака Конец микропрограммы, регистр 10 текущего адреса, ин- крементатор 11, вход 12 условий устройства, вход 13 начального адреса устройства, первый синхронизирующий вход 14 устройства, установочный вход 15 устройства, выход 16 микроопераций устройства, блок 17 управления восста ношением, блок 18 формирования точек возврата, блок 19 памяти точек возврата, второй мультиплексор 20 адреса, поле 21 кода восстановления и поле 22 формирования точек возврата регистра 5, вход 23 ошибки устройства, второй синхронизирующий вход 24 устройства, выход 25 идентификации отказа устройства.

Блок 18 формирования точек возвра- та (фиг, 2) содержит первый счетчик 26, схему 17 сравнения, первый 28 и второй 29 буферные регистры 29, элемент ИЛИ 30, первый 31, второй 32 и третий 33 элементы И.

Блок 17 управления восстановлением (фиг. 3) содержит второй счетчик 34, дешифратор 35, мультиплексор 36, IKQ

0

5 о

-

5

5

триггер 37, RS-триггер ;38, четвертый 39, пятый 40 и шестой 41 элементы И.

Организация точек возврата для реализации процедуры восстановления после сбоя осуществляется под управ- лением блока 17 формирования точек возврата. Для хранения точек возврата предназначен блок 19 памяти точек возврата. Непосредственно процедура восстановления после сбоя в соответствии с избранным методом восстановления осуществляется под управлением блока 17 управления восстановления.

Устройство микропрограммного управления функционирует следующим образом.

Импульсом начальной установки, поступающим с установочного входа устройства 15 на установочный вход регистра 5 микрокоманд и на вход 17,5 блока управления восстановлением, с которого поступает на установочные входы триггеров 37 и 38, регистр 5 микрокоманд, триггеры 37 и 38 приводятся в , исходные состояния. В исходном состоянии разряд признака конца микропрограммы в регистре 5 микрокоманд устанавливается в состояние логической единицы, что вызывает установку в исходные состояния регистров 28 и 29, счетчика 26 в блоке 18 формирования точек возврата и счетчика 34 в блоке управления восстановлением. В исходном состоянии в регистре 5 микрокоманд размещается микрокоманда, соответствующая микроинструкции перехода по начальному адресу, поле 9 признака конца микропрограммы устанавливается в состояние логической 1, что обеспечивает наличие сигнала разрешения на входе управления третьим состоянием преобразователя 1 начального адреса и сигнала запрета на входе управления третьим состоянием регистра 5 микрокоманд, переводящего в третье состояние разряды регистра

5микрокоманд соответствующие полю

6адреса перехода. Кроме того, в поле 7 кода условия регистра 5 микрокоманд помещен код, соответствующий внешнему условию перехода. На вход преобразователя 1 начального адреса

с входа устройства 13 поступает код выполняемой операции, что вызывает появление на выходе преобразователя 1 начального адреса выполняемой микрокоманды, которая, проходя через первый мультиплексор 3 адреса, поступает на вход второго мультиплексора 20 адреса. Наличие уровня логичес- кого нуля на выходе первого триггера 37 блока 17 управления восстановлением обеспечивает появление на выходе мультиплексора 36 .блока 17 управления восстановлением уровней логического нуля с вторых его информационных входов, а следовательно, и наличие уровней логического нуля, поступающих с первого выхода блока 17 управления восстановлением, на управляющем входе второго мультиплексора 20 адреса. При

68456

выходе первого мультиплексора 3 адреса кода, поступающего из поля адреса перехода регистра 5 микрокоманд и соответствующего адресу перехода. Точки возврата микропрограммы формируются под управлением блока 18 формирования точек возврата в блоке 1У памяти точек возврата, на вход которого с выхода регистра 10 текущего адреса поступает адрес выполняемой микропрограммы. При организации точки воз- , врата в поле 22 признака формирования точки возврата регистра 5 микрокоманд

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1254481A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение отказоустойчивости работы устройства за счет реализации повторного выполнения сбойных микрокоманд и восстановления после сбоя. Микропрограммное устройство управления содержит преобразователь начального адреса, мультиплексор условий, первый и второй мультиплексоры адреса, блок памяти микропрограмм, регистр микрокоманд, в котором выделены поле адреса перехода, поле кода условия, поле управления, поле признака конца микропрограммы, регистр текущего адреса, инкрементатор, блок управления восстановлением, содержащий с четвертого по пятый элементы И, второй счетчик, дешифратор, мультиплексор, RS- и I К-триггеры, блок формирования точек возврата, содержащий с первого по третий элементы И, элемент ИЛИ, первый и второй буферные регистры, первый счетчик и схему управления, блок памяти точек возврата. В регистре микрокоманд дополнительно введены поле кода восстановления и поле формирования точки возврата, что позволяет повысить надежность восстановления после сбоя за счет обеспечения возможности выполнения повторных процедур возврата к точкам восстановления с увеличением глубины восстановления, 5 ил, & о OS & 00 Јь сд

этом начальный адрес микрокоманды по- помещается логическая единица, котоявляется на выходе второго мультиплексора 20 адреса и поступает на вход блока 4 памяти микропрограмм для выбора соответствующей микрокоманды и на информационный вход регистра 10 текущего адреса. С выхода блока 4 памяти микропрограмм выбранная микрокоманда поступает на информационный вход регистра 5 микрокоманд. Запись микрокоманды в регистр 5 микрокоманд и запись соответствующего ей адреса в регистр 10 текущего адреса осуществляется импульсом второй синхронизирующей серии, поступающей с первого входа устройства 14 на синхронизирующие входы регистра 5 микрокоманд и регистра 10 текущего адреса, с выхода которого адрес поступает на вход инкрементатора 11, где осуществляется формирование адреса следующей микрокоманды путем подсуммирования единицы. Дцрес следующей микрокоманды с выхода инкрементатора 1 1 поступает на первый информационный вход первого мультиплексора 3 адреса. Если текущей микрокоманде соответствует микрокоманда Продолжить., то в поле 7 кода условия регистра 5 микрокоманд задается код, соответствующий анализу внешнего условия этой микроинструкции, что обеспечивает появление на выходе мультиплексора 2 условий логического сигнала, разрешающего появление на выходе первого мультиплексора 3 адреса, соответствующего адресу следующей микрокоманды, с выхода инкрементатора 11. При выполнении микрокоманды условного перехода в поле 7 кода условия регистра 5 микрокоманд помещается код, соответствующий анализу внешнего условия перехода, что обеспечивает появление на выходе мультиплексора 2 условий логического сигнала, разрешающего появление на

0

5

0

5

0

5

0

5

рая. поступает на первый вход первого элемента И 3 блока 18 формирования точек возврата и при появлении на втором его входе фронта первой син- хросерии, осуществляет запись в блок 19 памяти точек возврата по адресу, содержащемуся в счетчике 26 блока 18 формирования точек возврата. Увеличение содержимого счетчика на единицу происходит при переходе устройства к выполнению следующей микрокоманды, признак формирования точек возврата который равен нулю. При возникновении сбоя с третьего входа устройства , 23 сигнал Ошибка поступает на третий управляющий вход блока 8 формирования точек возврата, во втором регистре 29 которого фиксируется код соответствующего адреса и на второй управляющий вход блока 17 управления восстановлением, где осуществляется перевод первого триггера 37 в сбстоя- ние логической единицы, что обеспечивает появление на первом выходе блока 17 управления восстановлением кода, соответствующего избранному способу восстановления. Код восстановления поступает с выхода поля 21 кода восстановления регистра 5 микрокоманд на третий управляющий вход блока 17 управления восстановлением и далее на информационный вход счетчика 34, запись в который осуществляется по появлению признака наличия ошибки с выхода схемы 27 сравнения блока 18 формирования точек возврата с выхода счетчика 34, код восстановления поступает на вход дешифратора 35, выходные сигналы которО2 о обеспечивают управление восстановлением микропрограммы при повторении сбоев. Процедура восстановления микрокоманды завершается переводом первого триггера 37 блока 17 управления восстановлением

10

20

в состояние логического нуля, которое осуществляется синхронно с импульсом второй синхросерии. Если при восстановлении после первого сбоя кодом возврата был избран метод повтора сбойной микрокоманды, то в счетчик блока 17 управления восстановлением будет занесен код (ll), позволяющий выполнить переход по адресу из регистра 10 текущего адреса. При повторном сбое содержимое счетчика 34 блока 17 управления восстановлением уменьшается на единицу, что обеспечивает переход по адресу, выб- jc ранному из блока 19 памяти точек возврата. При каждом последующем сбое -. содержимое счетчика 26 блока 18 формирования точек возврата по сигналу Ошибка, проходящему через открытый второй элемент И 32, уменьшается на единицу„ что обеспечивает выбор предыдущей точки возврата, При восстановлении из последней точки возврата с выхода многовходового элемента ИЛИ 25 30 блока 18 формирования точек возврата на первый управляющий вход блока 17 управления восстановлением и далее на третий вход третьего элемента И 4I поступает уровень логической единицы, JQ который при появлении поступающей ошибки позволяет произвести установку второго триггера 38 блока 17 управления восстановлением в состояние логической единицы, которое поступает на второй выход блока 25 устройства и представляет собой запрос на останов по ошибке, При успешном завершении процедуры восстановления, когда текущий адрес микрокоманды превысил адрес сбоя, хранящийся во втором гистре 29 блока 18 формирования точек возврата на выходе схемы 27 сравнения уровень логической единицы переходит в состояние логического нуля, при этом в счетчик 26 заносится код номера точки возврата, хранящийся в первом регистре 28 блока 18 формирования точек возврата. Эта операция завершает процедуру восстановления после сбоя, что определяет переход всех элементов управления восстановлением в исходное состояние и обеспечивает возможность формирования последующих точек возврата в соответствии, с алгоритмом микропрограммы, Формула изобретения Микропрограммное устройство управления, содержащее блок памяти микро16368458

программ, преобразователь начального

35

40

45

50

55

адреса, первый и второй мультиплексоры адреса, регистр микрокоманд, мультиплексор условий, регистр текущего адреса, инкрементатор, причем вход начального адреса устройства соединен с информационным входом преобразователя начального адреса, выход которого соединен с выходом поля адреса перехода регистра микрокоманд и с первым информационным входом первого мультиплексора адреса, выход которого соединен с первым информационным входом второго мультиплексора адреса, выход которого соединен с информационным входом регистра текущего адреса и с адресным входом-блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля условий которого соединен с управляющим входом мультиплексора условий, вход условий устройства соединен с информа ционным входом мультиплексора условий выход которого соединен с управляющим входом первого мультиплексора адреса, второй информационный вход которого соединен с выходом инкрементатора, вы ход регистра текущего адреса соединен с входом инкрементатора и с вторым информационным входом второго мультиплексора адреса, первый вход синхрони зации устройства соединен с входом синхронизации регистра текущего адреса и регистра микрокоманд, выход приз нака Конец микропрограммы которого соединен с входами управления третьим состоянием преобразователя начального адреса и регистра микрокоманд, выход поля микроопераций которого соединен с выходом микроопераций устройства, отличающееся тем, что, с целью повышения отказоустойчивости ра боты устройства за счет реализации повторного выполнения сбойных микрокоманд, оно дополнительно содержит блок памяти точек возврата, первый и второй буферные регистры, схему сравнения, элемент ИЛИ, с первого по шестой элементы И, первый и второй счетчики, дешифратор, мультиплексор, RS- триггер, и lK-тригтер, причем вход установки устройства соединен с входом установки в О RS, I К-триггеров и регистра микрокоманд, выход признака формирования точек возврата которого соединен с первыми входами пер вого и второго элементов И, выходы

10

20

jc 25JQ

35

40

45

50

55

адреса, первый и второй мультиплексоры адреса, регистр микрокоманд, мультиплексор условий, регистр текущего адреса, инкрементатор, причем вход начального адреса устройства соединен с информационным входом преобразователя начального адреса, выход которого соединен с выходом поля адреса перехода регистра микрокоманд и с первым информационным входом первого мультиплексора адреса, выход которого соединен с первым информационным входом второго мультиплексора адреса, выход которого соединен с информационным входом регистра текущего адреса и с адресным входом-блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля условий которого соединен с управляющим входом мультиплексора условий, вход условий устройства соединен с информационным входом мультиплексора условий, выход которого соединен с управляющим входом первого мультиплексора адреса, второй информационный вход которого соединен с выходом инкрементатора, выход регистра текущего адреса соединен с входом инкрементатора и с вторым информационным входом второго мультиплексора адреса, первый вход синхронизации устройства соединен с входом синхронизации регистра текущего адреса и регистра микрокоманд, выход признака Конец микропрограммы которого соединен с входами управления третьим состоянием преобразователя начального адреса и регистра микрокоманд, выход поля микроопераций которого соединен с выходом микроопераций устройства, отличающееся тем, что, с целью повышения отказоустойчивости работы устройства за счет реализации повторного выполнения сбойных микрокоманд, оно дополнительно содержит блок памяти точек возврата, первый и второй буферные регистры, схему сравнения, элемент ИЛИ, с первого по шестой элементы И, первый и второй счетчики, дешифратор, мультиплексор, RS- триггер, и lK-тригтер, причем вход установки устройства соединен с входом установки в О RS, I К-триггеров и регистра микрокоманд, выход признака формирования точек возврата которого соединен с первыми входами первого и второго элементов И, выходы

которых соединены соответственно с входом записи-чтения блока памяти точек возврата и с входом прибавления единицы первого счетчика, информационные выходы которого соединены с входами элемента ИЛИ адресным входом блока памяти точек возврата, информационным входом первого буферного регистра, выход которого соединен с информационным входом первого счетчика, выход регистра текущего адреса соединен с первым входом схемы сравнения, информационным входом второго буферного регистра, информационным входом блока памяти точек возврата, выход которого соединен с третьим информационным входом второго мультиплексора адреса, вход ошибки устройства соединен с первыми входами с третьего по шестой элементов и, входом синхронизации второго буферного регистра , входом установки в 1 I К триггера, выход которого соединен со своим К-входом и с управляющим входом мультиплексора, выход которого соединен с управляющим входом второго мультиплексора адреса, второй вход синхронизации устройства соединен с вторым входом первого элемента И, выход признака Конец микропрограммы регистра микрокоманд соединен с входами установки в О первого и второго буферных регистров, первого и второго счетчиков, выход второго бу

ферного регистра соединен с вторым входом схемы сравнения, выход кото- , рой соединен с входом записи первого счетчика, вторым входом второго элемента И, третьим входом первого элемента И и с входом синхронизации первого буферного регистра, выход поля кода восстановления регистра микрокоманд соединен с информационным входом второго счетчика, информационный выход которого соединен с первым информационным входом мультиплексора и с входом дешифратора, первый выход которого соединен с вторыми входами третьего и пятого элементов И, выходы которых соединены соответственно с входом вычитания единицы первого счетчика и с входом записи второго счетчика, вы0 ход элемента ИЛИ соединен с вторым входом шестого элемента И, выход которого соединен с входом установки в 1 RS-триггера, выход которого соединен с входом индикации отказа устрой5 ства, первый вход синхронизации устройства соединен с входом синхронизации IK-триггера, второй и третий выходы дешифратора соединены соответственно с третьим входом шестого элемен0 та И и с вторым входом четвертого элемента И, выход которого соединен с входом вычитания единицы второго счетчика, второй информационный вход мультиплексора подключен к потенциалу логического нуля устройства.

s

(jfafleQ

Фиг А

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Булгаков С.С | |||

| и др | |||

| Проектирование цифровых схем на комплектах микро- программируемых БИС | |||

| -М.: Радио и связь, 1984, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-03-23—Публикация

1989-03-23—Подача