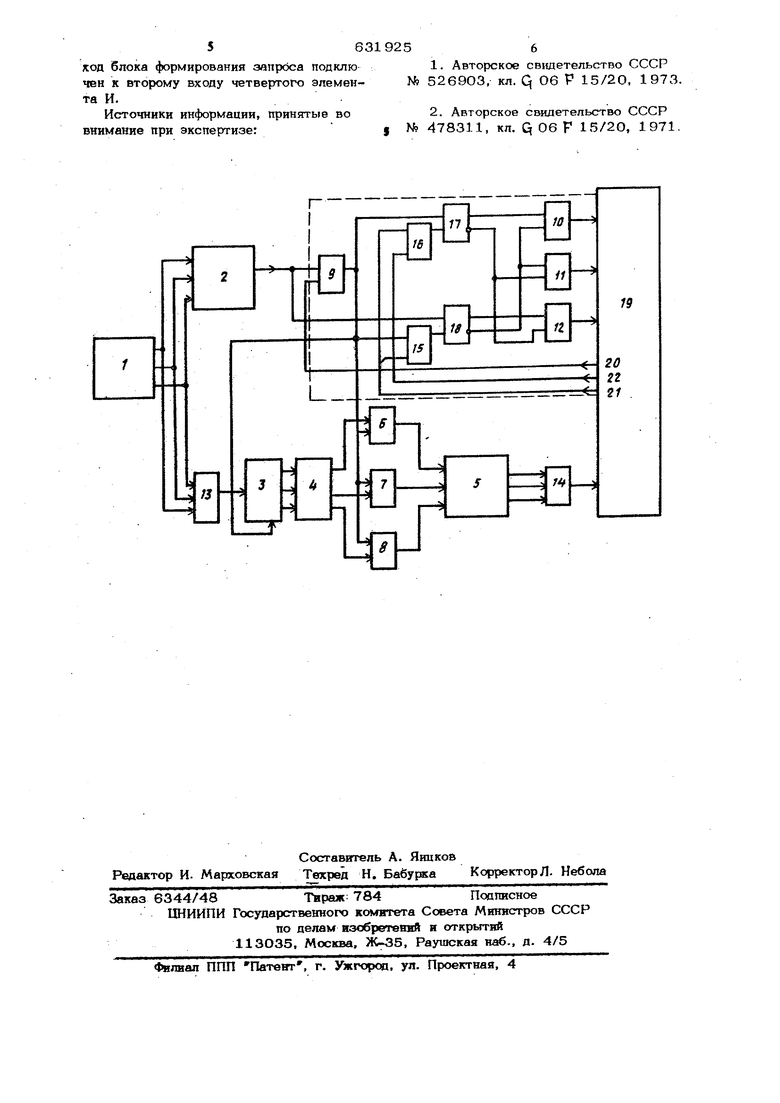

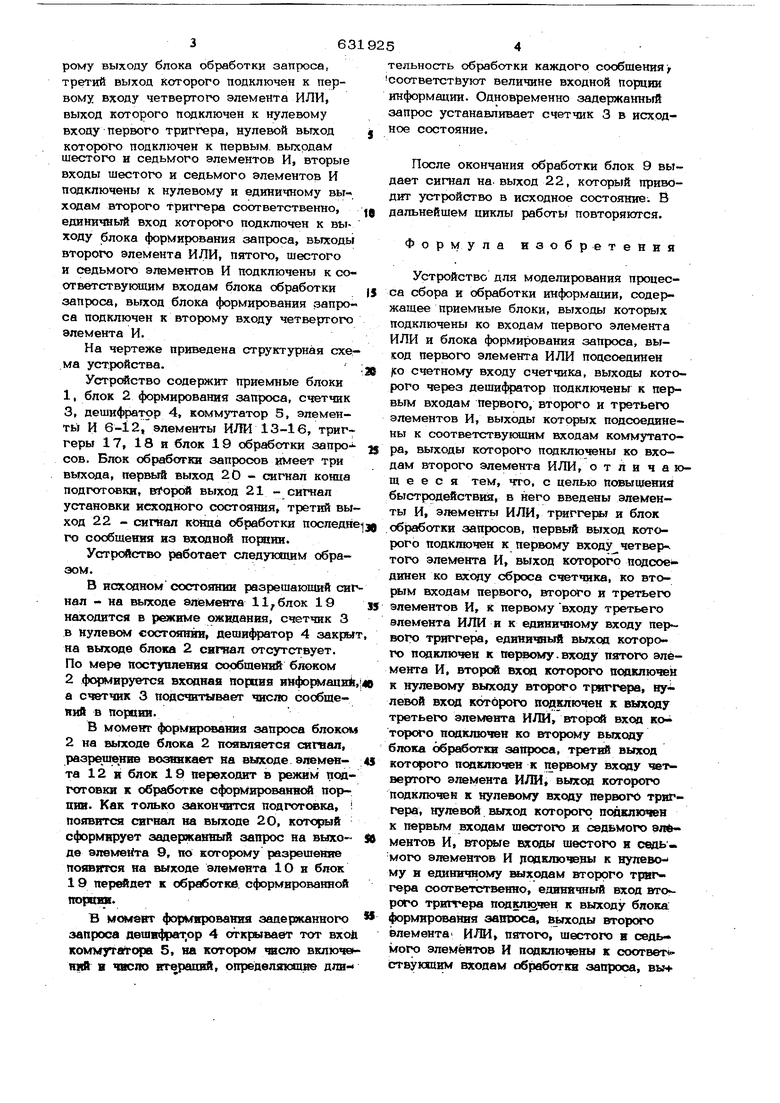

рому выходу блока обработки запроса, третий выход которого подключен к первому входу четвертого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, нулевой выход которого подключен к первым, выходам шестого и седьмого элементов И, вторые входы шестого и седьмого элементов И подключены к нулевому и единичному выходам второго триггера соответственно, единичный вход которого подключен к выходу блока формирования запроса, выходы второго элемента ИЛИ, пятого, шестого и седьмого элементов И подключены к соответствующим входам блока обработки запроса, вьгход блока формирования запроса подключен к второму входу четвертого элемента И. На чертеже приведена структурная схема устройства. Устройство содержит приемные блоки 1, блок 2 формирования запроса, счетчик 3, дешифратор 4, коммутатор 5, элементы И 6-12, элементы ИЛИ 13-16, триггеры 17, 18 и блок 19 обработки запро- сов. Блок обработки запросов имеет три выхода, первый выход 20 - сигнал конца подготовки, в орсйй выход 21 - сигнал установки исходного состояния, третий вы ход 22 - сигнал конца обработки последне го сообщения из входной порции. Устройство работает следутоошм образом. В исходном состоянии разрешающий сиг нал - на выходе алёмевта 11 блок 19 находится в режиме ожидания, счетчик 3 в нулевом состоянии, дешифратор 4 закры на выхсще блока 2 снгнал отсутствует. По мере поступления сообщений блоком 2 формируется входная порция имфо{и аиий а счетчик 3 подсчитывает число сообщений в порции. В мометгг формирования запроса блоком 2 на выходе блока 2 появляется сипаал, разрешение возникает на выходе элемента 12 и блок 19 переходит в резким подготовки к обработке сфор лнрованжЛ порции. Как только закон штся подготсжка, ПО1ГОИТСЯ сигаал на выходе 2 О, который сформирует задержанный запрос на выходе апемейта 9, по которому разрешение появятся на выходе элемента 10 и блок 19 к обработке, сформированной ПО{Л11Ш. в момент формвроваташ задермсанного запроса дешиф|)атор 4 открывает тот вхо коммутатора 5, на котором тасло включе ннй в число итераций, определяхзшие длиельность обработки каждого сообщения; оответствуют величине входной порции нформации. Одновременно задержанный апрос устанавливает счетчик 3 в исхрдое состояние. После окончания обработки блок 9 выает сигнал на выход 22, который привоит устройство в исходное состояние. В альнейшем циклы работы повторяются. изобретения Устройство для моделирования процесса сбора и обработки информации, содержашее приемные блоки, выходы которых подключены ко входам первого элемента ИЛИ и блока формирования запроса, выкод первого элемента ИЛИ подсоединен (СО счетному входу счетчика, выходы которого через дешифратор подключены к первым входам первого, второго и третьего элементов И, выходы которых подсоединены к соответствующим входам коммутатора, выходы которого подключены ко входам второго элемента ИЛИ, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействи:я, в него введены элементы И, элементы ИЛИ, триггеры и блок обработки запросов, первый выход которого подключен к первому входу четвер того элемента И, выход которого подсоединен ко входу сброса счетчика, ко вторым входам первого, второго и третьего элементов И, к первому входу третьего элемента ИЛИ и к единичному входу первого триггера, единичный выхса которого подключен к первому. входу пятого элемента И, второй вхш которого подключи к нулевому выходу втсфого триггера, нулевой вход которого подключен к выходу третьего элемента ИЛИ, второй вход ко торого поаключен ко второму выходу блока запроса, третий выход которого поаключен к первому входу четвертого элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, нулевой выход которого попключев к первым входам шестого и седьмого элементов И, еторие входы шестого н седь. мого элементов И роаключены к HyneBoму и единичному выходам второго триггера соответственно, единичный вход вто рого триггера подкл15чен к выходу блока формирования запроса, выходы второго элемента ИЛИ пятого, шестого н седьмого элементов И подключены к соответ ствуюшим входам обработки aattpcxe, вьн56319256

лод блока формирования запроса подклю1. Авторское сввдетельство СССР

чей к второму входу четвертого элемен-hfe 526903, кл, G 06 Р 15/20, 1973

та И..

Источники информации, принятые во2. Авторское свидетельство СССР

внимание при экспертизе:j ) 478311, кл. Q 06 Г 15/2О, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 2000 |

|

RU2182359C2 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1987 |

|

SU1515165A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

Авторы

Даты

1978-11-05—Публикация

1977-04-05—Подача