проверяемого узла, причем первый управляющий вход блока соединен с первыми управляющими входами узлов, первые информационные входы которых соединены .с первым информационным входом блока, вторые управляющие вхсэды узлов соединены соответственно с группой управляющих входов блока, вторые информационные входы которого соединены соответственно с вторыми информационными входами узлов.

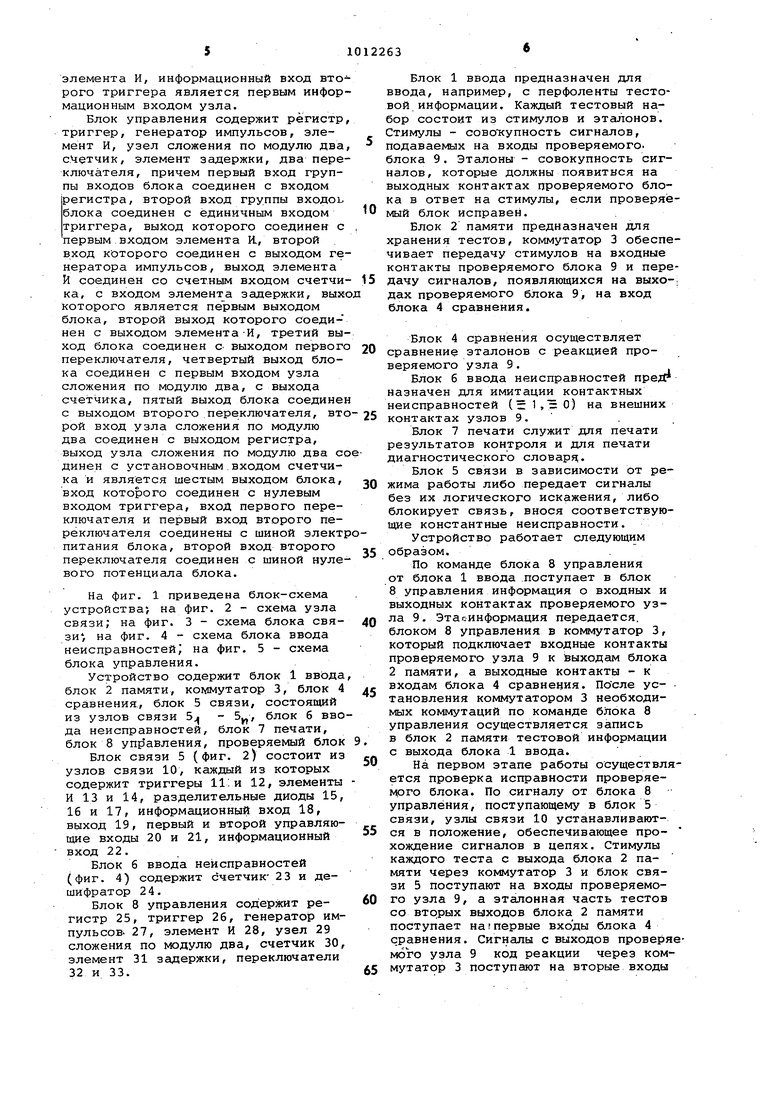

4. Устройство по п. 3, о т л и ч а То щ е :е с я тем,, что узел связи содержит два триггера, два элемента И, три разделительных диода, причем прямой выход первого триггера соединен с первым входом первого элемента И, второй вход которого соединен с катодом первого разделит тельного диода и является вторым информационным входом узла, анод первого разделительного диода соединен с катодом второго разделительного диода, с катодом третьего раз.дёлительного диода и является выходом узла, аноды второго и третьего разделительных диодов соединены соответственно с выходами первого и второго элементов И, первый вход второго элемента И соединен с инверсным выходом первого триггера, единичный вход которого является первым управляющим входом узла, второй управляюс щий вход которого соединен с нулевым входом первого триггера и с синхровходом второго триггера, прямой выход которого соединен с вторым входрм второго элемента И, информа ционный йход второго триггера явля ется первым.информационным входом узла.

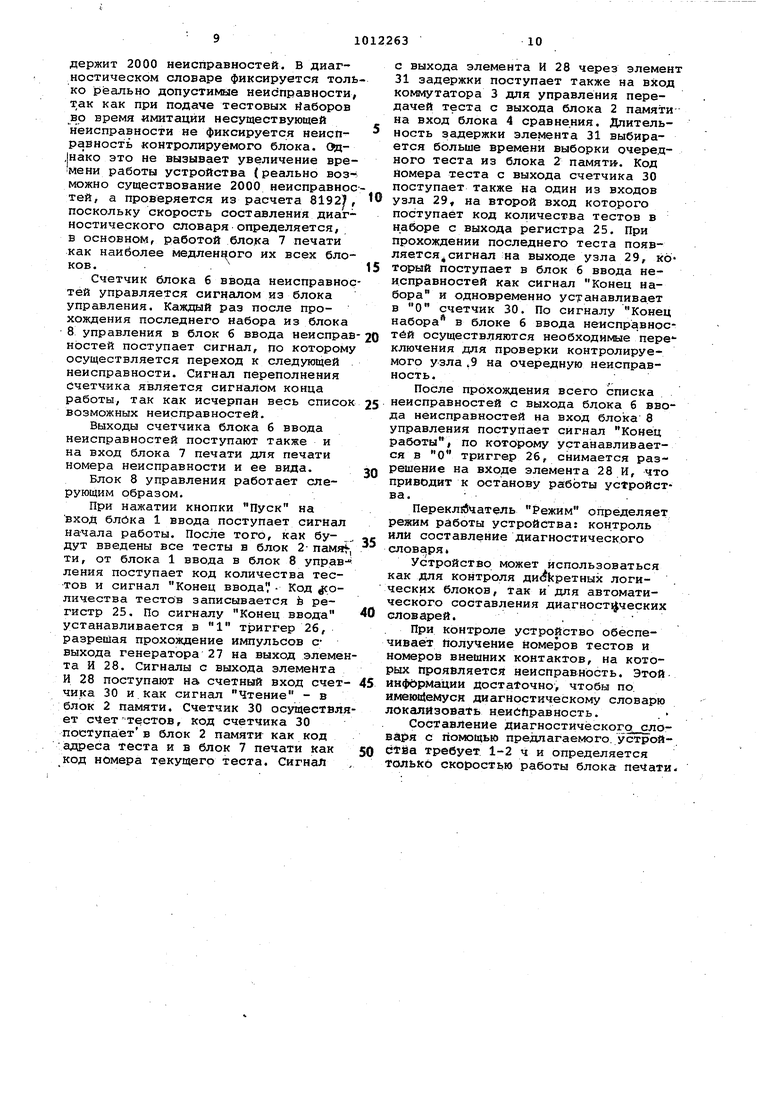

5. Устройство по п. 1, отличаю щ е е с я тем, что блок управления содержит регистр, триггер, генератор импульсов, элемент И, узел сложения по модулю два, счетчик, v элемент задержки, два переключателя, причем первый вход группы входов блока соединен с входом регистра, второй вход группы входов блока соединен с единичным входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И соеди- нен CfO счетным входом счетчика, с входом- элемента за держки, выход которого является первым выходом блока, второй выход которого соединен с выходом элемента И, третий выход блока соединенс выходом первого переключателя, четвертый выход блока соединен с первым- входом узла сложения по модулю два, с выходом счётчика, пятый выход блока соединен с выходом второго переключателя, второй вход узла сложения по модулю два соединен с выходом регистра, выход узла сложения по модулю два соединен с установочным входом счетчика и является шестым выходом блока, вход которого соединен с нулевым входом триггера, вход первого переключателя и первый вход второго . переключателя соединены с шиной электропитания блока, второй вход второго переключателя соединен с шиной нулевого потенциала блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Устройство для приема и отображения информации | 1980 |

|

SU955161A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ, содержащее блок ввода, блок Пс1мяти, коммутатор, блок сравнения, блок печати, блок управ-. ления, причем первый выход блока ввода соединен с информационным входом блока памятиj первая группа выходов которого соединена с первой группой информационных входов коммутатора, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с управляющим входом блока памяти, группа выходов блока ввода соединена с группой входов блока . управления, третий выход которого соединен с управляющим входом блока ввода, четвертый выход блока управления соединен с первым управляющим входом блока печати, второй управляющий вход которого соединен, с выходом блока сравнения, первая группа входов которого соединена с второй группой выходов блока памяти, вторая группа входов блока сравнения соединена с -первой группой выходов коммутатора, вторая группа выходов которого соединена соответственно с группой входов проверяемого узла, группа выходов которого соединена С второй группой входов коммутатора, отлич ающее ся тем, что, с целью повышения быстродействия, в устройство введен блок ввода неисправностей, блок связи, причем пятый выход блока управления соединен с первым управляющим входом блока ввода неисправностей, с первым управ ляющим входом блока связи, группа управляющих входов которого соединена соответственно с группой управг ляющих выходов блока ввода неисправностей, информационный выход которого соединен с первым информационным входом блока связи, группа выходов которого соединена соответственно с входами проверяемого уэла, выходы которого соединены с вторымиинформационными входамиблока связи, шестой выход блока управления соединен с вторым управлякщим входом блока ввода неисправностей, управляющий выход которого соединен с входом (Л блока управления, группа информационных выходов блока ввода неисправностей соеда1нена с группой информационных входов блока памяти. 2.Устройство по п. 1, о т л и - ; чающееся тем, что блок ввода неисправностей содержит счетчик и ,дешифратор, группа выходов которогсУ является группой управляющих выходов блока, группа информационных выходов ю к которого соединена соответственно с выходами разрядов счетчика, выход Oiпервого разряда счетчика является информационным выходом блока, управСлд ляющий выход которого соединен с выходом переноса счетчика, управляющий вход которого соединен с установочным входом счетчика и является первым управляющим входом блока, второй управляющий вход которого соединен со счетным входом счетчика, выходы счетчика с второго по п-й (где п - число разрядов счетчика) соединены соответственно с входами дешифратора. 3.Устройство по п. 1, отличающееся тем, что влок связи содержит узлы связи по числу выводрв.1

Изобретение относится к области цифровой вычислительной техники и может быть, использовано для контроля цифровых логических узлов и для автоматического составления диагностических словарей на этапе разработки тестов. .

Известно устройство для контроля | цифровых модулей и проверки качества тестов,которое содержит генератор псевдослучайных последовательностей, блоки сравнения, имитаторы неисправностей, блоки управления, регистр результатов, регистр длины тестов, контактный блок и позволяет оценить качество тестов путем сравнения рёакции заведомо исправной интегральной схемы из состава контролируемого модуля с реакцией эталонной интеграль

ной схемы путем внесения в последнюю фиксированных неисправностей, t.

Однако известное устройство не обеспечивает получение информации, необходимой для Составления диагностического словаря, так как в нем не фиксируется проявление вносимой неисправности на внешних контактах контролируемого модуля, а только оценивается ре.акция на выходах интегргшьной схемы, являющейся внутренним узлом контролируемого модуля.

Наиболее близким к предложенному является устройство для контроля циф ровых блоков, которое содержит блок ввода, выходы которого соединены с входом блока управления и блока памяти, первый и второй выходы которого соединены соответственно с первыми входами коммутатора и блока сравнения, второй вход которого подключен к первому выходу коммутатора, второ вход и второй выход которого являются входами и выходами устройства, и обеспечивает контроль цифровых ло гических блоков путем наблюденная ре акции контролируемого блока на вход-ные воздействия. С помощью этого устройства можно составлять диагност ческие словари, внося вручную неисправности в проверяемый блок (например, отпаивая соотгветствующую цепь и подключая ее к источнику логическо го нуля или единицы} 2. Однако составление диагностических словарей ручным способом требует больших затрат и времени и, кроме того, многократные перепайки в блоке могут привести к выходу его из .строя.. . .. - , ; - , Цель изобретения - повышение быст родейгствия. Поставленная цель достигается тем то в устройство для контроля цифровых /УЗЛОВ, содержащее ёлок ввода, блок памяти, коммутатор, блок срав нения, блок печати, блок управления причем первый выход блока ввода сое динен с информационным входом блока памяти, первая группа выходов которого с;ре динен ас пер,вой группой информационных входов коммутатора, управляющий вход которого соединен .ё первым выходом бл6к:а управления, .второй выход которого соединен с управляющим входом блока памяти, труппа выходов блока ввода соединена с группой входов блока управления, третий выкод Kotoporo соединен е управляющим входом блока.ввода, четвертый выход блока управления сое динен с первым управляющим .входом блока печати, второй управляквдий вход которого соединен с выходом блока сравнения, первая группа входов которого соединена с второй . группой выходов блока памяти, вторая группа входов блока сравнения соединена с первой группой выходов коммутатора, вторая группа выходов которого соединена соответственно с группой входов проверяемого узла, группа выходов которого соединена с второй группой входов коммутатора введен блок ввода неисправностей, блок связи причем пятый выход блока управления соединен с первым управляющим входом блока ввода неисправнвстей, с первым управляющим входом блока связи, группа управляющих входов которого соединена соответств но с группой .управляющих выходов блока ввода неисправностей, информационный выход которого соединен с ;первым информационным входом блока связи, группа выходов которого соединена соответственно с входами проверяемого узла, выходы которого сое-. дине;ны с вторыми информационными входами блока связи, шестой выход блока-управления соединен с вторым управляющим входом блока ввода неисправностей, управлякмций выход которого соединен с входом блока управления, группа информационных выходов блока ввода неисправностей соединена с группой информационных входов блока Ьамяти. . Блок ввода неисправностей содержит счетчик и дешифратор, группа выходов KOTopoixj является группой , управлякнцих выходов блока, группа информационных выходов которого соединена соответственно с выходами разрядов счетчика, выход первого разряда счетчика является информационным выходом блока, управляющий выход которого соединен с выходом переноса счетчика, управляющий вход которого соединен с установочным , входом счетчика и является первым управляющим входом блока, второй управляющий вход которого соединен со счетным входом счетчика, выходы счетчика с второго по п-й (где«п число разрядов счетчика) соединены v соответственно с входами д 1Шфратор 1. Блок связи узлы связи по числу выводов проверяемого узла, причем первый управляющий вход- блока соединен с первыми управляющими входами узлов, первые информационные входы которых соединены с первы- . м информационным. входом блока, вторые управляющие входы узлов соединены соответственно с группой управляющих входов блока, втЬрые информационные входы которого соединены Соответственно с вторыми информационными входами узлов. Узел связи содержит два триггера, два элемента И, три разделительных диода, причем прямой выход первого триггера соединен с первым Sxo-: дом первого элемента.и, второй вход которого соединен с катодом первого разделительного диода и является вторым информационным входом узла, анод первого разделительного диода соединен с катодом второго раздели-тельного диода, с катодом третьего разделительного Диода и является выходом узла, аноды второго и третьего разделительных диодов соединены с. выходами первого и второго элементов И, первый вход второго элемента И соединен с инверсным выходом первого триггера, единичный вход которого является первым управЛяюадам входом узла, ВТОРОЙ управляющий вход которого соединен с нулевым вход«м первого триггера и с с инхровхсдом второго триггера, прямой выход котов рого соединен с вторым входом второго ,

элемента И, информационный вход второго триггера является первым информационным входом узла.

Блок управления содержит регистр, триггер, генератор импульсов, элемент И, узел сложения по модулю два, сметчик, элемент задержки, два переключателя, причем первый вход группы входов блока соединен с входом регистра/ второй вход группы входоь блока соединен с единичным входом триггера, выход которого соединен с первым входом элемента К, второй вход которого соединен с выходом генератора импульсов, выход элемента И соединен со счетным входом счетчика, с входом элемента задержки, выхо которого является первым выходом блока, второй выход которого соединен с выходом элемента-И, третий выход блока соединен с- выходом первого переключателя, четвертый выход блока соединен с первым входом узла сложения по модулю два, с выхода счетчика, пятый выход блока соединен с выходом второго переключателя, вто рой вход узла сложения по модулю два соединен с выходом регистра, выход узла сложения по модулю два со динен с установочным входом счетчика и является шестым выходом блока, вход которого соединен с нулевым входом триггера, вход первого переключателя и первый вход второго переключателя соединены с шиной электрпитания блока, второй вход второго

переключателя соединен с шиной нулевого потенциала блока.

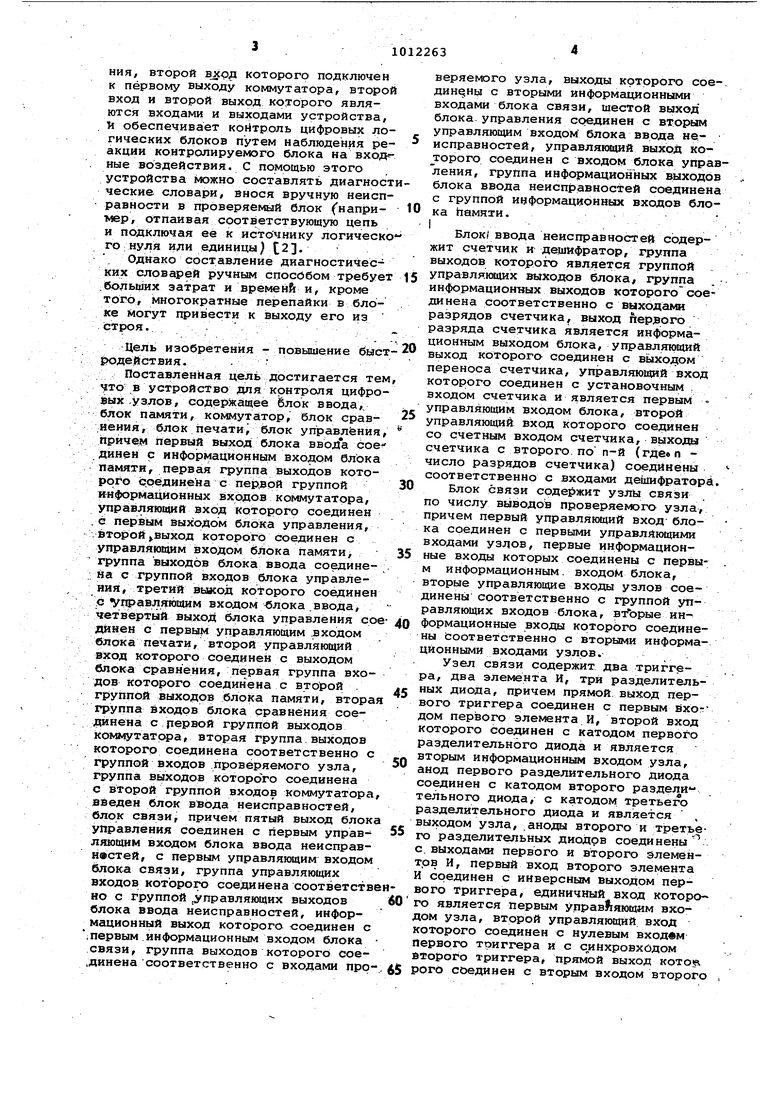

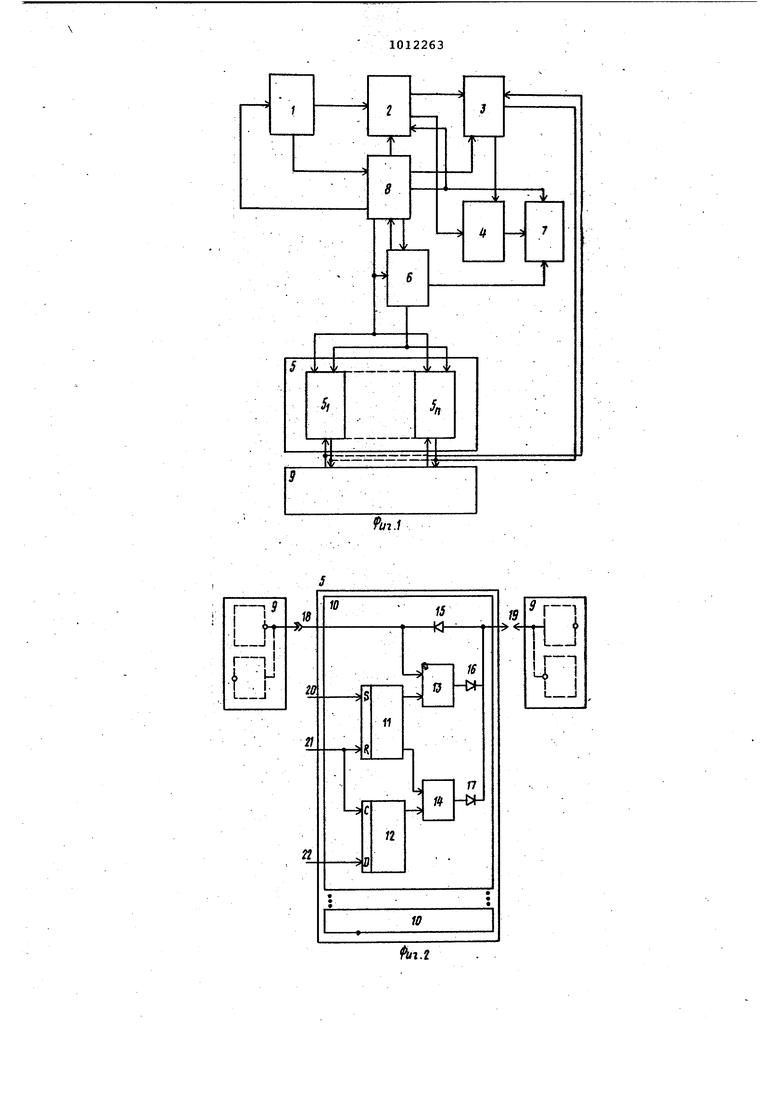

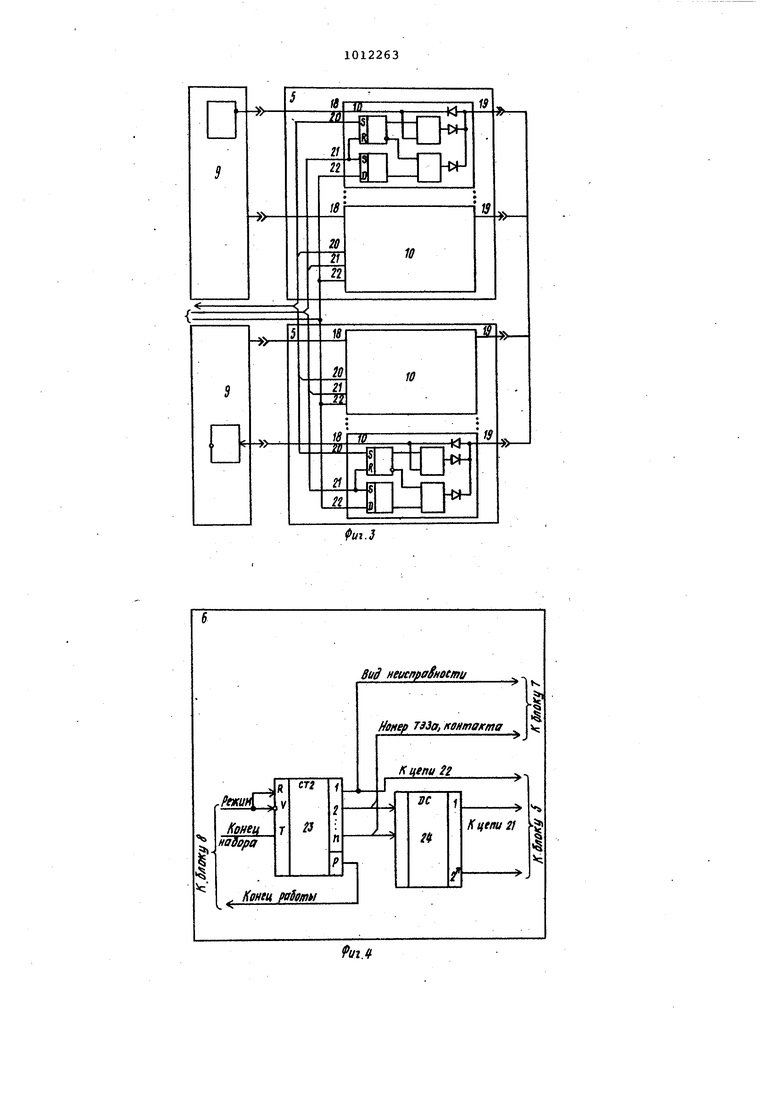

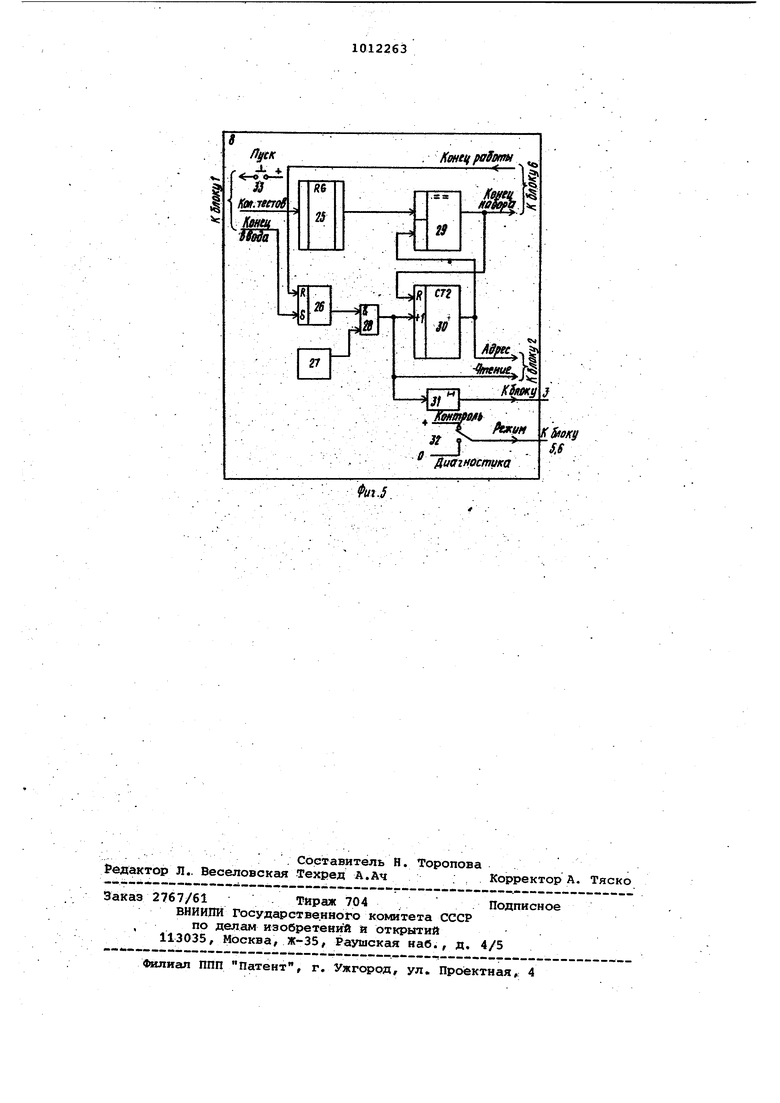

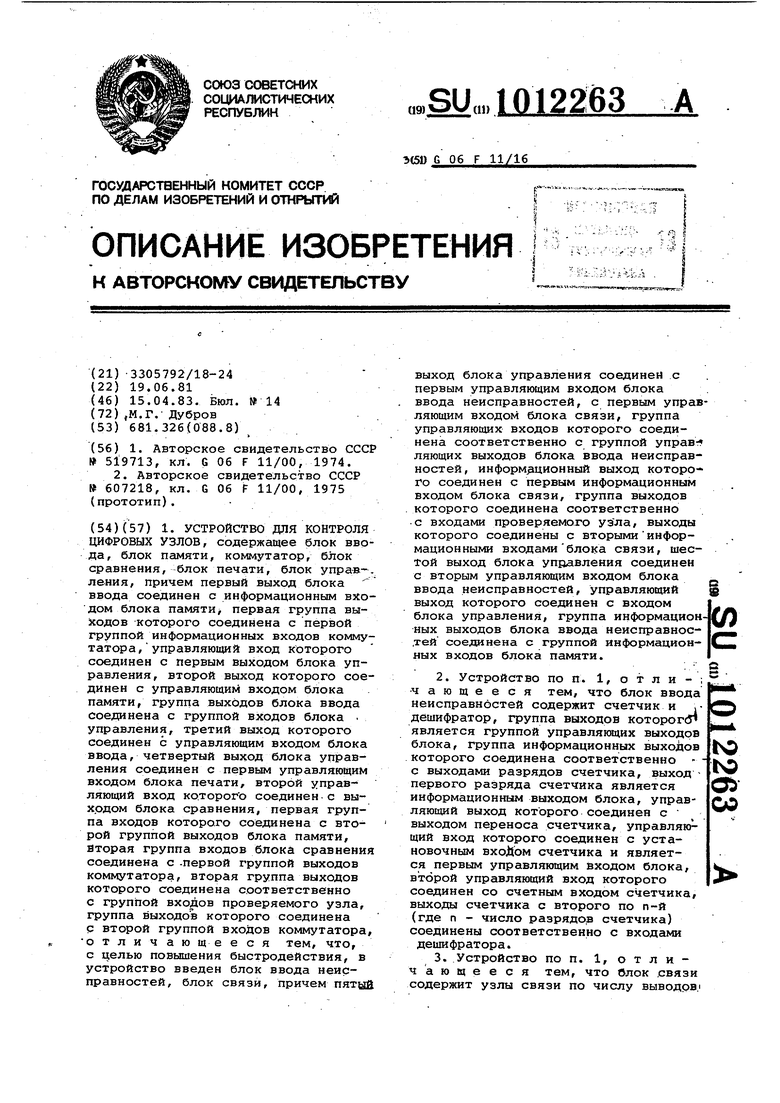

На фиг. 1 приведена блок-схема устройства, на фиг. 2 - схема узла связи; на фиг. 3 - схема блока связи, на фиг. 4 - схема блока ввода неисправностей; на фиг. 5 - схема блока управления.

Устройство содержит блок 1 ввода блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 связи, состоящий из узлов связи 5 - 5, блок б ввода неисправностей, блок 7 печати, блок 8 упЕ5авления, проверяемый блок

Блок связи 5 (фиг. 2) состоит из узлов связи 10, каждый из которых содержит триггеры 11.и 12, элементы И 13 и 14, разделительные диоды 15, 16 и 17, информационный вход 18, выход 19, первый и второй управляющие входы 20 и 21, информационный вход 22.

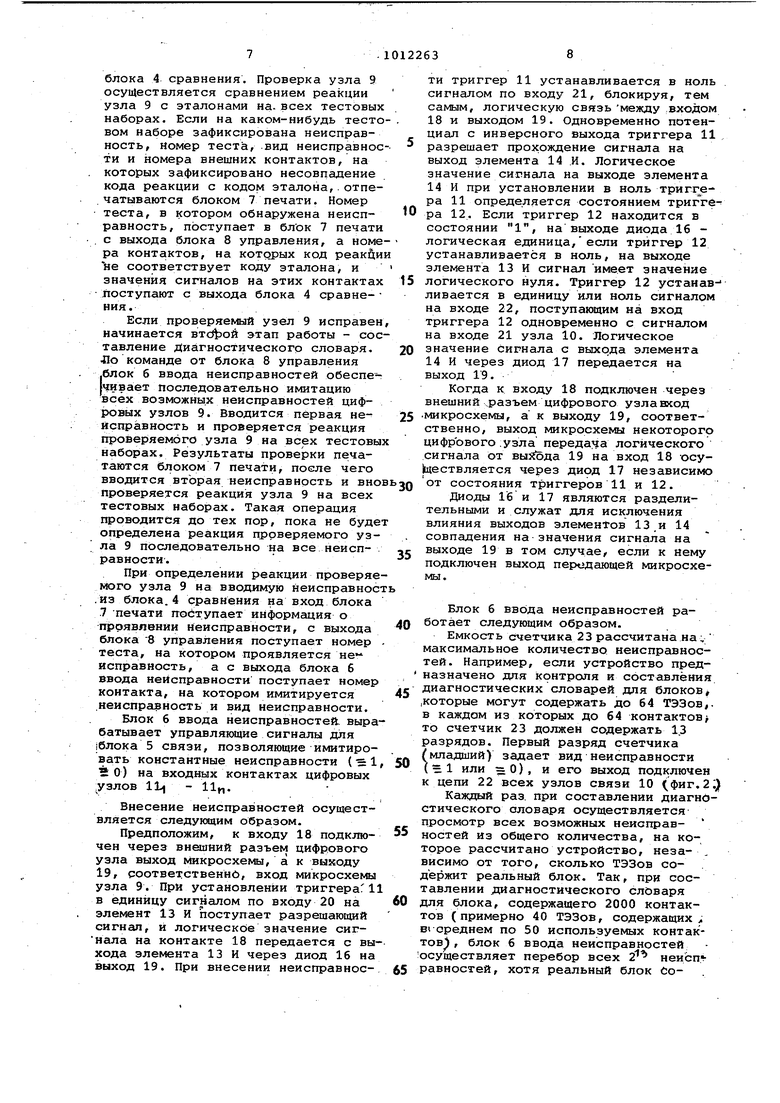

Блок 6 ввода неисправностей (фиг. 4) содержит счетчик- 23 и дешифратор 24.

Блок 8 управления содержит регистр 25, триггер 26, генератор импульсов- 27, элемент И 28, узел 29 сложения по модулю два, счетчик 30, элемент 31 задержки, переключатели 32 и 33.

Блок 1 ввода предназначен для ввода, например, с перфоленты тестовой информации. Каждый тестовый набор состоит из стимулов и эталонов. Стимулы - совокупность сигналов, подаваемых на входы проверяемого, блока 9. Эталоны - совокупность сигналов, которые должны появиться на выходных контактах проверяемого блока в ответ на стимулы, если проверямый блок исправен.

Блок 2 памяти предназначен для хранения тестов, коммутатор 3 обеспчивает передачу стимулов на входные контакты проверяемого блока 9 и пердачу сигналов, появляющихся на выхо дах проверяемого блока 9, на вход блока 4 сравнения.

Блок 4 сравнения осуществляет сравнение эталонов с реакцией проверяемого узла 9.

Блок 6 ввода неисправностей преД Назначен для имитации контактных неисправностей ( 1, 0) на внешних контактах узлов 9.

Блок 7 печати служит для печати результатов контроля и для печати диагностического словар.

Блок 5 связи в зависимости от режима работы либо передает сигналы без их логического искажения, либо блокирует связь, внося соответствующие константные неисправности.

Устройство работает следующим образом..

По команде блока 8 управления от блока 1 ввода поступает в блок 8 управления информация о входных и выходных контактах проверяемого узла 9. Этасинформация передается, блоком 8 управления в ког &лутатор 3, который подключает входные контакты проверяемого узла 9 к выходам блока 2 памяти, а выходные контакты - к входам блока 4 сравнения. После установления коммутатором 3 необходимых коммутаций по команде блока 8 управления осуществляется запись в блок 2 Пс1мяти тестовой информации с выхода блока 1 ввода.

На первом этапе работы осуществлется проверка исправности проверяекрго блока. По сигналу от блока 8 управления, поступающему в блок 5 связи, узлы связи 10 устанавливаются в положение, обеспечивающее прохождение сигналов в цепях. Стимулы каждого теста с выхода блока 2 памяти через коммутатор 3 и блок связи 5 поступают на входы проверяемого узла 9, а эталонная часть тестов со вторых выходов блока 2 памяти поступает нагпервые входы блока 4 сравнения. Сигналы с выходов проверямого узла 9 код реакции через коммутатор 3 поступают на вторые входы блока 4 сравнения. Проверка узла 9 осуществляется сравнением реакции узла 9 с эталонами на. всех тестовых наборах. Если на каком-нибудь тесто вом наборе зафиксирована неисправность, номер теста, .вид неисправное ти и номера внешних контактов, на которых зафиксировано несовпадение кода реакции с кодом эталона,. отпечатываются блоком 7 печати. Номер теста, в котором обнаружена неисправность, поступает в блок 7 печати с выхода блока 8 управления, а номе ра контактов, на которых код реакци не соответствует коду эталона, и значения сигналов на этих контактах лгтоступают с выхода блока 4 сравнения. Если проверяемый узел 9 исправен начинается этап работы - сос тавление Диагностического словаря. По команде от блока 8 управления .блок б ввода неисправностей обеспе чивает последовательно имитацию всех возможных неисправностей цифровых узлов 9. Вводится первая неисправность и проверяется реакция проверяемого узла 9 на всех тестовы наборах. Результаты проверки печатаются блоком 7 печати, после чего вводится вторая неисправность и вно проверяется реакция узла 9 на всех тестовых наборах. Такая операция проводится до тех пор, пока не буде определена реакция проверяемого узла 9 последовательно на все неисправности. При определении реакции проверяе мого узла 9 на вводимую неисправнос .из блока,4 сравнения на вход блока .7 печати поступает информация о проявлении неисправности, с выхода блока 8 управления поступает номер теста, на котором проявляется неисправность, а с выхода блока 6 ввода неисправности поступает номер контакта, на котором имитируется .неисправность и вид неисправности. Блок 6 ввода неисправностей, выра батывает управляющие сигналы для яблока 5 связи, позволяющие-имитировать константные неисправности (1 SO) на входных контактах цифровых .узлов ILj - 11,. Внесение неиспразвностей осуществляется следукяцим образом. Предположим, к входу 18 подключен через внешний разъем цифрового узла выход Микросхемы, а к выходу 19, роответственнй, вход микросхемы узла 9. При установлении триггераГИ в единицу сигналом по входу 20 на элемент 13 И поступает разрешающий сигнал, и логические значение сигнала на контакте 18 передается с вы хода элемента 13 И через диод 16 на выход 19. При внесении неисправноети триггер 11 устанавливается в ноль . сигналом по входу 21, блокируя, тем самым, логическую связь между .входом 18 и выходом 19. Одновременно потенциал с инверсного выхода триггера 11 разрешает прохождение сигнала на выход элемента 14 .И. Логическое значение сигнала на выходе элемента 14 И при установлении в ноль триггера 11 определяется состоянием триггера 12. Если триггер 12 находится в состоянии 1, на выходе диода 16 логическая единица, если триггер 12 устанавливается в ноль, на выходе элемента 13 И сигнал имеет значение логического нуля. Триггер 12 устанавливается в единицу или ноль сигналом на входе 22, поступакндим на вход триггера 12 одновременно с сигналом на входе 21 узла 10. Логическое значение сигнала с выхода элемента 14 И через диод 17 передается на выход 19. Когда к входу 18 подключен через внешний чразъем цифрового узла вход микросхемы, а к выходу 19, соответственно, выход микросхемы некоторого цифрового узла передача логического сигнала от вызйда 19 на вход 18 -осуИествляется через диод 17 независимо от состояния триггеров 11 и 12. Диоды 16 и 17 являются разделительными и служат для исключения влияния выходов элементов 13.и 14 совпадения на значения сигнала на выходе 19 в том случае, если к нему подключен выход передающей микросхемы. Блок б ввода неисправностей работает следующим образом. Емкость счетчика 23 рассчитана на, максимальное количество неисправностей. Например, если устройство предназначено для контроля к составления диагностических словарей для блоков .которые могут содержать до 64 ТЭЗов,. в каждом из которых до 64 контактов то счетчик 23 должен содержать 13 разрядов. Первый разряд счетчика младший) задает виднеисправности ( 1 или О), и его выход подключен к цепи 22 всех узлов связи 10 (фиг.2;} Каждый раз. при составлении диагностического словаря осуществляется просмотр всех возможных неисправностей из общего количества, на которое рассчитано устройство, неза- , висимо от того, сколько ТЭЗов содержит реальный блок. Так, при составлении диагностического словаря для блока, содержащего 2000 контактов ( примерно 40 ТЭЗов, содержащих,. BI-среднем по 50 используемых контактов) , блок 6 ввода неисправностей осуществляет перебор всех 2 неисп.равностей, хотя реальный блок Содержит 2000 неисправностей, В диагностическом словаре фиксируется только реально допустимые неисзправности, т,ак как при подаче тестовых Наборов до время имитации несуществующей неисправности не фиксируется неисправность контролируемого блока. Однако это не вызывает увеличение времени работы устройства (реально возможно существование 2000 неисправностей, а проверяется из расчета 8192), поскольку скорость составления диагностического словаря определяется, в основном, работой блока 7 печати как наиболее медленного их всех блоков.

Счетчик блока 6 ввода неисправностей управляется сигналом из блока управления. Каждый раз после прохождения последнего набора из блока 8 управления в блок б ввода неисправ ностей поступает сигнал, по которому осуществляется переход к следующей . неисправности. Сигнал переполнения счетчика является сигналом конца работы, так как исчерпан весь список возможных неисправностей.

Выходы счетчика блока б ввода неисправностей поступают также и на вход блока 7 печати для печати номера неисправности и ее вида.

Блок 8 управления работает слерующим образом.

При нажатии кнопки Пуск на вход блс5ка 1 ввода поступает сигнал начала работы. После того, как бу- .., дут введены все тесты в блок 2- naMaf, ти, от блока 1 ввода в блок 8 управления поступает код количества тестов и сигнал Конец ввода , Код рличества тестов записывается b регистр 25. По сигналу Конец ввода устанавливается в 1 триггер 26, разрешая прохождение импульсов свыхода генератора 27 на выход элемента И 28. Сигналы с выхода элемента И 28 поступают на счетный вход счетчика 30 и.как сигнал Чтение - в блок 2 памяти. Счетчик 30 осуществляет счгет тестов , код счетчика 30 поступает в блок 2 памяти как код адреса теста и в блок 7 печати как код номера текущего теста. Сигнал

с выхода элемента И 28 через элемент 31 задержки поступает также на вход коммутатора 3 для управления передачей теста с выхода блока 2 памяти на вход блока 4 сравнения. Длительность задержки элемента 31 выбирается больше времени выборки очередного теста из блока 2 памят. Код номера теста с выхода счетчика 30 поступает также на один из входов узла 29 на второй вход которого поступает код количества тестов в наборе с выхода регистра 25. При прохождении последнего теста появляется сигнал на выходе узла 29, который поступает в блок б ввода неисправностей как сигнал Конец набора и одновременно устанавливает в О счетчик 30. По сигналу Конец набора в блоке б ввода неисправностей осуществляются необходимые пере-ключения для проверки контролируемого узла .9 на очередную неисправность.

После прохождения всего списка неисправностей с выхода блока б ввода неисправностей на вход блока 8 управления поступает сигнал Конец работы, по которому устанавливается в О триггер 26, снимается разрешение на входе элемента 28 И, что приводит к останову работы устройства.

Переключатель Режим определяет режим работы устройства: контроль или составление диагностического словаря.

Устройство может использоваться как для контроля ди 1| ретных логических блоков, так и для автоматического составления диагностических словарей.,

При контроле устройство обеспечивает лолучеиие номеров тестов и номеров внешних контактов, на которых проявляется неисправность. Этой инфЬрМации достаточно, чтобы по; имекмйемуск диагностическому словарю локализовать неийЛравность.

Составление диагностичёского словаря с по1 «эщью предлагаемого, устройства требует. 1-2 ч и определяется толькб скоростью работы блока печати.

KoHtu, fttbemu

Bui HeucfiftffSHOcint/

гг

I g

nerna Ь

. Ктямп k Рккум

зг оj-

а Яиагнйстика

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровых модулей и проверки качества тестов | 1974 |

|

SU519713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-06-19—Подача